CCU25 Communication and Control Unit ASIC in CMOS 0.25 μm Ch.Paillard

-

Upload

suzan-lambert -

Category

Documents

-

view

227 -

download

0

description

Transcript of CCU25 Communication and Control Unit ASIC in CMOS 0.25 μm Ch.Paillard

LECC 2002COLMAR

Ch.Paillard CERN EP 1

CCU25

Communication and

Control Unit

ASIC in CMOS 0.25 μmCh.Paillard

LECC 2002COLMAR

Ch.Paillard CERN EP 2

SUMMARY

• CMS tracker slow control• Network architecture and redundancy• Messages structure• CCU25 Bloc diagram• Detail of Blocs I2C, parallel, memory, jtag, trigger• Radiation hardness and irradiation test• Conclusions

LECC 2002COLMAR

Ch.Paillard CERN EP 3

Tracker slow controlAPVs

CLK - T1

CCU

DCU

Det

PLL-Delay

A/DMemory

TTCrx

I2C

FED

FEC

IV

TTCrx

PCIIntfc

CLK

& T

1

A/D

Temp

Front-endModule

CCUM

FEC ctrl

DataPathControlPath

toDAQ

LVDSMUX

LVDSBUF

LD

In control roomOn detector

LECC 2002COLMAR

Ch.Paillard CERN EP 4

RING

ApplicationASICs

CCU

ApplicationASICs

CCU

ApplicationASICs

CCU

FEC

Internal protocol

User accessible protocol:I2C, Memory, Parallel, JTAG

Trigger

LECC 2002COLMAR

Ch.Paillard CERN EP 5

Network architecture

• Ring protocol (Token-Ring)– FEC-CCU (Front End Controller)– CCU-CCU

– Message-based

– Broadcast– Write = post– Read request

• Request packet

• Channel protocol– CCU-Channels

• I2C, Jtag, Memory• Parallel

– Data part– Channel specific– Asynchronous– concurrent

LECC 2002COLMAR

Ch.Paillard CERN EP 6

Messages format

SOF Destination Source Length Data CRC-16 EOF

CH# TR# Channel Specific command

SOF EOF TOKEN

CH# TR# CMD ADDR Data I2C write

LECC 2002COLMAR

Ch.Paillard CERN EP 7

FUNCTIONS of CCU

• Communication– Link between CCU & FEC– Token Ring network

• 2 line data and clock • Data line NRZI

– Timing transport• In clock line

– 7-bit address => 127 ccu in ring

• Control– Link between CCU & F-E

chips– Several protocol

• 16 I2C master• 1 JTAG master• 1 memory• 4 parallel interfaces

LECC 2002COLMAR

Ch.Paillard CERN EP 8

CCU25 Block diagram

I2C Master

I2C Master

LinkController

Node Controller

SCLSDATA

D[0:7] A[0:15] R/W CS[1-2]*

DO(A)

CLKI(A)

Local Bus

DI(A)

DO(B)

DI(B)

Clock Distribution CLKI(B)

CLKO(A)

CLKO(B)

ST1ST2ST3ST4

TriggerDecoder

Trigger Counter& other timing logic

16 x

I2C

Bus

es

Parallel interface

Memory BusInterface

PA[0:7] PB[0:7] PC[0:7] PD[0:7]

Ext Reset*

JTAGMaster

JTAGSlave

Reset*

Alarms

Interrupts[0-3]*

LECC 2002COLMAR

Ch.Paillard CERN EP 9

Node Controller

• Control network & channels– Control Register (5)

• Select net Input A-B • Select Output A-B• Enable channels• Reset channel• Alarm• External reset out

Status register (6)• Illegal sequence • Crc error• Invalid command• I2C busy• Parity error counter• Transaction number

LECC 2002COLMAR

Ch.Paillard CERN EP 10

I2C Interface

• 2 wires clock, data• Read-write

– 7-bit addr, 8-bit data– 10-bit addr, 8-bit data– APV6 mode

• Read-mod-Write– and, or, xor

• Status registers– Detection of line data low– Invalid command– Transaction last succ.– Transaction last bad– Last command

• Control register– Clock freq. 100,200,400,1000 Khz– Write acknowledgement or not– mask

LECC 2002COLMAR

Ch.Paillard CERN EP 11

Memory Interface

• 16-bit addr., 8-bit data• 2 windows pre-decoded• Block transfer• Read mod. write

– and, or, xor

• Status registers– Inv. Command– Inv. Address

• Control registers– Length chip select– Windows 1 & 2– Enable w1 et w2

LECC 2002COLMAR

Ch.Paillard CERN EP 12

Parallel Interface

• 8-bit bi-dir– Each bit individually

• Input strobe– Tr ou level– interrupt

• Output strobe– 100ns,200ns,400ns,1μs

• Status registers– Interrupt– Inv. Command

• Control registers– Strobe 100,200,500,1000 ns– Enable interrupt

LECC 2002COLMAR

Ch.Paillard CERN EP 13

JTAG MASTER

• Simplified JTAG master– TCK, TMS, TDO out, TDI in

• No command structure• Need special ring packet• Example of data part message

TMS[11:8] TDO[11:8] TMS[7:4] TDO[7:4] TMS[3:0] TDO[3:0]

LECC 2002COLMAR

Ch.Paillard CERN EP 14

Trigger

• Distribution of ST1-ST4• ST1- ST4 output can be delayed (1-16) clock period• 4 Counters 32-bit• 2 LVDS input T1 and Clock

CLKT1CLK+T1

~ 25 ns

LECC 2002COLMAR

Ch.Paillard CERN EP 15

Redundancy

CCUM-1

LVDS/CMOS

CC

U

Primary

Secondary

CC

U

CC

U

CC

U

LVDS/CMOS LVDS/CMOS LVDS/CMOS

CCUM-2 CCUM-3 CCUM-4

B

A

B

A

LECC 2002COLMAR

Ch.Paillard CERN EP 16

Radiation–Hardness and irradiation

• For total dose tolerance– Library of standard cells rad-tolerant 0.25 μm CMOS

• For SEU robustness– One-hot type state machine– Node controller 3 blocks + majority voting – Parity on all registers

• Error counter

• Irradiation:– Test at PSI 300 MeV proton beam 3x108 p/s– 4.5 SEU/chip/hour => LHC 4.21x10-2 SEU/chip/hour

LECC 2002COLMAR

Ch.Paillard CERN EP 17

CCU_M

photo

CCU

Data In-Port A

Data In-Port B Data Out-Port B

Data Out-Port A

Clk In-Port A

Clk In-Port B

ClkIn_A ClkOut_A

DIn_A DOut_A

PLL_Clk

DOut_B

ClkOut_BClkIn_B

DIn_B

PLLCKSEL

LVDSMUX

LECC 2002COLMAR

Ch.Paillard CERN EP 18

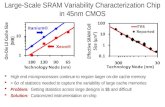

CCU25 layout

• Synthesis from HDL• Features

– 6x6 mm2, 3 metals– 196 pin fpBGA array 14x14 with 1mm pitch– 250 mW @ 2.5v

LECC 2002COLMAR

Ch.Paillard CERN EP 19

CONCLUSIONS

• Network interface (Like Token Ring) 40 Mb/s• Control interface

– I2C, parallel, memory bus and JTAG.• Radiation resistant

![Power Efficient CMOS Full Adders with Reduced Transistor Count · The TGA full adder [5] using 20 transistors is based on CMOS transmission gates and CMOS inverters. It ... In TFA](https://static.fdocument.org/doc/165x107/5c01a10709d3f20f068d0c17/power-efficient-cmos-full-adders-with-reduced-transistor-count-the-tga-full.jpg)

![Adaptive CMOS Circuits for 4G Wireless Networksdigital.csic.es/bitstream/10261/3754/1/ECCTD07_TutorialJrosa.pdf · Adaptive CMOS Circuits for 4G Wireless Networks ... [UMTS/WCDMA]](https://static.fdocument.org/doc/165x107/5ae0f6c27f8b9af05b8e5633/adaptive-cmos-circuits-for-4g-wireless-cmos-circuits-for-4g-wireless-networks-.jpg)