Lecture 19: Timers and Digital Interfacing

description

Transcript of Lecture 19: Timers and Digital Interfacing

Lecture 19: Timers and Digital Interfacing

Lecturers:Professor John Devlin

Mr Robert Ross

Επισκόπηση

• Εισαγωγή στους χρονιστές (Timers)

• Υλοποίηση Timer

• Διασύνδεση Ψηφιακής Λογικής-Digital Logic interfacing

Για επιπρόσθετη ανάγνωση

• http://www.interfacebus.com/voltage_threshold.html• http://www.planetanalog.com/features/signal/showArticle.jhtml?articl

eID=51201009

Εισαγωγή στους Timers• Ο MSP430 έχει έναν 16-bit hardware timer• Ο timer απαριθμεί ανεξάρτητα από την CPU – δεν απαιτεί πόρους

της CPU για την λειτουργία του. • Οι καταχωρητές σύγκρισης-Comparison registers (TAACR0 και

TAACR1) επιτρέπουν την παραγωγή διακοπών-interrupts όταν επαληθεύονται συγκεκριμένες συνθήκες για τον timer

• Η πηγή ρολογιού του timer μπορεί να ελεγχθεί για να είναι συμβατή με συγκεκριμένες προδιαγρφές

• Τρόποι λειτουργίας:– Πάνω-Up: Επαναλαμβανόμενη απαρίθμηση από 0 έως TAACR0– Συνεχής-Continuous: Επαναλαμβανόμενη απαρίθμηση από 0 έως

FFFF– Πάνω-Κάτω-Up/Down: Επαναλαμβανόμενη απαρίθμηση από 0 έως

TAACR0 και έπειτα πίσω προς το 0

Χρησιμοποιώντας τον timer

• Για την χρήση του timer:– Σταμάτημα του timer (θέτοντας MCx στο 0 – ο mode 0

ισοδυναμεί με σταμάτημα)– Καθορισμός των καταχωρητών σύγκρισης-

comparison registers– Καθορισμός των διαιρετών της πηγής ρολογιού για

την επίτευξη του επιθυμητού χρονικού διαστήματος– Επιλογή του τρόπου (MCx):

• Up • Continuous• Up/Down

– Έναρξη Timer

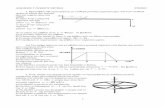

Timer Registers

Timer – Up Mode• Χρήση για ακριβή χρονισμό μιας

συγκεκριμένης περιόδου• Η περίοδος καθορίζεται από TACCR0 + 1

περιόδους του ρολογιού • Μια διακοπή-Interrupt παράγεται με την

αλλαγή του timer από TACCR0 to 0

Timer – Continuous Mode

• Απαρίθμηση από 0 έως FFFF

• Μια διακοπή-Interrupt παράγεται με την αλλαγή του timer από FFFF σε 0

Timer – Up/Down Mode

• Ο Timer απαριθμεί από 0 έως TACCR0 και πάλι πίσω στο μηδέν

• Η περίοδος είναι 2 x TACCR0 περίοδοι του ρολογιού

• Παραγωγή Interrupt όταν η απαρίθμηση φτάσει στοTACCR0 και στο 0

Timer – Παράδειγμα Servo

• A timer was used in lecture 16 to generate a PWM signal to make a DAC

• Remote control aircraft (and some robotics) are operated using servos

• Servos are controlled using a PWM signal– Period: 20ms– On time: 1.25 to 1.75ms– On time sets the position of the servo arm

Timer – Servo Example

MSP430F2013 5V

P1.2

Timer – Servo Example

• Use up/down mode• Period = 20ms• Use clock: 1MHz (Calibrated)• Servo position stepped slowly from left to right

and immediately moved back to right (software controlled)

• Code on web: MDD_Servo.s43

Timer – Servo ExampleSetupP1

BIS.B #0x0f,&P1DIR ; Set P1.0-P1.7 as outputs BIS.B #00010100b,&P1SEL ; P1.2 and P1.4 TA/SMCLK options

SetupP2 BIS.B #11000000b,&P2DIR ; Set P2.6 and P2.7 as outputs

Set_clock ; Set to calibrated 1MHz Clock MOV.B &CALBC1_1MHZ,&BCSCTL1 ; Set range; DCO = 1 MHz MOV.B &CALDCO_1MHZ,&DCOCTL ; Set DCO step + modulation

setup_timer MOV.W #02710h,&TACCR0 ; CCR0 = PWM Period/2, Period = 20ms MOV.W #023A5h,&TACCR1 ; CCR1 = PWM_OFF_Time/2 = 1.5ms

; Range: 18.25ms -> 18.75ms (off) = ; 23A5h -> 249Fh

MOV.W #00C0h,&TACCTL1 ; Output=Toggle/Set MOV.W #0230h, &TACTL ; CLK = SMCLK(1MHz), MODE =

; UP/DOWN

Timer – Servo Examplereset_position

MOV.W #023A5h, R5 ; Fully left positionreset_countdown MOV.W #0F00h, R4 ; Initialise countdownmain DEC R4 ; Decrement countdown JNZ main ; If countdown != 0, loop INC R5 ; Increment the servo position CMP #0249Fh, R5 ; Does servo position = fully right?

JEQ reset_position ; If servo position = fully right, jump MOV.W R5,&TACCR1 ; Load servo position into register JMP reset_countdown ; Loop again

Digital Logic Interfacing

• In digital electronics, when we refer to ‘high’ or ‘low’ what do we really mean?

• This depends on the logic family, low is often 0V, but high could be 3V, 3.3V, 5V or something different altogether

Digital Logic Interfacing

Graphic: http://www.interfacebus.com/voltage_threshold.html

Digital Logic Interfacing

• How can we interface between logic families?

• Use specialised IC (eg. TI TXB0104) or• Higher voltage -> Lower Voltage

– Voltage Divider– Open Drain buffer

• Lower Voltage -> Higher Voltage– Open Drain buffer– TTL-CMOS (Pull Up Resistor)

Voltage Divider

• When going from a higher voltage to a lower voltage a simple resistor voltage divider may be used

5V device

output

3.3V deviceinput

5.1K

10K

)21

1(12

RR

RVV

TTL-CMOS (Pull Up Resistor)

• TTL outputs 2.4V to 3.3V for a high level

• CMOS required 3.7 for high level.

• Use a 1K or 2K resistor pulled up to Vcc

• Increases output voltage from the TTL driver

TTL

output

CMOSinput

2K

Vcc

Open Drain buffer

• Can be used to step up or down

• When not being driven the Open-collector output would float

• Rpullup, ensures that rather than floating it is pulled up the required voltage

Summary

• Hardware timers can be used to accurately time and trigger events

• Digital logic devices often have different definitions of ‘High’ and ‘Low’ voltages

• If ‘High’ and ‘Low’ voltages don’t match interfacing circuitry may be required to connect devices