[IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran...

Transcript of [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran...

![Page 1: [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran (2012.05.15-2012.05.17)] 20th Iranian Conference on Electrical Engineering (ICEE2012) - Efficient](https://reader031.fdocument.org/reader031/viewer/2022020609/575082441a28abf34f983e54/html5/thumbnails/1.jpg)

20th Iranian Conference on Electrical Engineering, (ICEE2012), May 15-17,2012, Tehran, Iran

Efficient Decimation Filters for L� ADCs, Using New

FIR Filters Involving Shifts and Only Two Additions

Mahdi Mottaghi-Kashtiban

Microelectronics lab Shahid Beheshti University

Tehran, Iran m _ [email protected]

Abstract-A new class of digital FIR filters with application to the

decimation filter design for �A Analog to Digital Converters

(ADCs) is introduced, which can be realized using an efficient

multiplier-less structure. The filter coefficients are conditioned in

such a way that, independent of the order, the realization

structure comprises shifts (delays) and only two additions; hence

the proposed filters have close relation to the first order

Cascaded Integrator-Comb (CIC) filters, but offering more

design parameters to overcome their limited degree of freedom.

A filter Involving Shifts and Only Two Additions (abbreviated as

ISOTA), has coefficients dependant to each other; this together

with the non-linearity of the discrete-space of the coefficients,

makes the design procedure somewhat limited. A simple design

method is used to find the desired solutions, based on applying

gradient search algorithm to the possible combinations of the

coefficients (obtained by state tree diagram). Demonstrative

examples as well as the practical application are presented.

Keywords-decimation filter; FIR; multiplier-less; sigma-delta ADC

I. INTRODUCTION

Digital Finite Impulse Response (FIR) filters are widely used in signal processing mainly because of inherent stability and linear phase response. In contrast, Infmite Impulse Response (IIR) filters have instability problems and generally non-linear phase response [ 1]. The most important advantage of IIR filters over F[R counterparts is the ease and efficiency of hardware realization: Neglecting the phase non-linearity, IIR filters can achieve the desired frequency response specifications with an order much less than FIR filters. Reduced order of IIR filters generally results in less hardware requirements such as delay elements (shift registers), memory for storing the coefficients, and multipliers and adders to perform the arithmetic operations.

Due to the advantages of F[R filters, many researches are performed to overcome the computational complexity and hardware cost of this class of filters. The major cost of a filter is due to the multiplications of taps inputs by the coefficients, which in general involve many shifts and additions (known as Multiplier block Additions. MBA). Also the final output is achieved by applying a summation on all multiplication results; this involves a number of additions proportional to the filter order (known as Structural Additions. SA). Since the shifts can

978- 1-4673- 1 148-9/ 12/$31.00 ©20 12 IEEE 249

Ali Jalali

Electrical and Computer Engineering Faculty Shahid Beheshti University

Tehran, Iran a [email protected]

be easily hard-wired, the major concern in the cost of a digital filter is the number of required additions. Many efforts are performed on reducing the computational complexity of the filters, leading to the "multiplier-less realizations" which need limited number of additions. The filter with mostly reduced additions is the Cascaded Integrator-Comb (C[C) filter proposed in [2]. An Nh-order CIC filter is the cascade of N rectangular windows:

[ 1 D-I -k l

N [ [ l_z-D jN

HClc{Z) = D �Z =

D [-z-I ( 1)

D (the length of windows) is preferred to be a power of two to avoid the need for Division. Although the filter is FIR with only zeros appeared inside L in ([), its recursive realization is more efficient as it requires N additions for the integrators (l_z-l)N, and N subtractions for the comb filters (l-z-D)N. Since hardware requirements for additions and subtractions are approximately the same, the filter needs a total of 2N additions. Three important disadvantages of C[C filters are the low stopband attenuation, relatively high droop in pass-band gain, and limited number of design parameters. The first problem is resolved by increasing the filter order N, but this leads to more droop of the pass-band gain; hence a compensating filter is used to eliminate the second problem. However the third problem remains unsolved.

Another efficient class of filters, known as half-band filters, is very useful in decimation applications and multi-rate filterbank designs [3]. Interestingly, about half of the filter coefficients are zero, which enables us to avoid approximately 50% of multiplications. Of course it is obvious that these filters have also limited design parameters because of their special frequency response.

For general specifications, a number of techniques are used to design multiplier-less FIR filters which can be classified into two categories: optimization of the filter coefficients over a discrete space, and multiplier block adder reduction. Discrete coefficient optimization techniques are based on finding a filter such that the desired specifications are met, while its coefficients are represented by sum of a minimum number of signed powers-of-two (MNSPT), for example by canonic signed digit (CSD) representation. The Mixed Integer Linear

![Page 2: [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran (2012.05.15-2012.05.17)] 20th Iranian Conference on Electrical Engineering (ICEE2012) - Efficient](https://reader031.fdocument.org/reader031/viewer/2022020609/575082441a28abf34f983e54/html5/thumbnails/2.jpg)

Programming (M[LP) algorithm [4,S] finds the optimum solution, but is restricted to low order filters. Some sub-optimal techniques have been proposed including random local search [6], simulated annealing [7], genetic algorithm [8], and trellis search [9]. Also a simple coefficient rounding has been reported [ 10]. On the other hand the algorithms working on multiplier block adder reduction, apply various methods to extract Common Sub-expressions in whole multiplications to perform the same computations only once; this is called Common Sub-expression Elimination (CSE) [ 1 1- 14]. Also FIR filter structures based on Reconfigurable Multiplier Blocks (ReMB) have been proposed which use time domain multiplexing of MBAs to avoid unnecessary computations, and hence reduce the overall power consumption [IS].

Except for the C[C filters, all abovementioned structures usually involve much more than two additions to perform a filtering operation. For on-line applications such as decimation filters of LL1 ADCs, which high speed of processing is in demand, it is desirable to reduce the required operations as much as possible. The paper shows that for unipolar input data (always positive or always negative, as in the case of the LL1 modulator bit-stream), a new class of F[R filters [SOTA can be used to decrease the computational complexity and hardware cost. The novelty of the proposed filters is that the required number of additions is reduced to only two Gust like the first order C[C filter), while the coefficients are not fixed at I so that the problem of limited design parameters is considerably resolved; also the high pass-band gain droop can be neglected, which in turn eliminates the need for a compensating filter.

Section II describes the main idea for the proposed class of the digital filters through demonstrative examples, followed by general formulization presenting the necessary conditions and the detailed discussions on some important points. Section III explains a derivative based design algorithm, and as a practical application in section IV, a filter ISOTA is used to design the decimation filter for a 6-bit LL1 ADC with I-bit quantization; finally section V concludes the paper.

[I. DIGITAL F[R FILTERS [SOTA To explain the main idea of the paper, subsection A begins

with demonstrative examples of low and high-pass filters applied on I-bit and 2-bit input binary data, and describes the necessary conditions on the coefficients and the corresponding filter specifications; next in subsection B, the results are generalized and the formulization process for designing the filters [SOT A is presented.

A. Demonstrative Examples Let x be a bit-stream of zeros and ones, for example the

output of a LL1 modulator with I-bit quantization. Assume this data is to be processed with a low-pass filter to result in a 6-bits unsigned data y. The conventional method is to design the desired filter in MATLAB, and then use one of the abovementioned algorithms to optimize the coefficients for minimum signed power of two representations andlor share the common sub-expressions. In general, as the filter order increases, the required number of additions increases too. Here a new class of filters is discussed which independent of the order, require only two additions.

2S0

·20 III "0 ;:l .., .... <: ·40 Ol �

·60 -l--��"'--���_..J...-��---L�--1 o �------------------------,

';:: " .... -g ·4 "

-12+--��-���-�_�_�--I o 0.2 0.4 0.6 O.B

Normalized Frequency (<0>/1<)

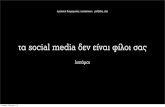

Figure l. Magnitude and phase response oUilter hj.

For now, consider a system described as: 12

y [ n] = Lhdk]x [ n-k]' k=O

_ _ (2) (7) (2) hi -[ 1,3,3,7,7,7,7,7,7,7,3,3, 1] - [1,3 ,7 ,3 , 1] .

hi is the system impulse response shown in vector form; for simplicity, the number of equal sequential coefficients is denoted by a super-script number in the parenthesis; if there is no such a super-script number (here, on the first and last coefficients), then the corresponding coefficient is not repeated. This FIR filter has the low-pass frequency response depicted in fig. I. The pass-band frequency for ±O.SLSB (±0.068dB) error is 0.027r, and the stop-band frequency is 0.27r with 21dB attenuation. The filter gain (sum of coefficients) is 63, its order is M= 12, and the coefficients are symmetric about the modal point, hl [ M12] , resulting in a generalized linear phase response [ 1]. Since the input bit-stream and the filter coefficients are all positive, the output value will be maximum when all input samples are 1; i.e. Ymax equals the filter gain, and y E [ 0, 63] . As a result y can be directly represented by 6-bits, eliminating the need for rounding.

Now we consider the filter coefficients to gain a sight about the performance of the filters ISOTA. Importantly note that the first and last coefficients are power of 2, and the differences between two sequential coefficients are either zero or a power of 2; if a difference is not zero, we denote it as a transition point. A non-zero difference is uniquely applied between two coefficients; but the difference zero can be infinitely occurred. Of course, as we will explain in the next subsection, the nonzero differences can be sum of signed powers of 2. Note that the first and last coefficients, because of having non-zero values, always contribute to the first and last transition points.

Initially the input and output of the filter are zero. Now assume a 1 enters the filter at time 0 (x[O] =I); then the previous filter output is incremented by the first coefficient (i.e. by 1); if the next input sample is also 1 (x[ 1 ]= 1), then the output will be the previous output incremented by 3 units: 1 because of entering the new sample, and 2 because of passing the previous

![Page 3: [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran (2012.05.15-2012.05.17)] 20th Iranian Conference on Electrical Engineering (ICEE2012) - Efficient](https://reader031.fdocument.org/reader031/viewer/2022020609/575082441a28abf34f983e54/html5/thumbnails/3.jpg)

I I I L __ -. .- ____ -'

I I I I I I r-�""'" I I I I I

'--:i-'-;:-''---' : : I I I L ___ ...I I

� _______ J

L. ________ -.

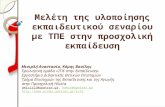

Figure 2. Block diagram for realizing filter hj.

I I I l I , I

sample through a transition point (increasing the coefficient from 1 to 3). In general, if an input sample which is 1 passes through a transition point with increasing value, then the output will be incremented by the difference of those two coefficients. Tn the same way if the transition point is a decreasing one, then the output will be decremented by the corresponding difference. Finally if a sample does not pass through a transition point, for example when shifting from hi [1] to hi [2] or from hJ[3] to hJ[4], then the output is not affected through this sample. This process can be written in the following recursive form:

y [ n] = y [ n-l]+x [ n ]+(3 -1)x [ n-l]+(7 -3)x [ n-3] +

(3 -7)x [ n -10] + (l-3)x[n -12] -x[n-13].

The last subtractive term is because of exiting the oldest sample of the input from summation. Reordering the above formula, we can write

y [ n] = y [ n -1] + 4x [ n -3] + 2x [ n -1] + x [ n]

-4x [ n-lO] -2x [ n-12]-x [ n-13].

Now interestingly note that, the right hand of this equation can be written as

y [ n] = y [ n -1] + Ax -Sx (2)

where Ax (abbreviation to Additive x) and Sx (Subtractive x) are 3-bit numbers added to, and subtracted from y[ n- l]:

Ax: Binary

Sx: Binary

Since the subtraction and addition require almost the same hardware, then the filter requires only two additions. Fig. 2 depicts the block diagram for realizing this filter. The delay elements used for the input are I-bit length, and that for the output is 6-bits length. The shifted samples are simply hardwired to the adder blocks.

As it can be easily inferred, the input x can not be a signed data, because its random sign may corrupt Ax and Sx. For example if all input samples are positive except for x[ n], then it contributes as a subtractive term like x[ n-13]. Tn contrast, there is no limit on the filter coefficients to be whether signed or unsigned numbers, though they are unsigned for this example; the reason is that the filter coefficients are deterministically fixed, unlike the input random data, and hence it is certainly determined that a particular input sample appears whether as an additive or subtractive term.

251

i or-------��==�

0.2 0.4 0.5 0.8 No<malized F<equency (0!n)

(a)

(b)

Figure 3. (a) Magnitude response, and (b) realization of filter h2.

The coefficients differences at the transition points can not be equal; otherwise certain bites) in Ax or Sx are not determined by single input samples. For example, in a filter with coefficients h=[4,2,6,7,6,2,4] the differences -2,-1,1 and 2 have occurred only once, but the difference 4 is repeated twice: once for the first coefficient, and once between h[ 1] and h[2]. In the same way the difference -4 is repeated twice: once for transition point between h[4] and h[5], and once for the last transition point. Hence the MSB of Ax (or Sx) for this filter is determined by addition of x[n] and x[n-2] (or x[n-5] and x[n-7]), and consequently it is not a filter ISOTA.

Clearly, if the input is a 2-bit unipolar data, then the difference between sequential coefficients must be zero or (sum of) signed powers of 22=4; as a result, the first and last coefficients are (sum of) powers of 4. This can be inferred from the form of Ax and Sx: each input sample passing a transition point determines (at least) two bits in Ax or Sx, and therefore the other sample must be shifted (at least) twice to only affect other two bits.

As the second demonstrative example, consider filter h2=[I,-3,-19,45,-19,-3,1], which is applied to a 2-bit data. The filter coefficients are signed numbers with differences ±4°, ±41, ±42 and ±43• The sum of positive coefficients is 47, and that of negatives is -44. Since the maximum value of the input samples is binary 11 (decimal 3), the filter output can take a value in the interval [-44*3,47*3]=[-132,141]; hence h2 is a filter TSOT A working on 2-bit input data, and resulting in 9-bit (including sign) output data. In contrast with the previous example, here the output result can not reach its full range [-256,255]; however in both examples if a rounding to less number of bits is required, then a round off noise does exist.

Fig. 3(a) shows the high-pass frequency response of h2, and fig. 3(b) depicts its realization. The delay elements used for the input are 2-bits length, and that for the output is 9-bits length. The MSBs of Ax and Sx are the MSBs of x[n-3] and x[n-4], respectively; their LSBs are the LSBs of x[n] and x[n-7], respectively.

![Page 4: [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran (2012.05.15-2012.05.17)] 20th Iranian Conference on Electrical Engineering (ICEE2012) - Efficient](https://reader031.fdocument.org/reader031/viewer/2022020609/575082441a28abf34f983e54/html5/thumbnails/4.jpg)

h(-J)

h(O)-h(2nd TP -1) h(2nd TP) --

h(3l'd TP) heM) h(M+J) --

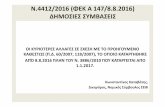

_ _ . B Figure 4_ State tree diagram of filter coetlicients for U ={ ±l,±2 Tn) with the constraint of positive first coetlicient, and eliminating the paths

with single non-zero coefficient; nodes (circles) are the filter coefficients, and the numbers on the branches are their differences at the transition points (TP)_

B. General Formulization Assume that the filter order is M (its length is M+ I), hence

the coefficients denoted as h[k] can be non-zero for k=0,00 . ,M. To simplifY the formulization, we also consider the zero-value coefficients before the first and after the last coefficients:

h[k], k =-I, O, I, o o ., M+I; h[-I] = h[M+I] = 0 .

The filter input is a B;n-bit data, and the output result is desired to be a Bou,-bit data. The filter coefficients may be both positive and negative, but the input is unipolar. If input is always negative, like 2's complement, then the samples can not be directly shifted and concatenated to form Ax and Sx in (2); a solution is to convert the samples into positive numbers and negate the filter coefficients.

Define the differences between filter coefficients as:

d [ j] = h [j]-h[j -1], j = 0,00 . , M + 1 .

Also define the set of signed powers of 2BIII as:

(3)

(4)

The conditions applied on the coefficients to design a filter ISOTA are stated as follows:

A filter can be realized using the structure ISOTA, if the input data is unipolar, and the non-zero coefficients differences defined in (3) are (sum oj) elements o{the set U defined in (4), in such a way that each element can be used only once.

Some noticeable points can be derived from the mentioned conditions. First, the unique use of each element of U implies that the coefficients differences never will be equal, though the coefficients may be; in fact, the possibility of equal coefficients helps in designing linear phase FIR filters. To describe this, as the second point consider (3) where we have d[O]=h[O] and d[ M+ I ]=-h(M); hence according to the first point, h[O]=t'=-h(M). In the other words the first and last coefficients can not be antisymmetric, and thus it is impossible for linear phase FIR filters of types III and IV (anti-symmetric impulse response with even and odd M, respectively [I]) to be realized using structure ISOT A. Of course the FIR filters of types I and II (symmetric impulse response with even and odd M, respectively) can be realized by this structure, since the symmetry of coefficients

252

requires a possible condition of h[O]=h[M], or more generally

h[k]=h[ M-k]. Third, note that if a particular difference 2m;BIII is

applied for a transition point, then the difference _2mlBIII must also be applied for another transition point (and vice versa), otherwise it is impossible for the last coefficient to be the sum

of signed powers of 2B

;fI ; the reason is that the sum of different signed powers of 2

B;n will not be equal. Forth, the conditions

do not force the designer to apply all signed powers of 2B

;n up to the maximum power, pB;n; for instance one can apply the

differences ±20B;n = ±1 together with ±23B;n , skipping the use

of differences ±2IB

;n and ±22B

;n . The fifth point is about the relationship between the filters ISOTA and the CIC filters: ignoring the constant gain of M+ 1, a first order CIC filter (with N=I in (I)) is a filter ISOTA with only two applied differences

of U = {± I} between the coefficients; the constant gain does

not change the normalized frequency response.

As the fmal point, note that the terms Ax and Sx have equal number of bits which is determined by Bin together with the number of transition points. On the other hand the filter order directly determines the number of delay elements used to store the taps inputs, and also affects the number of bits in the output result; therefore the filter order is important since it has an influence on the "addition depth" for two additions in (2). If the

sum of negative coefficients multiplied by 2B

;n12

is less than

2Bolll12

in magnitude, and the sum of positive coefficients

multiplied by 2BIII12 -I is less than 2

BolI/12 -I , then there is

no round off or truncation noise; of course this is not usually satisfied, and the results of two additions need to be rounded to Bout bits.

Fig. 4 shows the state tree diagram of the coefficients for

U = {±I,±2B;fI} ; of course the first coefficients are constrained

to be positive, and the paths with single non-zero coefficient are not shown since they have the same normalized frequency response as the first order CIC filter. The coefficients are placed in circles (nodes), and their differences at the transition points are assigned to the branches. The state tree grows very sharply as the number of elements of U is increased. The problem of finding a filter with desired specifications is discussed next, where the goal is to find the optimum number of repetitions for each coefficient in a candidate path.

![Page 5: [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran (2012.05.15-2012.05.17)] 20th Iranian Conference on Electrical Engineering (ICEE2012) - Efficient](https://reader031.fdocument.org/reader031/viewer/2022020609/575082441a28abf34f983e54/html5/thumbnails/5.jpg)

III. DESIGN ALGORITHM

Since the coefficients are not independent of each other, and also belong to a highly nonlinear discrete space (sum of

signed powers of 2BlfI ), their optimization becomes somewhat

limited. In this paper a simple gradient search algorithm is used, of course with slight modifications to change its inherent continuous nature and make it suitable for this discrete optimization, and also help in skipping local optimums. The cost of these improvements is the increased search time.

First, depending on the application an appropriate error function is defmed using the frequency responses of the desired

(HlJ) and designed ( H ) filters:

Error = G(H D, H) (5)

The state of the gradient search algorithm (to be optimized) is the number of repetitions of coefficients between sequential transition points; the set of coefficients is obtained using state tree diagram (discussed next). The derivative of Error with respect to each number of coefficients is computed numerically with step-sizes of both -I and I; the reason to do so is that the Error function is highly non-linear, and the derivative with increasing step-size may be far different than that of decreasing one. The first modification is that only the coefficient is updated (by the value of step-size) which offers the maximum Error improvement, and not the whole coefficients as in the conventional gradient search; this is because of high nonlinearity of Error function. This process continues until we reach to a local optimum which the step-sizes ± I do not lead to Error improvement; then the second modification is made to skip this local trap by increasing step-sizes to ±2. If the Error is decreased, the state will be updated and the step size will be returned to ± I for fine tuning; if not, the step size will be increased again by ± 1 units until an improvement occurs, or the algorithm reaches a pre-determined limit of the filter order.

Since the state tree diagram grows sharply as the number of transition points increases, the set U is firstly defined to have

few elements as U = {± 1, ±2 B

in} ; the gradient search is applied

to all set of coefficients (paths in fig. 4) to find the optimal numbers of coefficients minimizing the Error. The first coefficients are always set positive because the filters h and -h have the same frequency responses except for a constant phase shift of ISO degrees; this is not an important problem and if required, the final optimized filter can be negated to achieve the desired phase response. If the specifications are not met, the

optimization proceeds to U = {±I,±2Bln ,±2

2Bln} ; here there is

no need to check all possible set of coefficients, and we can use the best filter in the previous optimization to estimate the candidate set of coefficients for the desired filter. The optimization continues until the Error becomes zero. Note that if a generalized linear phase filter is required, the symmetry of coefficients decreases the design algorithm computations since we are concerned with the coefficients up to h[MI2].

IV. ApPLICATION EXAMPLE

In L� ADCs, the decimation filters are used to convert lowresolution high-sample-rate bit-stream of the modulator output,

253

into high-resolution low-sample-rate data. Usually an Nth-order CIC filter is used in the first stage of the decimation filter, followed by one or more filters to ensure sufficient stop-band attenuation and also compensating for the gain droop of CIC filter in the pass-band. Here as an application, a decimation filter is designed for a 6-bit L� ADC with first order modulator and I-bit quantization. According to [1], an oversampling ratio of about 16 is required to increase the output resolution by 5 bits. Therefore the pass-band frequency of the overall decimation filter (in the other words, the signal bandwidth) is copms=1I16=0.0625 (with sampling frequency normalized to 2), the decimation factor is considered to be S, and consequently the stop-band frequency is cos/op=I/S=0.125. For 6-bit resolution an SNR of 3SdB is required, hence the stop-band rejection must be better than 3SdB. For specifications almost identical to the proposed filter, a design presented in [16] uses a 5th order CIC filter of length S (with 10 additions) together with the compensating filter requiring 4 additions and an FIR filter of order IS with S integer multiplications (the number of additions for this FIR filter is not reported).

The stop-band attenuations for the first and second order CIC filters are 13dB and 26dB, respectively. To maintain the SNR, we can move to a third order CIC filter with 39dB stopband attenuation, or the filter ISOTA needs to be sharper with high stop-band rejection. To simplify the overall realization, we use the composite of two first order CIC filters with lengths 10 and 16, offering better stop-band rejection near the frequency cos/oP (dashed curve in fig. 5(a)). The price paid for this improvement is five excess delay elements compared to a second order CIC filter of length S, as we can see it from fig. 5(b); but this architecture leads to significant reduction in the compensating filter order. The filter ISOT A is applied to perform additional attenuation in the stop-band, and to compensate for the pass-band gain droop of CIC filters.

To design the filter ISOTA, the Error in (5) is defined based on the overall decimation filter pass-band ripple and stop-band attenuation. The allowed pass-band ripple is set to 0.5 LSB (±0.06SdB), and its excess error is considered as the pass-band error. The Error is the sum of pass-band error and the stop-band peak amplitude. The filter is desired to be symmetric having a linear phase, hence the design algorithm computations is reduced. The resulting type I filter is of order 64 with a negative gain, so the coefficients are multiplied by -1 to make the gain positive. Noting on the symmetry h[k] =h[64-k], the first half coefficients are:

h[O: 32] = [_2(9)

,14(6) ,-IS,-17

(1I) ,47,55

(4) ,51]

The filter has 14 transition points and is applied before the CIC filter, since it is designed for I-bit input bit-stream (the differences between coefficients are powers of 2). Total number of required additions for this design is 6; 4 for CIC filters and 2 for the filter ISOTA. The output of the proposed filter ISOTA is in the range [-223,753], hence requiring 11 bits (including sign bit) for representation. The final result of decimation filter is rounded to 6-bits. The terms Ax and Sx are in fact 7-bit binary numbers in magnitude, but since Sx needs an additional sign bit, the depth of adder which subtracts it from Ax is S bits.

![Page 6: [IEEE 2012 20th Iranian Conference on Electrical Engineering (ICEE) - Tehran, Iran (2012.05.15-2012.05.17)] 20th Iranian Conference on Electrical Engineering (ICEE2012) - Efficient](https://reader031.fdocument.org/reader031/viewer/2022020609/575082441a28abf34f983e54/html5/thumbnails/6.jpg)

OJ "" 2

.� -1 ;;: -1

,........, -20 OJ � '" -40 "" 2 ·�o -60 "

:E -80

0.08 0.04

Pass-band zoom 0

0.02 0.04

0.1 02 03 0.4 0.5 0.6 0.7 N orlllalized Frequency (Ol/n)

0.8

MSB x(n-27) Ax �Y-(n�-5jj) �Y(ij:-ti) �Y-(n�-i8) �Y-Ui�j3) �Y-Ui�-65)

LSB �Y-Ui:-i6)

(a)

(b)

y

(c)

.IX x(n-38) �Y-Ui�B) �Y-C J:j �-56) �Y-Cn�j7) �y-(ii�j2) �YCrr---) �y-(ii�-49)

-14O-I-_��_��---"'_ -. 10 -J 10 -2 -1 0 -4 -J -2 10 10 10 10 10 10 Normalized Frequency Coo/n)

(d)

0.9

-, 10 o 10

Figure 5. (a) Magnitude responses of the filter ISOTA (dotted), composite CIC (dashed) and overall decimation (solid) filters; realization of

(b) composite CIC filter, and (c) filter ISOTA; (d) PSD of the modulator output for -2dBFS input at frequency wp",,!3 stepped by -6dB (left),

and PSD of final ADC output after rounding and down-sampling (right).

Fig. 5(a) also shows the magnitude responses of the filter ISOT A (dotted) and overall decimation filter (solid). The passband gain ripple is ±0.047dB, with stop-band rejection of 39.2dB at w=0.122. For these specifications, the optimal Remez algorithm results in a filter of order 72. Fig. 5(c) is the realization of the filter ISOTA; a total of 65 shifts are required which for compactness the delay elements are not shown. The range of analog input signal is [0,1], and the threshold value for I-bit (binary) quantizer is set to 0.5; therefore input signals are stepped by a DC value of 0.5 (i.e. -6dB) to make them always positive with a full-scale signal amplitude of 0.5.

Fig. 5(d) shows PSD of the modulator output (left plot) for a sinusoidal input at frequency wpass!3 with -2dB of full scale

254

(the number of FFT points is 16384). Also the right plot of this figure is the PSD of final decimated output of ADC, rounded to 6 bits.

V. CONCLUSIONS

The filters ISOT A can be efficiently used to process unipolar data since they require only two additions, and consequently the hardware and power consumption is greatly reduced, while the processing speed is increased. Future works can be directed to fmd efficient methods with minimum pre and post processing to make these filters applicable for signed input data. Also the use of design algorithms with discrete nature can be proposed.

REFERENCES

[1] A V. Oppenheim, R. W. Schafer, with 1. R. Buck, Discrete-Time Signal Processing, New Jersey: Prentice Hall, 2nd ed., 1999, Ch. 5, 6 and 7.

[2] E.B. Hogenauer, "An economical class of digital filters for decimation and interpolation," IEEE Trans. Acoust., Speech, Signal Processing, voL ASSP-29, pp. 155-162, Apr. 1981.

[3] R. E. Crochiere and L. R. Rabiner, Multirate Digital Signal Processing, Englewood Cliffs, NJ: Prentice Hall, 1983.

[4] Y. C. Lim, "Design of discrete-coefficient-value linear phase FIR filters with optimum normalized peak ripple magnitude," IEEE Tran. Circuits Syst., vol. CAS-37, pp. 1480-1486, Dec. 1990.

[5] Y. J. Yu and Y. C. Lim, "Design of linear phase FIR filters in subexpression space using mixed integer linear programming," IEEE Trans. Circuits Syst. I, Reg. Papers, voL 54, pp. 2330-2338, Oct. 2007.

[6] Q. Zhao and Y. Tadokoro, "A simple design of FIR filters with powersof-two coefficients", IEEE Trans. Circuits Syst., vo1.35(5), pp.566-570, 1998.

[7] J. Radecki, J. Konrad and E. Dubois, "Design of multidimensional finite-word length FIR and IIR filters by simulated annealing", IEEE Trans. Circuits Syst. II, voL 42(6), pp. 424-431, 1995.

[8] OJ. Xu and M.L. Daley, "Design of optimal digital filter using a parallel genetic algorithm", IEEE Trans. Circuits Syst. II, voL 42(10), pp. 673-675, 1995.

[9] c.L. Chen and AN. Willson Jr., "A trellis search algorithm for the design of FIR filters with signed-powers-of:two coefficients," IEEE Trans. Circuits Syst. II, voL 46(1), pp. 29-39, 1999.

[10] G. J. Dolecek and S. K. Mitra, "Computationally efficient multiplier-free FIR filter design," Computacion y Sistemas, voLlO(3), pp.251-267, 2007.

[11] R.L Hartley, "Subexpression sharing in filters using canonic signed digit multipliers", IEEE Trans. Circuits Syst. II, vol. 43(10), pp. 677-688, 1996.

[12] M. Martinez-Peiro, £.1. Boemo and L. Wanhammar, "Design of high speed multiplierless filters using a nonrecursive signed common subexpression algorithm", IEEE Trans. Circuits Syst. II, voL 49(3), pp. 196-203, 2002.

[13] F. Xu, C.-H. Chang, and c.-c. Jong, "Contention resolution algorithm for common subexpression elimination in digital filter design", IEEE Trans. Circuits Syst. II, voL 52(10), pp. 695-700, 2005.

[14] A P. Vinod and Edmund M-K. Lai, "On the implementation of efficient channel filters for wideband receivers by optimizing common subexpression elimination methods", IEEE Trans. Computer-Aided Design Integ. Circuits Syst., vol. 24(2), pp.295-304, 2005.

[15] S. S. Demirsoy, 1. Kale and A Dempster, "Reconfigurable multiplier blocks: structures, algorithm and applications," Circuits, Syst. and Signal Processing, vol. 26, pp. 793-827, 2007.

[16] G. 1. Dolecek and V. Dolecek, "Multistage decimation filter," 13th Int. Research/Expert Conf, Trends in the Development of Machinery and Associated Technology, pp. 381-384 , 2009.

![Conference Poster - [email protected]](https://static.fdocument.org/doc/165x107/6203b130da24ad121e4c5b7c/conference-poster-emailprotected.jpg)