Scaling the MOS transistor below 0.1 μm: methodology, device structures, and technology...

Transcript of Scaling the MOS transistor below 0.1 μm: methodology, device structures, and technology...

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 41. NO. 6, JUNE 1994

~

94 1

Scaling the MOS Transistor Below 0.1 pm: Methodology, Device Structures,

and Technology Requirements Claudio Fiegna, Hiroshi Iwai, Senior Member, IEEE, Tetsunori Wada,

Masanobu Saito, Enrico Sangiorgi, and Bruno Riccb, Senior Member, IEEE

Abstract-This work is a systematic investigation of the feasi- bility of MOSFET’s with a gate length below 0.1 pm.

Limits imposed on the scalability of oxide thickness and supply voltage require a new scaling methodology which allows these parameters to be maintained constant. The feasibility of achieving sub-0.1 pm MOSFETs in this way is evaluated through simula- tions of the electrical characteristics of several different device structures and by addressing the most important issues related to the scaling down to ultra-short gate lengths.

This study forms a valuable starting point for the understand- ing of technological requirements for future ULSI.

I. INTRODUCTION HE scaling of silicon MOSFET channel lengths to 0.1 T pm and below is a subject that has recently attracted great

interest. Much work has been done approaching this problem from both the experimental and theoretical points of view [1]-[7]. Fig. 1 illustrates the trend followed scaling the MOS device and reports the most recent achievements. Scaling of the supply voltage (VDD) is necessary to control short channel effects and hot carrier effects. The oxide thickness (tox) has been progressively scaled and the shortest devices fabricated so far, almost reached a 3 nm thickness that is regarded as a lower limitation for Si02 due to the onset of relevant direct tunneling [8].

Several crucial issues must be considered when scaling a MOSFET’s channel length down to the deep submicron regime (a valuable review of this topic can be found, for example, in

I ) The short-channel effects, which cause severe degrada- tion of the subthreshold characteristics and an unac- ceptable dependence of threshold voltage on channel length;

[91).

2) the adjustment of the long-channel threshold voltage; 3) the lower limit on the threshold voltage and supply volt-

age, VDD, imposed by requirements of noise immunity margins;

Manuscript received August 10, 1993. The review of this paper was arranged by Associate Editor Y. Nishi.

C. Fiegna was with ULSI Labs. R&D Center, Toshiba Co., Kawasaki, Japan; he is now with the Istituto di Ingegneria, University of Ferrara, Ferrara, Italy.

H. Iwai, T. Wada, and M. Saito are with ULSI Labs. R&D Center, Toshiba Co., Saiwai-ku, Kawasaki 210, Japan.

E. Sangiorgi was with the University of Bologna; he is now with the Department of Physics, University of Udine, Udine, Italy.

B. Riccb is with DEIS, University of Bologna, Bologna, Italy.

s 1 1 ToshibaSZ

lo-’ 1 OD

Gate length [pm]

Fig. 1. Trend for the scaling of gate oxide thickness and supply voltage.

4) the lower limit on oxide thickness, imposed by direct tunneling which degrades the transistor characteristics;

5 ) the limitations due to hot-carrier effects (HCE), which severely reduce device lifetimes;

6) the limitations resulting from band-to-band tunneling, which leads to an additional degradation of the sub- threshold characteristics;

7) the optimization of intrinsic device performances (high current driving ability);

8) the minimization of parasitic effects such as those due to source-drain series resistances and capacitances asso- ciated to the junctions; and

9) the minimization of process complexity and production cost.

In this work, several device structures are evaluated in view of their use in the fabrication of ultra-short channel devices; all the issues listed above are taken into consideration, with the exception of 8), this one will require extensive future work, as discussed later.

If the requirements and limitations listed in 1)-7) are to be met, a new scaling approach is needed. Conventional scaling, requiring an increase in channel doping and reductions in oxide thickness (tox) and supply voltage (VDD), is expected to become ineffective as the channel length falls below 0.1 pm, because the following severe limitations come into force: 1) Conventional bulk MOSFET’s will require channel doping

approaching or exceeding 10l8 cm-3 in order to limit short-channel effects (SCE). Such high doping concentra- tions are likely to cause severe performance degradations

0018-9383/94$04.00 0 1994 IEEE

942 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 41, NO. 6, JUNE 1994

due to impurity scattering and reduced carrier mobility in the high transverse field. Furthermore, a high doping concentration at the interface causes severe carrier con- finement and thus, quantization of the carriers' energy levels [lo] that, in tum, leads to higher threshold voltage than predicted by classical calculations. The shift due to quantization has been estimated theoretically [ 111 and for doping concentrations of the order of 10l8 cm-3 it is comparable to the low VTH value necessary for reduced VDD operation of sub-0.1 pm MOSFET's. Hence, these effects are likely to prevent adjustment of device's threshold voltage.

2) An additional limit is imposed by 4) above. On the basis of experimental results, the ultimate lower limit for Si02 thickness is expected to be 3 nm 181.

3) The supply voltage reduction needed in conventional scal- ing is limited by noise immunity margins as stated in 3). In this regard, we did not investigate in details on the actual lower limit for the threshold voltage which is dependent on the specific application. For logic applications we expect that VTH = 0.3 V is a lower limit for a subthreshold swing of 80-100 mv/Dec; adopting the empirical criterion

enforced. VTH N ~ / ~ V D D [9], VDD > 1.0 - 1.5 v should be

Thus, realization of sub-0.1 pm MOSFET's requires a new scaling approach that maintains tox and VDD constant for LG < 0.1 pm and which, at the same time, limits the doping concentration in the channel region. Here, we investigate the feasibility of achieving such a methodology. In particular, we look into its application to different MOS structures by device simulations.

Recently, investigations of the lower gate length limitations on conventional bulk silicon MOSFET's [2] and double-gate structures [5] based on the semi-classical models of charge transport have been reported. In this paper, we intend to extend this previous work by reporting on an extensive comparison of different structures in terms of current drivability, short- channel effects and hot-carrier effects. Junction depth and oxide thickness are made smaller than in [2] in order to test the ultimate limitations of MOSFET technology. Our analysis is restricted to a DC characterization, leaving the discussions on the effects of parasitic resistances and capacitances on ac performances of CMOS circuits to a future work. The final aim of this study is to offer an indication as to which is the most promising device structure for achieving sub-0.1 pm gate lengths, and to give some guidelines regarding the requirements for future VLSI.

In this report, the investigated device structures and the methods used in this work will first be described; then the results of comparing simulated electrical characteristics of different structures will be reported with particular emphasis on short-channel effects, threshold adjustment and current drivability. One of the considered structures will be then considered in more detail in view of its good characteristics. The results of hot-carrier characterization will also be reported and the implications of scaling at constant voltage on HCE will be studied on the basis of the simulation results. Finally, we will conclude by discussing the different considered device

TABLE I MAIN DEVICE PARAMETERS

Oxide Thickness (tax) Back ox. thick. ( t b o x )

Epi. thickness (t+, t,i) N (p) depth XJ1 N+ (P) depth X 52

Su 1 volta e (VDD) Ground plane conc. (Ns) 1018cm-3

Conveational

(a) Uniform

(b) Buried

(e) DoubleG

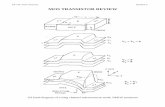

Fig. 2. work.

Schematic cross section of the MOSFET shuctllre.~ studied in this

structures, proposing a new scaling approach at constant VDD and tox, and discussing the main requirements for future sub-0.1 pm technology.

11. DEVICE STRUCTUFtES AND METHODS

In this section, the device structures considered in this work and the methods adopted are described.

A. Simulated Devices Device Structures Fig. 2 and Table I gives schematic cross

sections and the main parameters for each of the devices considered in this work. "bo conventional bulk MOSFET structures are considered as reference cases and are compared to more sophisticated device structures.

e Conventional MOSFET's The first MOS structure fea- tures a constant high level of doping in the channel and is representative of the simplest possible approach increasing the channel doping with decreasing gate length. An extremely high doping concentration, 2 lo1' ~ m - ~ , is required to control short-channel effects.

The second bulk MOSFET is a buried-channel device based on the previous structure but with a 10 nm-thick compensating layer below the interface with dopant of the same polarity as the majority carrier. This device is included in our analysis because buried-channel MOSFET's seem of great interest for application to channel length in the 0.1 pm regime [ 121.

0 Epitaxial MOSFET An epitaxial channel structure (Epi) is adopted that conceptually resembles the transistor structure proposed in [4]. It features an almost intrinsic epitaxial silicon

FIWjNA et al.: SCALING THE MOS TRANSISTOR 943

layer grown over a heavily doped layer placed on the top of the silicon bulk. We adopt an extremely thin epitaxial layer (10 nm) and shallow junctions; furthermore, the epitaxial layer is assumed to be almost undoped to eliminate the effects of impurity scattering. The substrate below the epitaxial silicon features a highly doped region (2 lo1’ ~ m - ~ ) extending to a depth of 0.2 pm which acts as a punch-through stopper and forms a ground plane mimicking the effects of a buried gate. In such structure the threshold voltage is determined by the doping concentration of the ground plane ( N s ) and hence, doping statistic fluctuations have reduced effects on the device’s threshold voltage. In [13] in fact, it was shown by means of device simulations that uncertainties on threshold voltage related to doping fluctuations are particularly sensitive to the impurity distribution at the interface and that the inclusion of an intrinsic layer at the surface effectively reduces them.

0 SOI MOSFET’s Two ultra-thin fully depleted SO1 struc- tures are also considered here, as these are regarded as very interesting for application in deep sub-micron MOSFET’s [ 141.

The first is an SO1 device with a 10 nm silicon layer over a 50 nm buried oxide layer (S-SOI); extremely small silicon and back-oxide thicknesses are used in order to minimize short-channel effects [15], [16].

The second is a double gate MOS with an ultra-thin (10 nm) silicon layer and gate oxide thickness (D-SOI). This structure is studied due to its superior immunity to short-channel effects and current drivability [SI.

Main Device Structure Characteristics The values adopted for the main device structure parameters and supply voltage are reported in Table I; these are the values taken as defaults in the simulations unless differently specified.

All the devices feature the same LDD-like source-drain structure with an ultra-shallow junction depth (10 nm) in order to minimize the impact of short channel-effects on the threshold voltage and subthreshold characteristic and, hence, to evaluate an ultimate limit for MOS technology. As already stated, this paper includes no discussion of the effects of parasitic source-drain resistances that are also likely to become a serious limiting factor due to the extremely shallow junctions adopted. In order to limit the parasitic resistance associated with the P - ( N - ) regions, the oxide spacer has been limited to 20 nm in length. The fabrication of extremely shallow junctions like the ones considered here is a realistic possibility; this junction depths have already been successfully achieved [17]. The peak concentration of the P- ( N - ) region is limited to 2 . 10’’ cm-3 to control short channel effects (which increase as the junction profile becomes more abrupt); furthermore, such ultra-shallow junctions will be obtainable by diffusion (e.g., solid phase or vapor phase diffusion) instead of implantation; hence, in the case of p-channel, an upper limit for boron peak concentration is set by the relatively low segregation coefficient of boron. The situation should improve in the case of n-channel due to the higher segregation coefficient of phosphorus.

An extremely thin gate oxide is adopted in order to limit short-channel effects; the limit is assumed to be 3 nm ox- ide thickness for Si02 due to severe direct tunneling effect

4- Substrate

Fig. 3. Schematic representation of the source/drain region included in the simulation domain (both DD and MC) of the EPI structure; the same profiles and geometric characteristics are adopted for all the other structures.

[SI. However, even thinner equivalent oxide thicknesses are considered in order to investigate the further possibilities that may be given by the introduction of new, high-permittivity dielectric materials.

The epitaxial layer in the Epi structure and the silicon layers in the S-SO1 and D-SO1 structures are made 10 nm thick, one that is already easily achievable by adopting high- vacuum CVD techniques for epitaxial growth as developed for bipolar technology. Thinner layers would result in a limited improvement as discussed later for the epitaxial device, furthermore, a lower limitation in the SO1 case has been estimated to be about 5 nm in [SI based on the possible effects of channel quantization on threshold voltage adjustment and on the increase of channel resistance.

The back-oxide thickness for the S-SO1 device (tbox) was set to 50 nm the need for very thin back oxides in short SO1 submicron devices has been stated in previous papers [15], [16]; in this work the importance of thinning this layer has been evaluated by calculating the subthreshold characteristics and threshold voltage. The results (not reported) indicate that, as the silicon layer approaches thicknesses of the order of 10 nm, the effects of tbox have little relevance.

The supply voltage (VDD) is fixed at 1.2 V, a level, which in this work is considered the lower limit to ensure noise margin immunity. In addition, a 1.2 V supply is expected to suppress band-to-band tunneling [9] and to limit HCE due to the reduced energy supplied by the field to the carriers [18].

Fig. 3 shows a schematic representation of the drain-source region in the simulation domain for the default EPI structure; the same doping profiles and geometric characteristics are adopted for all the other simulated structures.

B. Physical Models and Numerical Methods

A range of different device structures are compared through device simulations within the framework of the semi-classical approach given by the Boltzmann transport equation; thus, we use the same conceptual modeling approach adopted in previous investigations [2], [SI. This approach suffers from certain limitations, and these are discussed below.

0 The discrete nature of the electric charge may mod- ify a device’s characteristics as, towards the lower limit of channel length, the effects of the presence or absence

944 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 41, NO. 6, JUNE 1994

of a single electron may have significant impact on the blocking characteristics of the barrier at the source-channel junction determining oscillations in the I-V characteristics. This problem has been tackled in [19] by using a molecular- dynamic simulation approach [20]. The results of [19] predict that these effects will not have great relevance at room temperature for the range of channel length studied in this paper.

a Quantum effects such as the intra-collision field effects and collision broadening discussed in [21], may be expected to modify a device's behavior with respect the predictions obtained by a semi-classical approach. In this regard, there is no general agreement on the real significance of these effects and on the actual limitations of the semi-classical approach. (different predictions have been reported by different authors, see for example 1211, [221).

Given the lack of a full quantum transport model applicable to actual 2-D device simulation, we believe that the approach adopted in this work is the only viable means to make an exploratory investigation of sub-0.1 pm MOSFET's; the results, even if sometimes lacking in precision, will be of great importance since they give an indication of the medium-term technological choices to be made in the development of future MOSFET's.

The Drift Diffusion model [23] is used to evaluate short- channel effects by computing the device's threshold voltage and subthreshold characteristic slope (S factor). Besides be- ing a very crude approximation for the modeling of charge transport in very short devices, the remarkable efficiency of the drift diffusion (DD) model still makes it preferable to both the Monte Carlo method and the hydrodynamic model when evaluating I-V characteristics under bias conditions for which no relevant hot-carrier effects (HCE) occur.

Self-consistent Monte Carlo simulation is used in the eval- uation of current drivability for channel lengths below 0.25 pm, where significant effects of velocity overshoot on currents have been reported. This approach also allows us to compare different device structures as far as carrier heating is concerned and to estimate the impact of scaling at constant voltage on hot carriers.

The electron transport model described in [24] was adopted, with the transport parameters determined in 1251. In the case of holes, the band model proposed in [26] has been adopted with transport parameters (phonon couplings and the surface scattering parameter) determined so as to fit the transport properties in the p-MOSFET inversion layer [27].

111. ELECTRICAL CHARACTERISTICS AT DEVICE TERMINALS

The results of electrical characteristic simulations are re- ported in this chapter; the impact of short channel effects on threshold voltage and on the subthreshold characteristics, cur- rent and adjustment of the long-channel threshold voltage are considered in turn. As already discussed, the analysis is carried out without addressing the problem of the minimization of the parasitic source/drain resistances but the different devices are compared with the same source/drain structures.

A. Threshold Voltage and Subthreshold Swing In this section, we report the results obtained in simulations

of short-channel effects. Although simulations were performed for both n- and p-channel devices, unless explicitly stated, the results given here are for the p-channel case.

Reduction of t$e channel length causes severe SCE as a result of the gate's inability to control the electrostatic potential and free carrier distribution within the device channel. As a consequence, a degradation is seen in the subthreshold characteristics and a related dependence of threshold voltage on channel length arises due to drain-induced barrier lowering and punch-through between the source and drain junctions. These effects were investigated by simulating the subthreshold characteristics and their dependence on gate length for differ- ent device structures; all the simulations refer to a situation in which VDS = VDD, corresponding to the worst case in terms of SCE.

Fig. 4(a) shows the threshold voltage shift as a function of gate length. Here, the threshold voltage is defined as the gate bias corresponding to IDS . LG/w = 0.5 pA. A substantial threshold shift occurs for gate lengths below 0.1 pm in all the structures considered with the exception of the double- gate MOS, which exhibits superior SCE controllability [3], [5]. By assuming that the maximum allowable threshold shift is equal to 10% of VDD, the EPI device and the S-SO1 device appear to be scalable down to 0.05 pm. All the other structures have higher limitations on LG. For LG < 0.05 pm, the S-SO1 structure-in spite of a very thin silicon thickness-exhibits an abrupt increase in SCE due to the low control the gate has over the potential distribution at the back interface.

The same conclusions about SCE can be drawn from the dependence of the subthreshold characteristic on gate length, as reported in Fig. 4@). The S-SO1 and D-SO1 devices have very low S-factor (S) in long-channel devices due to the reduced depletion capacitance between the interface and ground. The uniformly doped device exhibits a limited S- factor dependence on LG due to a good SCE control and a high S-factor in the long-channel case due to high capacitive coupling between the channel and ground. As for threshold voltage, the D-SO1 structure offers the best performance with no limitation (at least in the framework of our modeling approach) for gate lengths down to 0.025 pm.

The results obtained by this SCE evaluation in terms of electrical Characteristics well correlates with the 2-D contours of electrostatic potential distribution reported in Fig. 5 for the case LG = 0.05 pm, VG = VTH, and VDS = VDD. By comparing the EPI and the S-SO1 structures, is clearly noticed that in the latter the equipotential lines are less confined within the channel region due to the reduced gate control.

B. Current Drivability The current drivability for different device structures is

estimated by means of Monte Carlo device simulation, taking into account the effects of velocity overshoot on device characteristics.

Fig. 6 reports the maximum drain current as a function of channel length for the different device structures. Here, in

FIEGNA et al.: SCALING THE MOS TRANSISTOR 945

- 2 U

>E 0.4

'f 0 . 3 Q 2 0.2

> 0.1 9

n 4

a - - 0

2 0.0 L c

-0.1

- llnif . . Bur . t 9EPI *--.E s-501

50 I

10.' 1 oo

gate length [ p m ]

(b)

Fig. 4. (a) Threshold voltage shift with respect to the long channel device as a function of gate length and for different device structures. (b) Subthreshold characteristic logarithmic slope as a function of gate length and for different device structures.

Fig. 5. Two-dimensional distribution of the electrostatic potential within the EPI (a) and S-SO1 (b) 0.05 Im transistors biased at threshold condition, VDS = 1.2 v.

order to present a fair comparison among the different devices, we assumed that the gate work function could be modified at will so as to achieve the same threshold voltage independent of the channel length and device structure.

The double-gate structure, since it has a double channel at the two interfaces, yields higher current drivability. The S-SO1 structure provides higher currents than the EPI at relatively long channel lengths due to the lower transverse electric field and higher saturation current [9]. As a general result, it can be noticed that the differences among different device structures are lost in the ultra-short gate length limit. This effect is due

-* EPI 'Y

t 4 s-sol

1 0 - 5 L-

1 o-2 io-' 1 oo Gate length [pm]

Maximum drain current as a function of gate length for different Fig. 6. p-MOSFET structures bias at Lbs = VGS = -1.2 V.

V,,=-l.2V 37-- ;/

v - 0.0 - 0.5 - 1.0 - 1.5

Drain Voltage [VI

Fig. 7. I-V output characteristics of a p-channel EPI MOSFET with LG = 0.05 pm.

to nonnegligible source/drain series resistances related to the ultra-shallow junctions. Furthermore, due to high electric fields at the source channel end a nonohmic regime is established which equalizes current drivability for the different structures.

The simulated output I-V characteristic of a p-channel 0.05 ,um EPI (LEFF 21 0.035 pm) MOSFET is reported in Fig. 7. This may be qualitatively compared with those reported for a double-gate MOS of comparable channel length in [ 5 ] . Consistently with greater short-channel effects, the EPI device presents significant output conductance due to channel length modulation.

C . Threshold Voltage Adjustment Another very important issue that must be addressed when

evaluating the possible scalability of a MOSFET structure to the sub-0.1 pm regime is the controllability of the threshold voltage. As already stated in [ 5 ] , threshold voltage adjustment in ultra-short D-SO1 devices would require control of the gate work function. This is also true for the S-SO1 device, as Fig. 8 shows: here the threshold voltage is shown as a function of channel length for the EPI structure and for the S-SO1 structure with both N + and P+ polysilicon gates. In the S-SO1 case, the silicon channel is undoped, it is not possible to obtain a threshold voltage compatible with an acceptable VDD value. A very high channel doping level

946 IEEE TRANSACTIONS ON ELECTRON DEVICES. VOL. 41, NO. 6, JUNE 1994

-1 .5

s-so1 P' poly - L - L I +

EPI - 4

6 . ..., s-SO1 N + poly

"O"- - . .Q. - - ................................. 0

1 0 - 2 10-1 1 0 0

Gatp length [pm]

Fig. 8. Threshold voltage as a function of channel length for the p-EPI MOSFET with P+ poly-gate and the p-S-SO1 MOSFET with P+ and N+ poly gates.

would be required (in the order of 1OI8 ~ m - ~ ) . The EPI structure, conversely, makes threshold voltage control possible by adjusting the dopant concentration in the highly doped silicon region located below the undoped epitaxial layer. This is demonstrated by Fig. 8 where a good threshold voltage value is attained with a conventional P+ polysilicon gate and a concentration Ns = 10" cm-3 without affecting the channel region. The impact of variations in Ns on SCE over the range of useful threshold voltage values is not significant, as will be shown in the next section. Hence, in the EPI case, the threshold voltage can be treated as an independent variable and can be optimized without significant degradation of overall device performances. Furthermore, as already discussed, the effects of microscopic doping fluctuations on the device threshold voltage are effectively limited by the introduction of an intrinsic layer at the interface. This effect was discussed in [13] where device simulations evidenced that fluctuations of the doping distribution determine a remarkable uncertainty on the threshold voltage. In this work, the same approach proposed in [13] was applied to very short channel devices (0.05 pm); comparison among the EPI, the uniform and the double gate structure confirms the results of [13] proving that the EPI structure, due to the presence of an almost intrinsic layer below the interface, is remarkably less prone to the effects of doping fluctuations as it features much lower deviations compared to the other structure. Finally, the introduction of such a layer determines a reduction of the transverse electric field at the interface and hence, reduces the impact on threshold voltage of energy quantization in the channel.

The results reported in this section indicate that the double- gate MOSFET, as already stated in [5 ] , has very good char- acteristics for ultra-short gate lengths. The S-SO1 structure with ultra-thin silicon is preferable to other, more conventional structures, for gate lengths down to 0.075-0.1 pm, but at shorter gate lengths it suffers severe SCE since the gate has little control over the back Si-Si02 interface. Finally, the EPI MOSFET structure exhibits good SCE characteristics for LG values down to 0.05 pm and is very attractive since it offers the possibility of easy threshold voltage control and to better integration than SO1 devices. In particular the double-gate structure in spite of very good electrical characteristics is likely to be limited in its application to ultra-short devices by its

-0.2 - U * d

-0.3

-0.4

91

90 - 0

89 p E

88 5 I

L

U

c

87

66 10"

Doping [cm-'1

Fig. 9. Threshold voltage and S-factor dependence on the ground plane doping concentration for a p-channel EPI structure with LG = 0.05 pm; VDS = -1.2 v.

three-dimensional nature that causes high process complexity and cost.

IV. THE EPI MOS STRUCTURE In this section the EPI MOSFET is investigated in more

detail in view of its attractive characteristics. In particular, the effect of variations in various structural parameters on SCE is studied, and the requirements for further possible scaling are examined.

A. Dependence on the Ground Plane Concentration Fig. 9 shows the dependence of threshold voltage and S-

factor on dopant concentration in the ground plane (Ns). By varying the dopant concentration in the silicon under the channel region, it is possible to control the threshold voltage and obtain values compatible with VDD = 1.2 V. A nonmonotonic dependence of the S-factor on bulk dopant is typical of short-channel devices. In fact, increasing the dopant concentration leads, in long-channel devices, to an increase in S due to the greater capacitive coupling between the interface and ground. With short channel devices, on the other hand, decreasing NS below a certain critical value (which is dependent on the channel length and the device structure) leads to an increase in S due to the substantial short-channel effects. However, variations in Ns within the range of interest for VTH adjustment (5 1017-2 . 10" ~ m - ~ ) have little impact on the S-factor, which remains below 90 mVDec.

Fig. 10 shows S as a function of Ns for different channel lengths; with LG > 0.075, "long channel" behavior is obtained with increasing S as a function of N s .

B. Dependence on the Junctions Depth

The sensitivity of SCE to variations in junction depth has been analyzed. Fig. 1 1 shows the S factor shift induced in an LG = 0.05 pm transistor as the junction depth is varied; these results are given for the cases Ns = 10" and N s = 2 . 10l8 ~ m - ~ , the latter leading to less sensitivity due to better control of the short-channel effects. An interesting feature can be noted in the dependence of S on &I: at the minimum X J ~ value, a lower S factor is obtained in the case

FTEGNA et al.: SCALING THE MOS TRANSISTOR

150

140 9 i I \

f . . L,=~.!..p+m ..... .... .. ....... + 1

70

60 I-- 10''~ 1 0 ' ' ~

Doping [ ~ m - ~ ]

Fig. 10. S-factor as a function of the ground plane dopant concentration for EPI p-channel devices and different channel lengths; Sbs = vc;~ = -1.2 V.

/ 'J!

85 0 10 20 30 40 50 60

'J , , 'J2 Inml Fig. 1 1 . S-factor dependence on the junctions depth for the EPI 0.05 pm MOSFET and two different values of Ns. X J ~ is vaned for - Y J ~ = 30 nm; -YJZ is varied for S J I = 10 nm.

N s = 10'' due to the lower capacitive coupling between the channel and ground. However, the increase in junction depth enhances short-channel effects where the doping concentration is lower and, consequently, the dependence of S on NS is reversed. The same effects occur in the case of X J ~ but at greater junction depths.

C . Dependence on the Epitaxial-Silicon Thickness Fig. 12 shows the behavior of the S-factor and threshold

voltage shift, with respect to the long-channel case, as a function of the thickness of the undoped silicon layer. Short- channel effects drop off with decreasing t s ~ due to the greater transverse electric field induced by the underlying heavily doped region; such dependence is not great relaxing the need for ultra-thin epitaxial layers. A 10 nm thickness may be considered a good compromise between short-channel characteristics and both the problems of channel quantiza- tion affecting the threshold voltage and increasing channel resistance which limits t s ~ to about 5 nm.

D . Dependence on Gate Oxide Thickness Short-channel effects are critically dependent on the gate

oxide thickness: reducing this dimension enables a better gate control over the electrostatic potential distribution within the device channel. For this reason, the lower limit on Si02 thickness imposed by direct tunneling conduction [SI should be considered the major limit when scaling the MOSFET channel

0 5 10 15 20 25 84 L-

Epi th ickness [nm]

Fig. 12. epitaxial layer thickness for the 0.05 pm device.

S-factor and threshold voltage shift as a function of the silicon

1 0 - ~ Epitaxial p-MOSFET. t,,=1.5 nni. V D b = - l . 2 V W / L = I r

~ 0 . i (I n 0.5 1 . n

\'<,, I\ I Fig. 13. t o ~ = 1.5 nm, dy.5 = 2 .

Subthreshold characteristics for p-channel EPI MOSFET's with Lc: = 0.05, 0.025 pm, S,Ds = -1 .2 V.

length. Figs. 13 and 14 show the effects of reducing the oxide thickness: Fig. 13 gives the subthreshold characteristics for devices with 0.025 pm and 0.05 pm channels and an equivalent oxide thickness of 1.5 nm and N s = 2 . 1018 biased at VDS = 1.2 V; Fig. 14 gives the channel length dependence of threshold shift and subthreshold swing for this ultra-thin oxide structure. By reducing the equivalent oxide thickness, scaling to below LG = 0.05 km seems possible for the epitaxial structure without short-channel effects becoming unacceptable. This result justifies current efforts to develop new dielectrics with higher permittivities than SiOz. Such materials would enable equivalent thicknesses below 3 nm while, at the same time, limiting the direct tunneling current.

V. HOT-CARRIER EFFECTS

In this chapter, we discuss certain issues regarding the constant voltage scaling of hot-carrier effects at gate lengths below 0.1 pm. This discussion is based on the results of self-consistent MC simulations. Different device structures are compared as far as hot-carrier effects are concerned. Here, the results of HCE simulations are not adopted in order to determine the limitations on devices' dimensions because, until now, no reliable models relating carrier heating in the semiconductor to actual degradation processes have been developed for ultra-short devices. The effects of scaling at constant VDD are investigated in order to determine whether a dramatic increase in carrier heating should be expected. The

948 IEEE TRANSACTIONS ON ELE4TRON DEVICES, VOL. 41, NO. 6. JUNE 1994

VI .A...........*

-0 .1 1 ’ 70 10-2 10-1 1 0 0

gat^ length [ p m ]

Fig. 14. S-factor and threshold voltage shift as a function of gate length for a pchannel EF’I structure withtox = 1.5 MI, N s = 2.10’’, VDS = -1.2 V.

EPI ..._

-1.0 - ....... s-so1 U % UNIF

- D-SO1 P $

h

0.25 0.30 0.35 0.40 0.45

Position [pm]

= 2.5 V,VGS = 1.25 V. Fig. 15. LG = 0.05 p n and

Electron mean energy at the interface of the different structures for

HCE results given in this chapter refer, unless otherwise stated, to the n-MOS case. Gate work-function controllability has been assumed in order to obtain the same threshold voltage regardless of device structure and channel length.

A . Comparison of Different Device Structures The various device structures are compared in Fig. 15 for

the case of LG = 0.05 pm, VDS = 2.5 V and VGS = 1.25 V; these electron mean energy profiles computed at the front Si- Si02 interface suggest that the double-gate structure is slightly less affected by HCE than others. In this regard, it should be noticed that the maximum electric field in the D-SO1 case is higher than in, for example, the EPI case, and the energy is lower due to the more abrupt electric field profile within the channel, leading to a greater delay in the carrier heating process.

B. Scaling of Carrier Heating at Ultra-Short Gate Lengths The following is an investigation into the effects of scaling

a MOSFET to ultra-short gate lengths. This is a topic of great interest, because recent experimental work carried out by different groups has led to contradictory results in terms of substrate current dependence on gate length. More precisely, some experimental results indicate a decreasing substrate current for LEFF < 0.15 pm [28], or continuously increasing

1 .o

0.0 0.1 0.2

Position [ p m ]

Fig. 16. D-SO1 (dashed) structures; VDS = 2.5 V, VGS = 1.25 V.

Electric field and mean energy along the channel of EPI (solid) and

ISIJB for decreasing L [7], [29]. Fig. 16 show the electric field and mean electron energy computed at the front interface of the EPI structure with 0.025 pm < LG < 0.15 pm. Calculations are performed for VDS = 2.5 V and VGS = 1.25 V, approximately corfesponding to the maximum HCE degradation.

Reducing the gate length from 0.15 to 0.05 pm does not appreciably affect the maximum electric field, but it does lead to an increase in the “channel field,” or the electric field in the channel region between the source and the pinch-off point (to the left of the dashed line in Fig. 16), which has a marginal effect on carrier heating.

For LG = 0.025 pm, it is not possible to distinguish the channel region and the pinch-off region as the high field region broadens towards the source due to relevant short channel effects; no dramatic increase of the mean energy peak value is seen. In qualitative agreement with the results reported in [7], [29], carrier heating appears to increase with decreasing channel length, even at these ultra-short channel lengths.

To summarize, the results of self-consistent MC simulations indicate that scaling MOSFET dimensions at constant VDD will not produce dramatic increase in HCE. The D-SO1 struc- ture suffers less carrier heating and hence, a better reliability may be predicted for this type of device.

Since these ultra-thin devices will operate at low gate voltages (11 .5 V), it can be assumed that no significant increase in hot-carrier device degradation will occur. Never- theless, recently reported experimental data reporting substrate currents at drain bias as low as 0.6 V [29], [30] prevent us giving a conclusive assessment. These measurements, hardly explainable on the basis of a conventional semi-classical modeling approach, will require more investigation before a satisfactory explanation can be given.

VI. CONCLUSION In this paper device numerical simulation was applied to

the investigation of the scaling of MOS transistors to gate lengths well below 0.1 pm. Several device structures were compared considering all the most important issues related

FIFGNA et al.: SCALING THE MOS TRANSISTOR

POSSIBLE SCALING SCENARIO

Vdd t Tox 1

1 - 005 0 1pm

Fig. 17. Scaling concept for LG < 0.1 A m .

to miniaturization of MOSFET dimensions to such ultra-short channel lengths. The limits on scalability of the gate oxide thickness and power supply voltage were enforced by adopting a scaling approach that maintains such quantities constant. A device structure featuring a thin, almost intrinsic silicon epitaxial layer grown over an highly doped substrate was studied in details in view of its well promising characteris- tics.

Fig. 17 summarize the results of this study by visualizing the new scaling concept that must be adopted for gate lengths below 0.1 pm: constant gate voltage and oxide thickness must be adopted; further oxide thickness reduction will be possible in the future by adopting a new dielectric material with higher permittivity than SiO2.

The main results of this study are outlined below. By adopting a scaling approach that maintains the oxide thickness and the supply voltage constant at decreasing gate length, scaling to LG = 0.05 pm is achievable using a MOSFET structure featuring an ultra-thin undoped silicon layer grown over an highly-doped region acting as punch-through stopper. The advantages of SO1 structures in terms of sub- threshold characteristics and current drivability seem to vanish in the ultra-short gate length limit. For this reason and in view of problems in terms of threshold voltage adjustment and high process complexity and cost, the SO1 device does not seem extremely promis- ing for extensive use in future VLSI below 0.1 pm. Nonetheless, the SO1 structure features some advantages due to reduced parasitic capacitances associated to the draidsource junctions, thus it may be used for specific applications requiring very high speed operation, pro- vided that the problems of threshold adjustment will be solved (i.e., gate work-function control). Simulation within the semi-classical domain indicate that further scaling may be obtained by adopting the epitaxial structure if a new dielectric material with higher permittivity than Si02 will be adopted. This result justifies future efforts towards new high-permittivity dielectrics. The double-gate MOSFET provides the best character- istics in terms of short channel effects and performances but its extensive use seems to be limited by high cost and process complexity.

From the results of this work some requirements for future technology can be anticipated:

ACKNOWLEDGMENT The authors wish to thank T. Kimura and S. Nakamura for

their support with the computer environment. The continuous support and encouragement of Dr. A. Kasami, Dr. H. Hara, Dr. N. Goto, and Dr. N. Toyoda is also gratefully acknowledged.

949

Techniques for obtaining very shallow junctions like, for example, the solid phase diffusion proposed in [31] and successfully applied in [7], [17] to devices with 0.1 pm gate length, must be investigated and further improved. New insulator materials with higher permittivity than Si02 should be developed in order to overcome the problems related to direct tunneling. Gate work function controllability would be a very attrac- tive feature as it would make possible to improve threshold voltage control by decoupling this problem from that of short channel effects control. Very shallow junction will increase parasitic series re- sistances requiring the adoption of some measures like silicide shunts over the source/drain diffusions and the improvement of metallizations to decrease contact resis- tance. Altemative source/drain structures should also be investigated like elevated source and drain. This topic is of great importance and interest for future MOS technology, hence future work about it is mandatory. Finally, further work is required to investigate on the actual improvements that may be expected in terms of AC characteristics of CMOS circuits including these ultra short channel devices.

REFERENCES

M. Aoki, T. Ishii, T. Yoshimura, Y. Kiyota, S. Iijima, T. Yamanaka, T. Kure, K. Ohyu, T. Nishida, S. Okazaki, K. Seki, and K. Shimohigashi, “0.1 pm CMOS devices using low-impurity-channel transistors (LICT),” in IEDM Tech. Dig., pp. 939-941, 1990. D. A. Antoniadis and J. E. Chung, “Physics and technology of ultra-short channel MOSFET devices,” in IEDM Tech. Dig., pp. 21-24, 1991. R. H. Yan, A. Ourmazd, K. F. Lee, D. Y. Leon, C. S. Rafferty, and M. R. Pinto, “Scaling the silico-oxide-semiconductor field-effect transistor into the 0.1 pm regime using vertical doping engineering,” Appl. Phys. Lett., Vol. 59, pp. 3315-3317, 1991. T. Hashimoto, Y. Sudoh, H. Kurino, A. Narai, S. Yokoyama, Y. Horiike, and M. Koyanagi, “3 V operation of 70 nm gate length MOSFET with new double punchthrough stopper structure,” Ext. A h . of Int. Conf. on Solid Stare Devices and Materials, pp. 490.492, 1992. D. J. Frank, S . E Laux and M. V. Fischetti, “Monte Carlo simulation of a 30 nm dual-gate MOSFET: how short can Si go?,” in IEDM Tech. Dig., pp. 553-556, 1992. A. Toriumi, T. Mizuno, M. Iwase, M. Takahashi, H. Niiyama, M. Fukumoto, S . Inaba, I. Mori, and M. Yoshimi, “High speed 0.1 Irm CMOS devices operating at room temperature,” in Ext. A h . of Int. Cony on Solid State Devices and Materials, pp. 487489, 1992. M. Saito, T. Yoshitomi, M. Ono, Y. Akasaka, H. Nii, S. Matsuda, H. Momose, Y. Katsumata, Y. Ushiku, and H. Iwai, “An SPDD MOSFET structure suitable for 0.1 pm and sub 0.1 p m channel length and its electrical characterization,” lEDM Tech. Dig., pp. 897-900, 1992. T. Morimoto, H. S. Momose, M. Tsuchiaki, Y. Ozawa, K. Yamabe, and H. Iwai, “Limits on gate insulator thickness for MISFET operation in pure-oxide and nitride-oxide gate cases,” Ext. Ahs. of Int. Cor$ on Solid State Devices and Materials, pp. 23-25, 1991. J. R. Brews, High speed Semiconductor Devices, S. M. Sze, Ed. New York: Wiley Interscience, 1990. F. Stem and W. E. Howard, “Properties of semiconductor surface inversion layers in the electric quantum limit,” Phys. Rev., Vol. 163, No. 3, pp. 816-835, 1967 H. Ohkura, “Quantum effects in Si U-MOS inversion layer at high substrate concentration,” Solid State Electron., vol. 33, no. 12, pp. I58 1-1585, 1990.

950 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 41, NO. 6, JUNE 1994

[12] T. Yoshitomi, M. Saito, H. Oguma, Y. Akasaka, M. Ono, H. Nii, Y. Ushiku, H. Iwai, and H. Hara, “Ultra-shallow buried-channel y- MOSFET with extremely high transconductance,” 1993 Symp. on V U 1 Technol. Tech. Dig.

[13] K. Nishinohara, N. Shigyo, and Tetsunori Wada, “Effects of microscopic fluctuations in doping distributions on MOSFET threshold voltage,” IEEE Trans. Electron Devices, vol. 39, pp. 634-639, 1992.

[14] Colinge, Silicon on Insulator Technology: Materials to VLSI. New York: Kluwer, 1990.

1151 J. G. Fossum, S. Krishnan, and P.-C. Yeh, “Performance limitations of deep-submicron fully depleted SO1 MOSFET’s,” 1992 IEEE Int. SO1 Conf. Proc., pp. 132-133.

[16] Y. Omura, S. Nakashima, K. Izumi, and T. Ishii, “0.1 pm-gate, ultrathin- film CMOS devices using SIMOX substrate with 80 nm-thick buried oxide layer,” IEDM Tech. Dig., pp. 675-678, 1992.

[17] M. Ono, M. Saito. T. Yoshitomi, C. Fiegna. T. Ohguro, and H. Iwai, “Sub-50 nm gate length n-MOSFET’s with 10 nm phosphorous source and drain junctions,” IEDM Tech. Dig., pp. 119-122, 1993.

[18] F. Venturi, E. Sangiorgi, and B. Ricc6, “The impact of voltage scaling on electron heating and device performance of submicrometer MOSFET’s,” IEEE Trans. Electron Devices, vol. 38, pp. 1895-1904, 1991.

[I91 K. Yano, D. K. Ferry, and K. Seki, “Molecular-dynamics study of charge quantization on 1-100 nm Si-MOSFET,” IEDM Tech. Dig., pp. 557-560, 1992.

[20] D. K. Ferry, A. M. Kriman, M. J. Kann, and R. P. J. Joshi, Computer Physics Commun., vol. 67, p. 119, 1991.

[21] J. R. Barker and D. K. Ferry, “On the physics and modeling of small semiconductor devices-I,” Solid Stare Electron., vol. 23, pp. 5 19-130, 1980.

[22] S. K. Sarker, J. H. Davies, F. S. Kahn, and J. W. Wilkins, “Quantum corrections to the Boltzmann equation for transport in semiconduc- tors in high electric fields,” Phys. Rev. B , vol. 33, pp. 7263-7266, 1986.

1231 T. Wada and R. Dang, “Development and application of a high- speed 2-dimensional; time dependent device simulator (MOS2C),” Proc. NASECODE IV. p. 108, 1985.

[24] R. Brunetti, C. Jacoboni, F. Venturi, E. Sangiorgi, and B. Riccb, “A many-band silicon model for hot-electron transport at high energies,” Solid State Electron., vol. 32, 1663-1667, 1989.

[25] C. Fiegna and E. Sangiorgi, “Modeling of high energy electrons in silicon at the microscopic level,” IEEE Trans. Electron Devices, vol. 40, pp. 619-627, 1993.

1261 F. Venturi, A. Abramo, E. Sangiorgi, I. Higman, C. Fiegna, and B. Ricc6, “An isotropic best-fitting band model for electrons and hole transport in Silicon,” IEDM Tech. Dig., pp. 503-506, 1991.

[27] J. T. Watt and J. D. Plummer, “Universal mobility-field curves for electrons and holes in MOSFET inversion layers,” 1981 Symp. on VLSI Technol. Tech. Dig., pp. 81-82, 1981.

[28] G. G. Shahidi, D. A. Antoniadis, and H. I. Smith. “Reduction of channel hot-electron-generated substrate current in sub 150 nm channel length Si MOSFET’s,” IEEE Electron Dev. Lett., vol. 9, pp. 497-499, 1988.

[29] T. Mizuno, A. Toriumi, M. Iwase, M. Takahashi, H. Niiyama, M. Fukumoto, and M. Yoshimi, “Hot carrier effects in 0.1 pm gate length CMOS devices,” in IEDM Tech. Dig, pp. 695-698, 1992.

[30] L. Manchanda, R. H. Storz, R. H. Yan, K. F. Lee, and E. H. West- erwick, “Clear observation of sub-band gap impact ionization at room temperature and below in 0.1 @m Si MOSFETs,” IEDM Tech. Dig., pp. 994-996, 1992.

[31] H. Takemura, “BSA technology for sub-100 nm deep base bipolar transistors,” in IEDM Tech. Dig., pp. 375-378, 1987.

Claudio Fiegna was bom in Bologna, Italy, in 1963. He received the Laurea degree in electrical engineering from the University of Bologna in 1988.

He then joined the Department of Electron- ics, University of Bologna working in the field of electron devices. In particular he has worked on the study and characterization of latchup in CMOS technology, characterization and modeling of hot- electron effects in MOSFET’s and Monte Carlo device simulation. From July 1992 to July 1993 he was visiting Researcher at the Toshiba ULSI

Laboratories, Kawasaki, Japan, where he was engaged in the study of ultra- small MOSFET’s. In 1994 he joined the University of Ferrara, Italy.

Hiroshi Iwai (A‘79--SM‘93) was bom in Tokyo, Japan, on April 25, 1949. He received the B.S. and Ph.D. degrees in electrical engineering from the University of Tokyo, Japan, in 1972 and 1992, respectively.

In 1973, he joined the Research and Devel- opment Center of Toshiba Corporation, Kawasaki, Japan, where he developed the first generation of Toshiba’s NMOS LSI technology. From 1978 to 1980 he was also associated with NEC-Toshiba Information Systems, Inc., Kawasaki, Japan. From

1979 to 1989 he was with the Semiconductor Device Engineering Laboratory in the Semiconductor Group of Toshiba. In 1983 and 1984, he worked with Prof. R. W. Dutton at the Integrated Circuit Laboratory, Stanford University, Stanford, CA, as a Visiting Scholar, where he studied small-geometry effects of MOSFET capacitances. Since 1989, he has been associated with the ULSI Research Laboratories in the Research and Development Center of Toshiba. Since joining Toshiba, he has contributed to the development of processes and circuit design of several generations of high density static RAM’s, dynamic RAM’s and logic LSI’s including CMOS, bipolar, and Bi-CMOS devices. He has also been involved in research on device physics related to small- geometry MOS and bipolar transistors, as well as research on CAD regarding device/pmcess modeling and layout/schematic design. Currently he is working on the development of advanced CMOS/bipolar logic/analog devices and their technologies.

Dr. Iwai is an associate editor of IEEE EDS Newsletter and a guest editor of a Special Issue of IEEE Trans. on Electron Devices on “Submicron Bipolar/BiCMOS Devices and Technologies.” He is a member of the Japan Society Applied Physics.

Tetsunori Wada was bom in Kamakura Japan, in 1951. He received the B.S. degree in applied physics from the University of Tokyo, Tokyo, Japan, in 1975.

He then joined the Toshiba Corporation where he was engaged in microlithography technology from 1975 to 1981. He is currently engaged in the numerical modeling of semiconductor devices at Research and Development Center.

Mr. Wada is a member of the Japan Applied Physics Society.

Masanobu Saito was bom in Tokyo, Japan, on November 21, 1961. He received the B.S. and M.S. degrees in solid state physics from Waseda Univer- sity, Tokyo, Japan, in 1985 and 1987, respectively.

In 1987, he joined the ULSI Research Labo- ratories of Toshiba Corporation, Kawasaki, Japan. Since joining Toshiba, he has contributed to the development of processes and device technology for CMOS Gate Arrays. Currently he is working on the development of advanced- CMOS devices and their technologies.

Enrico Sangiorgi was born in Faenza, Italy, in 1954. He received the Laurea degree in electrical engineering from the University of Bologna in 1979.

In 1982, he was appointed Reasearch Associate at the University of Bologna. In 1983 and 1984 he was a Visiting Scientist at Stanford University, CA, and since 1985 he was a consultant of AT&T Bell Laboratories, Murray Hill, NJ. In 1986, he was appointed Associate Professor of Applied Electronics at the University of Udine, Italy, and in 1987 he joined the the University of Bologna, Italy. In 1993 he became Full Professor of Applied Electronics at the University of Udine, Italy.

His research interests include the physics, modeling, and fabrication of solid-state devices and integrated circuits. In particular he has been working on silicon dioxide physics, hotcarrier effects in MOSFET’s, contact modeling, latch-up in CMOS, Monte Carlo methods for carrier transport, and advanced device simulation techniques.

FIEGNA el al.: SCALING THE MOS TRANSISTOR

Bruno Ricco was born in Parma, Italy, in 1947. In 1971 he graduated in electrical engineering at the University of Bologna, Italy, and in 1975 received the Ph.D. from the University of Cambridge, U.K., where he had been working at the Cavendish Laboratory.

In 1980 he became Full Professor of Applied Electronics at the University of Padova, Italy. In 1983 he joined the Department of Electronics of the University of Bologna, Italy. In 1981 he was a visiting Scholar at the University of Stanford and, later, at the IBM Thomas J. Watson Research Center, Yorktown Heights, NY. In 1988 he was appointed Associate Editor for Europe of fEEE Transactions on Electron Devices. Since 1983 he has been consulting for the European Economic Community in the area of microelectronics. His scientific interests concem solid state devices and integrated circuits. In particular, he has worked on electron transport in semiconductors, tunneling in heterostructures. silicon dioxide physics, hot electrons effect in MOSFET’s, latch-up in C-MOS structures and Monte Carlo device simulation. In the area of integrated circuits he is currently working on fault modeling and simulation, design-for-testability techniques, self-checking circuits and, more in general, in IC design and testing.

Dr. Ricco was nominated Chairman of the Technical Committee of the Consortium JESSI-Italia in 1991. In 1992 he became a member of the BLR Board of the JESSI organization.

95 1

![Approach and Methodology - RTIrti.gov.in/rticorner/RTI_methodology[1].pdf · 1 RTI Implementation – Issues and Methodology Report 1 PricewaterhouseCoopers Understanding the”key](https://static.fdocument.org/doc/165x107/5a79ea3b7f8b9ab80d8b8343/approach-and-methodology-1pdf1-rti-implementation-issues-and-methodology.jpg)