ECE7570 Individual Take Home Exam W’06 - Wayne State...

Click here to load reader

Transcript of ECE7570 Individual Take Home Exam W’06 - Wayne State...

ECE7570 Individual Take Home Exam W’06

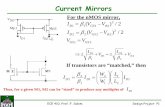

DUE: April 24, 2006, Monday on or before 5PM NOTE: (W/L) specification L is the drawn length, but in βn=(Kn/2)(W/Leff) and βp=(Kp/2)(W/Leff) calculations the length is the effective length. Use the following PSPICE MODEL in your simulation: .MODEL NMOS1 NMOS VTO=1.0 KP=40U + GAMMA=1.0 LAMBDA=0.02 PHI=0.6 + TOX=0.05U LD=0.5U CJ=5E-4 CJSW=10E-10 + U0=550 MJ=0.5 MJSW=0.5 CGSO=0.4E-9 CGDO=0.4E-9 .MODEL PMOS1 PMOS VTO=-1.0 KP=15U + GAMMA=0.6 LAMBDA=0.02 PHI=0.6 + TOX=0.05U LD=0.5U CJ=5E-4 CJSW=10E-10 + U0=200 MJ=0.5 MJSW=0.5 CGSO=0.4E-9 CGDO=0.4E-9 I. (10%) Small signal circuit analysis. Analyze the two-port amplifier circuit shown in Figure 1.

(a) (2.5%)Draw the complete small signal equivalent circuit. That is, it must include all the current source and conductance.

(b) (2.5%)Determine the Y parameters. (c) (2.5%)Determine Av=Vout/Vin, Ai=Iout/Iin, AZ =Vout/Iin, Ro=Vout/Iout (d) (2.5%)Find simplified expressions in (c) using the assumption that gm>>gd

Vb

Vin

IinVout

Vdd

M1

M2M4

M3

Iout

Figure 1. Two port amplifier circuit. II. (10%)Regulated Cascode Current Source. NOTE: this current source is the one used in the D/A circuit lab project.

Figure 2. Regulated Cascode Current Source.

Using the negative feedback principle one can increase the output impedance Ro. If the output voltage Vo increases, it causes IDS4 to increase and VDS3 to increase without feedback. The feedback amplifier A senses the change in its input and apply a reduce VGS4, which reduce IDS4. That is, IDS4 is maintained for a changing output voltage VDS4. Hence, increase output impedance Ro. Current source circuits in Figure 2 are considered single-port circuit. Unlike the circuits in Figure 1, there is no input signal Vi. To determine the small-signal output impedance Ro, apply the output voltage Vo and determine the resulting output Io. The voltages Vb1 and Vb2 are constant biasing voltages. (a) Show that the output impedance of the circuit in Figure 2(a) with an ideal amplifier A is given by:

]rg 1)A(rg1[r R ds3ds4ds3m4ds4o +++= (b) Show that the circuit in Figure 2(b) is the implementation of Figure 2(a) with the ideal amplifier gain A given by:

)r //r(g A ds2 ds1m1= (c) Shows that with the given assumption, the approximate output impedance is given by:

2rg

R3o

2m

o ≈

Assume:

dsimi

ds4ds3ds2ds1o

g gr r rr r

>>≈≈≈=

III.(10%) Widlar Current Source. Design the current source to generate 20uA. Given the transistor sizing and factor n: Wn=10.8u, Ln=6.6u; Wp=30u, Lp=6.6u ; n=4.

(a) (2.5%)Ignoring bulk effect, theoretically determine the value of the biasing resistor Rb to achieve 20uA.

(b) (2.5%)Using the value of Rb in (a), show the Pspice netlist and printout of the quiescent current of MB1, MB2, MB3, and MB4. NOTE no credit if (a) is wrong.

(c) (2.5%)Including the bulk effect in MB4, derive the equation to compute Rb assuming the transistor sizing and factor n remain the same. Compute Rb using this equation.

(d) (2.5%)Using the value of Rb in (c), show the Pspice netlist and printout of the quiescent current of MB1, MB2, MB3, and MB4. NOTE no credit if (c) is wrong.

MB3

(W/L)n

MB4

4(W/L)n

Rb

Vdd

Vss

MB1

(W/L)p

MB2

(W/L)p

Figure 3. Widlar Current Source

IV.(10%) Differential Amplifier Common Mode Range Applying common voltage to both inputs, with each transistor operating in saturation region. Where CMR= Vi(max) – Vi(min). In the following, assume all n transistors are of the same size (W/L)n, and all p transistors are of the same size (W/L)p. Also the sizing of n and p satisfies the requirement that ∆n = ∆p.

(a) (5%)In Fig 4(a), derived the minimum, Vi(min), and maximum, Vi(max) input voltage that guarantee each transistor remains in saturation.

(b) (5%)In Fig 4(b), derived the minimum, Vi(min), and maximum, Vi(max) input voltage that guarantee each transistor remains in saturation.

Vo

Vi2Vi1

Vb3

Vb4

M1 M2

M3 M4

M5a

M5b

Vdd

M1 M2

M3 M4

M5a

M5bVb1

Vb2

Vi1 Vi2

Vo

(a) (b) Figure 4. Differential Amplifier input stage

V.(10%) Differential OTA filter implementation. NOTE: the polarity of the output is reversed to simplify the schematic diagram. Derive the implemented transfer function, TF(s)= Vo(s)/Vi(s).

VI. (50%) Design the opamp that satisfy the following common specifications:

Vdd=+5V, Vss=-5V, -4.5V<=CMR<=3V, Avd>=20,000, PM>=85, CC=1pF; And your particular individual specifications are given in TABLE1.

Figure 6. Opamp circuit TABLE1. Individual Problem Specifications: No. Student Name SR(in

V/us)* GB(in MHZ) Ro (in

Kohm) 1 Abtahi, Mehrdad 5 5 6 2 Akkinepally,

Harshavardhan 5 6 5

3 Balasubramaniam, Arvind5 7 4 4 Bharadwaj, Abhijith S 5 8 3

5 Bhatia, Anuj 5 9 2 6 Chauhan, Pranav Y 5 10 1

7 Choudhary, Moyna 6 5 6 8 Fatima, Afroze 6 6 5

9 Gokavarapu, Sandeep 6 7 4 10 Haider, Adnan 6 8 3

11 Kakar, Sameer 6 9 2 12 Karanam,

VenuDurgaPrasa 6 10 1

13 Katragadda, Chaitanya 7 5 6 14 King, Brady W 7 6 5

15 Kitambi, Srivatsa N 7 7 4 16 Koya, Animesh T 7 8 3

17 Li, Yung-Sen 7 9 2 18 Mahenderker, Saikiran 7 10 1

19 Narendar, Harish 8 5 6 20 Noor, Faiaz U 8 6 5

21 Peyyeti, Pratima 8 7 4 22 Raghavendra,

Laxmikanth V 8 8 3

23 Reisner, Luke A 8 9 2 24 Sandhu, Gurmanjyot 8 10 1

25 Selvan, Madeswaran 9 5 6 26 Song, Binbin 9 6 5

27 Sridaran, Arun 9 7 4 28 Tangeda, Srujana 9 8 4

29 Vasudevan, Sriram 9 9 2 * NOTE only the negative slew rate is required to satisfy this specification. Grading of problem VI Grade All Common specifications are satisfied

(*1) and the individual specifications are satisfied as follows:

50% 3 specifications are within 10% 30% 2 specifications are within 10% 10% 1 specification is within 10% 0% 0 specification is within 10% *1 If CMR, Avd, and PM are not all satisfied, the above grades are scaled as follows: Number of Specs satisfied

Scaling Factor

3 1 2 2/3 1 1/3 0 0/3 Submission must include the following:

(1) All the calculations used in determining the (W/L) of each transistor, and the value of Rc.

(2) All Pspice netlists and outputs used in all your simulations. (3) Complete the following table: (This is a must, if missing maximum grade for

this problem is 25%)

Opamp parameter

Your Spec Actual Spec

% error (*2)

Avd >=60,000 Avc (*1) CMRR (*1) CMR -4.5<=CMR<=3 PM >=85 SR GB(in MHz) Ro *1 Spec not given. You just provide the actual spec from simulation or computation. %error not required. *2 %error = (Actual Spec – Your Spec)/(Your Spec) * 100