Computer architecture Lecture 7: Control unit. Microoperations Piotr Bilski.

-

Upload

aileen-beasley -

Category

Documents

-

view

222 -

download

4

Transcript of Computer architecture Lecture 7: Control unit. Microoperations Piotr Bilski.

Computer architecture

Lecture 7: Control unit. Microoperations

Piotr Bilski

Tasks of the Control Unit:

• Processor’s state monitoring

• Control of the processor’s work

• Microoperations scheduling

Instruction cycle Instruction cycle Instruction cycle

Fetching Indirect addressing Execution Interrupt

μOPμOP μOP

Microoperations

• Elementarny steps in the instruction cycle

• Every step is basic and its result is small

• Every microoperation takes one time unit

• They exist in all phases of the instruction cycle: fetching, indirect addressing, executing, interrupt

Instruction Fetching Cycle

t1: MAR (PC)

t2: MBR M(MAR)

Processor

MAR

MBR

CU

Memory

Address bus

Control bus

Data bus

PC

IR

PC (PC) + 1

t3: IR (MBR)

Indirect Addressing Cycle

t1: MAR (IR(Address))

t2: MBR M(MAR)

t3: IR(Address) (MBR(Address))

Processor

MAR

MBR

CU

Memory

Address bus

Control bus

Data bus

Interrupt Cycle

t1: MBR (PC)

t2: MAR Address

Processor

MAR

MBR

CU

Memory

Address bus

Control bus

Data bus

PC

PC IHP addresst3: M(MAR) (MBR)

Execution Cycle• The most complicated because of the branches

• Example:

BSA X

t1: MAR (IR(Address))

MBR (PC)

t2: PC (IR(Address))

M() (MBR)

t3: PC (PC) + 1

Register Instruction Cycle Code (ICC)

• Register storing instruction cycle code of the processor’s state, for example:

• 00 – fetching• 01 – indirect addressing• 10 – execution• 11 – interrupt

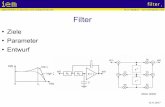

Model of the Control Unit

Status flags

clock

Instruction register

Control Unit

Control signals inside the processor

Control bus

Control Signal Types

• Activating functions of the ALU• Activating data path • Related to the system bus• Controlling signal types is performed by

opening gates between the registers and the memory

• Knowledge about the ICC status is required

Internal Organization of the Processor

t1: MAR (IR(Addr))

t2: MBR M(MAR)

t3: Y (MBR)

t4: Z (AC) + (Y)

t5: AC (Z)

CU IR PC

MAR

MBR

Address lines

Data lines

AC

Y

ALU

Z

Internal bus

Intel 8085 Processor (1977)• Compliant with 8080 processor • Powered by +5V voltage• Structure: CU, PC, A, RA, ALU, RF, RR• Program Counter – 16 bits, address register –

16 bits, instruction register – 8 bits• External stack in RAM• ALU – processing max 2 arguments

8085 Processor Scheme

Examples of the External Signals (Intel 8085)

• Address and data signals– Adresses/data (A0-A7, A8-A15)– Serial input/output data (SID, SOD)

• Control and clock signals– CLK, X1, X2

– Address Latch Enabled (ALE)– IO/M– Read/write control (RD, WR)

• Signals initiated by memory and input/output• Interrupt signals• Processor initialization (RESET)• Power

Implementations of the Control Unit

• Faster (logical circuits)• Complicated• Expensive• Realization:

combinatorial circuit• Used in the RISC

machines

• Slower • Flexible• Cheap• Realization:

microprogram• Used in the CISC

machines

Circuit implementationMicroprogram implementation

Circuit Implementation

Status flags

clock

Instruction register

Control unit

Clock generator

Control signals

Decoder 2 to 4

A

BA B S0 S1 S2 S3

0 0 0 0 0 1

0 1 0 0 1 0

1 0 0 1 0 0

1 1 1 0 0 0

S0

S1

S2

S3

Microprogram Implementation of the Control Unit

• Microprogram determines the logic of the control unit work regime

• Microprogram consists of the microoperations stored in the control memory

• This technique was used for the first time in the System/360 (IBM) computer

Horizontal and Vertical Microoperations

Internal signals controlling the processor

Control signals of the system bus

Microoperation address

Branch condition

Function codes Microoperation addressBranch conditions

Codes instead of the control lines – decoders required

Control Memory Organization

Fetch cycle subroutine

Indirect addressing cycle subroutine

Interrupt cycle subroutine

Execution cycle subroutine

Microprogram Control Unit

Control address register

Control buffer register

Control memory

Logical scheduling circuits

Decoder

Instruction register

Decoder

Read

ALU status flags

Clock

Control signals inside CPU

Control signals of the system bus

Microoperations Sequencing

• Instruction size and time of the address generation

• The next microoperation address is:– Inside instruction register (at the beginning of

the instruction cycle)– In the branch (the most common)– Next in the sequence

Sequencing Methods

• Two address fields

• One address field

• Changing format

Sequencing with Two Address Fields

CAR

Address decoder

Control memory

Branch logi-cal circuits Multiplexer IR

Con-trol Address1 Address2

Status flags

CBR

One Address Field Sequencing

CAR

Address decoder

Control memory

Branch logi-cal circuits Multiplexer IR

Control Address

Status flags

CBR

+1

Changing Format Sequencing

CAR

Address decoder

Control memory

Branch logi-cal circuits Multiplexer IR

Branch field

Status flags

CBR

+1

Gating logical circuits

Whole field Address field

Address Generation

Evident

• Two fields

• Conditional branch

• Uncoditional branch

Non-evident

• Projection

• Addition

• Residual control

Non-Evident Projection: Addition

Address register

Constant part of the addressBits set to determine the address of the next microoperation

Sequencing Microoperations in LSI-11

• 22-bit microoperation

• About 4 KB of the control memory

• Methods of the next address generation:– Next in line– Projection of the operation code– Standard subroutine– Interrupt testing– Branch

Microoperations Execution

• Microoperation cycle consists of the fetching and execution phase

• Execution causes putting on the internal and system bus control signals and determining the next instruction address

• Combination of the control bits related to the microoperation is encoded

Direct Microoperation Encoding

Field Field Field

DecodersDecoders Decoders

Control signals

Indirect Microoperation Encoding

Field Field Field

DecodersDecoders Decoders

Control signals

Decoders

Examples of the Vertical Instructions

0 0 0 0 0 0

0 0 0 0 0 1

0 0 0 0 1 0

0 0 1 0 0 0 0 0

0 0 1 0 0 1 0 0

0 1 1 0 0 0

MBR Register

Register MBR

MAR Register

Read from memory

Write to memory

AC AC + Register

Examples of the Horizontal Instructions

1. Register transfer2. Memory operation3. Sequencing operation4. ALU operation5. Register selection6. Constant

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

1 2 3 4 5 6

LSI-11 Microoperation Format

• Instruction breadth: 22 bits

• Microoperation list is complementary to the machine instruction list

Special functions

Translation Return register loading

Encoded microoperations

4 1 1 16

IBM 3033 Microoperation Format

• Control memory – 4 KB words

• Instructions from the interval 0000-07FF are 108-bit long

• Instructions from the interval 0800-0FFF are 126-bit

• Instructions are horizontal with coding