1Ausgewählte Themen des analogen Schaltungsentwurfs DCAC Ohne RK RK Ω

-

Upload

mirjam-gebauer -

Category

Documents

-

view

109 -

download

2

Transcript of 1Ausgewählte Themen des analogen Schaltungsentwurfs DCAC Ohne RK RK Ω

1 Ausgewählte Themen des analogen Schaltungsentwurfs

DC AC

Ohne RK

RK

inout VRR

RV

21

1

outVinV

1R

2R

)(1

)1()(

12

2

1 tAuDaDa

Dbtu Gout

)()( ssCUsI

Ω

RKA

AAFFA

OL

OLOLF

2

21

1

2112 )(

5.0zT

T

2 Ausgewählte Themen des analogen Schaltungsentwurfs

Testschaltungen für Feedbackanalyse

RKA

AAFFA

OL

OLOLF

2

21

1

AOL1 – Gain am Eingangsnetz AOL2 – aktive Verstärkung

RK FF

T - Schleifenverstärkung

Messpunkt - blau

Testquelle - rot

Kurzschluss

T

AAFFA OLOL

F

1

21

3 Ausgewählte Themen des analogen Schaltungsentwurfs

Ausgangswiderstand

OC

SCOUT T

TRR

1

10

R0 – Ausgangsimpedanz ohne Verstärkung

TOC TSC

Kurzschluss

Kurzschluss

R=?

offene Leitung

Schleifenverstärkungen

4 Ausgewählte Themen des analogen Schaltungsentwurfs

Linearer Spannung-Strom Wandler

T

GG OL

1

mOL gG 1 RgT m

RRg

gG

m

m 1

1

OC

SCDoutout T

TRR

1

1

RrR dsDout RgT mSC 0OCT

)1( RgrRR mdsout

Leerlaufverstärkung 1 Aol1

Leerlaufverstärkung 2 Aol2

Schleifenverstärkung T

Widerstand ohne Verstärkung

Schleifenverstärkung bei kurzgeschlossenen Knoten

Schleifenverstärkung bei offenen Knoten

5 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd||Rds

dmRgA

)1( dmfgIN RgCCC

fdOUT CCC

Cg

Cf

Cd

6 Ausgewählte Themen des analogen Schaltungsentwurfs

Millereffekt

testtest ICD

U1

Uin Uout

testOL

SCintest I

ACDT

TZUU

)1(

11

1

10

C

LCMeter

LCMeter

-A

C

(1+A)C

C

7 Ausgewählte Themen des analogen Schaltungsentwurfs

Aufgabe Rin=?

Cg Cg Cg

Transistor CS Amplifier SF Amplifier

Z=? Z=?

8 Ausgewählte Themen des analogen Schaltungsentwurfs

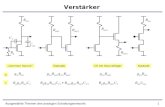

Verstärker mit einem Eingang

„Common Source“ Kaskade CS mit Sourcefolger Kaskode

9 Ausgewählte Themen des analogen Schaltungsentwurfs

Verstärker mit einem Eingang

10 Ausgewählte Themen des analogen Schaltungsentwurfs

Differentieller Verstärker

11 Ausgewählte Themen des analogen Schaltungsentwurfs

Differentieller Verstärker

dssatV

DynamikbereichAusgang

DynamikbereichEingang

12 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd||Rds

dmRgA

)1( dmfgIN RgCCC

fdOUT CCC

Cg

Cf

Cd

13 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

indmout URgU '

UIN

UOUT

)()1( ''1 fdddmfgg CCRRgCCRa

DC Verstärkung

Dominante Zeitkonstante

Wichtige Kapazitäten: Cd – Lastkapazität (groß), Cf – verstärkt durch Millereffekt

Diese Kapazität wird durch Miller-Effekt verstärkt

Rg

Rd

Cd

Cf

Nachteil: Verstärkung hängt vom Lastwiderstand ab

Cg

dsdd RRR ||'

OUTdINg CRCRa '1

14 Ausgewählte Themen des analogen Schaltungsentwurfs

Sourcefolger

UIN

UOUT

Eingang

Ausgang

+

gm UGSCgd

Cgs

Cs Rs‘ = Rs||Rds

Rg

-Eingang Ausgang

Cgs Kapazität zwischen Gate und Source

Cgd Kapazität zwischen Gate und Drain

Cs Summe aller Kapazitäten zwischen Source und Masse

RsRg

15 Ausgewählte Themen des analogen Schaltungsentwurfs

Sourcefolger - Zeitkonstanten

''

'1

11 sm

gsgdg

sm

gsss

Rg

CCR

Rg

CCR

UIN

UOUT

Eingang

Ausgang

Rs

Cgd

Cgs

Cs

ININ

ms

msOUT UU

gR

gRU

'

'

1DC Verstärkung

Dominante Zeitkonstante

Diese Kapazitäten werden durchdie Wirkung des Transistors stark gedämpft

Rg

Der Generator Ig „sieht“ die große Lastkapazität Cs nicht

dssS RRR ||'

16 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskade von 2 „common–sorce“ Verstärkern

UIN

UOUT

AusgangEingang

Rg1

Rd1

Rd2

17 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskade von 2 CS

indmdmout URgRgU 2211DC Verstärkung

Dominante Zeitkonstante

)()1(

)()1(

22222221

11111111

fdddmfgd

fdddmfgg

CCRRgCCR

CCRRgCCR

UIN

UOUT

Cf1

Cf2

Cd2DC Verstärkung ist Produkt von Verstärkungen einzelner Stufen

Die Zeitkonstante ist Summe von der Zeitkonstanten einzelner Stufen

Rg1

Rd1 Rd2

Wichtige Kapazitäten: Cf1, Cf2 – Millereffekt, Cd2 - Lastkapazität

)()1(

)()1(

22222221

11111111

fdddmfgd

fdddmfgg

CCRRgCCR

CCRRgCCR

indmdmout URgRgU 2211

18 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskade von CS und Source-Folger

UIN

UOUT

Ausgang

Eingang

Rg1

Rd1

Rs2

19 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskade von CS und Source-Folger

112'

2

2'

211 1 dmin

sm

smdmout RgU

Rg

RgRgU

UIN

UOUT

Ausgang

Eingang

DC Verstärkung

2'

2

222'

2'

2

22111

11111

1

)1

(

)1(

sm

sgss

sm

gsgdfdd

dmfgg

Rg

CCR

Rg

CCCCR

RgCCR

Dominante Zeitkonstante

Die Lastkapazität wird gedämpft, der Generator „sieht“ die Kapazität nicht

Rg1

Rd1

Rs‘2 DC Verstärkung wie beim common-source Verstärker – aber sie hängt vom Lastwiderstand Rs2 nicht ab. Gut für die Ausgangsverstärker

Cs2Cgs2

Cgd2

Cd1

Cf1

Kleine Kapazitäten

Millereffekt

20 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskade von CS und Source-Folger vs Kaskade von 2 CS

112'

2

2'

211 1 dmin

sm

smdmout RgU

Rg

RgRgU

2'

2

222'

2'

2

22111

11111

1

)1

(

)1(

sm

sgss

sm

gsgdfdd

dmfgg

Rg

CCR

Rg

CCCCR

RgCCR

indmdmout URgRgU 2211

)()1(

)()1(

22222221

11111111

fdddmfgd

fdddmfgg

CCRRgCCR

CCRRgCCR

indmout URgU 11

2

22221

11111111

)(2

)()1(

m

fdfgd

fdddmfgg

g

CCCCR

CCRRgCCR

22/1 dm Rg

2 cs

Cs+sf

kleiner

21 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskode

UIN

UOUT

Ausgang

Eingang

Rg1

Rc1

UIN

UOUT

Rg1

Rc1

Cs2

Cd2

Cg1

Cf1

Cd1

Source und Bulk sind getrennt

22 Ausgewählte Themen des analogen Schaltungsentwurfs

Kaskode

incmout URgU 21

UIN

UOUT

Ausgang

DC Verstärkung

222111

*

1*

1111

)(

)1(

dcgsfdd

dmfgg

CRCCCR

RgCCR

Dominante Zeitkonstante

Rg1

Rc2

Ab hier „sieht“ der common source Verstärker nur noch den kleinen Widerstand R*

d1 ≈ 1/gm2.Das mildert Millereffekt und macht die Kaskode schneller als „common cource“.

Cd2

Schwaches Millereffekt

23 Ausgewählte Themen des analogen Schaltungsentwurfs

Verstärker

„Common Source“ Kaskade CS mit Sourcefolger Kaskode

outmRg 2211 outmoutm RgRg 11 outm Rg outm Rg 1

foutmg CRgR 2221111 foutmoutfoutmg CRgRCRgR foutmg CRgR 11 outoutCR

fC

outR

gR

outC

1outR 2outR 1outR

2outR

outR

V

τ

24 Ausgewählte Themen des analogen Schaltungsentwurfs

Verstärker mit einem Eingang

25 Ausgewählte Themen des analogen Schaltungsentwurfs

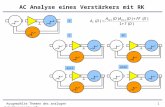

AC Analyse eines Verstärkers mit RK

T

AA

U

UA OLOL

in

outF

1

21

Signaldämpfung am Eingang

RückkopplungAktive Verstärkung

)(1

)()(

DT

DADA OL

F

1

)1()(

212

21

*0

DD

DADA zOL

OL

1

)1()(

212

21

0

DD

DTDT z

Annahme: System zweiter Ordnung

26 Ausgewählte Themen des analogen Schaltungsentwurfs

Testschaltungen für Feedbackanalyse

RKA

AAFFA

OL

OLOLF

2

21

1

AOL1 – Gain am Eingangsnetz AOL2 – aktive Verstärkung

RK FF

T - Schleifenverstärkung

Messpunkt - blau

Testquelle - rot

Kurzschluss

T

AAFFA OLOL

F

1

21

27 Ausgewählte Themen des analogen Schaltungsentwurfs

AC Analyse eines Verstärkers mit RK

111

1

1)(

0

0212

0

21

*

0

0

D

T

TD

T

D

T

ADA

z

zOLF

)(1

)()(

DT

DADA OL

F

28 Ausgewählte Themen des analogen Schaltungsentwurfs

Transistorschaltplan

UIN

UOUT

Rg

Rd

Cd

Cf

Cg

Rf

Feedback

Verstärker

Sensor- Kleinsignalmodell

29 Ausgewählte Themen des analogen Schaltungsentwurfs

Analyse eines Systems mit RK

+

gm UIN

Cf

Cd Rd

Rg -

Eingang

Cg

UIN

Rf

Ausgang

U*IN

PassivesNetzwerk

PassivesNetzwerk

Feedback

Xi Xi*Xs

30 Ausgewählte Themen des analogen Schaltungsentwurfs

Der Schnittpunkt

UIN

UOUT

Rg

Rd

Cd

Cf

Cg

Rf

Der Schnittpunkt befindet sich nach der Gatekapazität!Es wird nur schwer mit SPICE simuliert.

31 Ausgewählte Themen des analogen Schaltungsentwurfs

Schleifenverstärkung

+

gm U*IN

Cf

Cd Rd

Rg -Cg

UIN

Rf

U*IN

PassivesNetzwerk

PassivesNetzwerk

Feedback

Xi Xi*

32 Ausgewählte Themen des analogen Schaltungsentwurfs

Schleifenverstärkung – Zeitkonstante a1

+

gm U*IN

Cf

Cd Rd

Rg -Cg

UIN

Rf

IN

IN

U

UT

*

1

1

12

2

10

DaDa

DbTT

ffddgg RCRCRCa 0001

)(||0dfgg RRRR

)(||0gfdd RRRR

)(||0gdff RRRR

ggfd

dm R

RRR

RgT

0

Die Schleifenverstärkung für niedrige Frequenzen,Leicht herzuleiten nur Strom/Spannungsteiler

Minus Vorzeichen nicht vergessen, T0 muss positiv sein

Methode der Zeitkonstanten

33 Ausgewählte Themen des analogen Schaltungsentwurfs

Zeitkonstanten – die Formel für a2

C1

C2

Ci

Gnn

nn u

DaDaDa

DbDbiu

1...

1...,

12

2

1

nn

nnn RRCCRRCCa 11

012

110

212 ...

CN

Ω

Zur Messung von RN1

34 Ausgewählte Themen des analogen Schaltungsentwurfs

Schleifenverstärkung – Zeitkonstante a2

+

gm U*IN

Cf

Cd Rd

Rg -Cg

UIN

Rf

fd

dfdfg

gfgdg

gdg RRCCRRCCRRCCa 0002 )(||0

dfgg RRRR

)(||0gfdd RRRR

)(||0gdff RRRR

fddg RRR ||

dffg RRR ||

gffd RRR ||

35 Ausgewählte Themen des analogen Schaltungsentwurfs

Schleifenverstärkung – die endgültige Formel

+

gm U*IN

Cf

Cd Rd

Rg -Cg

UIN

Rf

U(t)

1

1

12

2

10

DaDa

DbTT ffddgdf CRCRCRRa )(1

)(2 fdfgdgdf CCCCCCRRa

?1 b

36 Ausgewählte Themen des analogen Schaltungsentwurfs

Nullstelle

+

gm U*IN

Cf

Cd Rd

Rg -Cg

UIN

Rf

uIN(t)=0

)()1()()1( *11

22 tuDbtuDaDa ININ

I(t)=0

Cf

Rf

I(t)=0

IR(t)≠0

IC(t)≠0)()( titi CR

)(1

)(*

tiCs

UtRiU CCRR

)(1

)(*

tiCs

tRi RR

0)()1( * tiRCs R

0)1( *1 sb

1bRC

Dan gilt es auch

Daher, es muss sein:

1* /1 bs )(0)( * tugtu INmIN

*sD

0)1( * RCs

undUIN(t)=0 UOUT(t)=0

tsIN aetu

*

)(*

37 Ausgewählte Themen des analogen Schaltungsentwurfs

Leerlaufverstärkung für niedrige Frequenzen

+

gm U*IN

Rd

Rg -

UIN

Rf

PassivesNetzwerk

PassivesNetzwerk

Feedback

Xi Xi*

PassivesNetzwerk

PassivesNetzwerk

Feedback

Xi Xi*Xs

Xs

Signaldämpfung

Verstärkung

gm U*IN

Rd

Rg

U*IN

)(||)||( gfdmfgDCOL RRRgRRA

Rf

fDCOL

DCF RT

AA

01Leerlaufverstärkung

Verstärkung mit RK (für niedrige Frequenzen)

38 Ausgewählte Themen des analogen Schaltungsentwurfs

Verstärkung mit RK – die Formel

111

1

1)(

0

0212

0

210

D

T

TD

TT

ADA

z

OLF

11

)()(

1

)(1

)(2

DRg

CRRgRCRRCRD

Rg

CCCCCCRRRDA

dm

ffdmfgdfdd

dm

dfdgfgdffF

2112 )(

5.0zT

T

225.0)( ffdmdfdgfgdf CRRgCCCCCCRR

fm

dfdgfgf Rg

CCCCCCC

5.02

Die Formel von Folie 20

Wir setzen die Zeitkonstanten ein:

Die Bedingung für die schnelle und genaue Signalantwort (ohne Überschwinger)

Der Feedbackkondensator macht die Schaltung „Stabil“.

Gm soll groß sein So größer Rf ist desto stabiler Antwort Solche Methode für Stabilisierung nennt

man Pole Splitting

39 Ausgewählte Themen des analogen Schaltungsentwurfs

Widerstand als Last

+

>Vth

-

+

-

>Vth

+

<Vth

A BC

A B C

A – Transistor sperrt

B – Transistor im Sättigung

B – Transistor im linearen Bereich

-

Vout

Vin

40 Ausgewählte Themen des analogen Schaltungsentwurfs

Widerstand als Last

Ids

Vds

sat

sat

I

LE

Vdssat

22 thgs

oxdssat VV

L

WCI

thgsdssat VVV

ds

satds I

LER

thgsoxgs

dssatm VV

L

WC

dV

dIg

2dssatm

ds

VgI

dssat

dsm V

Ig

2

Vgs1

Vgs2

Vgs3

2

2 dssatox

dssat VL

WCI

Vgs<Vt

41 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromquelle als Last

V

IVin

Vout

dssatLVV min

dsLmRgA

dsLmLmmL

mLdsLm Rg

I

Vg

g

gRgA min

2

1

TL

42 Ausgewählte Themen des analogen Schaltungsentwurfs

Widerstand als Last

I

VR

I

VgRgA mm

I

V

R

Vin

Vout

dsLmLm RgI

VgA min

2

1

Stromquelle als Last

Widerstand als Last

V

I

TL

43 Ausgewählte Themen des analogen Schaltungsentwurfs

Stabilisierung

Vin

Vout

Vin=Vout

Arbeitspunkt

44 Ausgewählte Themen des analogen Schaltungsentwurfs

Diode als Last

22 thin

InIn

oxds VV

L

WCI

22 thout

LL

oxds VV

L

WCI

LLox

InInoxthinthout LWC

LWCVVVV

/

/

Vin

Vout Vout=vdd

A: Diode als NMOS B: Diode als PMOS

45 Ausgewählte Themen des analogen Schaltungsentwurfs

Linearer Spannung-Strom Wandler

22 thin

oxout VV

L

WCI

Versuchen wir die Kennlinie mithilfe einer Rückkopplung zu linearisieren

46 Ausgewählte Themen des analogen Schaltungsentwurfs

Linearer Spannung-Strom Wandler

T

GG OL

1

mOL gG 1 RgT m

RRg

gG

m

m 1

1

OC

SCDoutout T

TRR

1

1

RrR dsDout RgT mSC 0OCT

)1( RgrRR mdsout

Leerlaufverstärkung 1 Aol1

Leerlaufverstärkung 2 Aol2

Schleifenverstärkung T

Widerstand ohne Verstärkung

Schleifenverstärkung bei kurzgeschlossenen Knoten

Schleifenverstärkung bei offenen Knoten

47 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromspiegel

IREF

)(UfI )(1 IfU

Biasspannung wird mit dem Spannungsteiler erzeugt. Der Biasstrom ist abhängig von Temperatur und Schwellespannung.

StromspiegelDer Biasstrom ist gut definiert

48 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromspiegel - Parameter

mdssat g

IVV

2min

I

LErR satdsout

22 thgs

ox VVL

WCI

2

2 dssatox VI

WCL

2

2

I

VWECR dssatsatox

out

49 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromspiegel mit Kaskode

mdssat g

IV

2

cascmcascdssat g

IV

2

dscascmcascdsOC

SCDoutout rgr

T

TRR

1

1

50 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromspiegel mit Kaskode

mdssat g

IV

2

cascmcascdssat g

IV

2

mdssat g

IVV

42min0

dsmdsout rgrR

dscascmcascdsout rgrR

dsmsat

out rgI

LER

2

0

2

I

VWECR satox

out

dsm

satoxout rg

I

VWECR

2

0

24

1

0V

Ohne Kaskode Mit Kaskode

51 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromspiegel mit Kaskode

thcascdssat VV

DC Ströme sind nicht gleich DC Ströme sind gleich

52 Ausgewählte Themen des analogen Schaltungsentwurfs

Stromspiegel AC Parameter

+

gm UIN-

UIN

rds

mmdsIN ggrR /1/1||

1/

11)()(

DgCgDIDU

mgesmING

1/)()()(

DgC

MDIgDMUDI

mgesINmGOUT

M

dbgsges CCMC 1

dbC

gdC

gsC

GU

INI

INI

GU

Nullimpedanzen

54 Ausgewählte Themen des analogen Schaltungsentwurfs

Tiefpass 1. Ordnung (Beispiel)

)(1

1)(

12 tAu

Datu GC

+

uG = h(t)C1

R1

+

dt

tduCti

)()(

+

55 Ausgewählte Themen des analogen Schaltungsentwurfs

Tiefpass 1. Ordnung (Beispiel)

)(1

1)(

12 tAu

Datu GC

+

C1

R1

+

DC

0

dt

tduCti

)()(

+

AAuu GC

)(10

1)(2

1)(2 Cu

uG = h(t)

1)(2 Cu A1

56 Ausgewählte Themen des analogen Schaltungsentwurfs

Tiefpass 1. Ordnung (Beispiel)

)(1

1)(

12 tu

Datu GC

+

C1

R1

+

)(1

1)(

12 s

sas GC uu

*)(,01*:* 21 ssass Cu

uG = h(t)

dt

tduCti

)()(

+

)()( ssCs UI

)()( tCDuti

*/11 sa

57 Ausgewählte Themen des analogen Schaltungsentwurfs

Tiefpass 1. Ordnung (Beispiel)

)(1

1)(

12 tu

Datu GC

C1

R1

+

)(1

1)(

12 s

sas GC uu

*)(,01*:* 21 ssass Cu

Ω

Req(s*) = 0

*/11 sa

uG = h(t)

dt

tduCti

)()(

+

)()( ssCs UI

)()( tCDuti

58 Ausgewählte Themen des analogen Schaltungsentwurfs

Tiefpass 1. Ordnung (Beispiel)

0*

1*)(

11

CsRsReq

C1

R1

+

Ω

Req(s*) = 0

0*

1*

1

11

Cs

CRs1*: 11 CRsCG

111 CRa

)(1

1)(

112 sA

sCRs GC uu

59 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

60 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

+

gm UIN

Cg Summe aller Kapazitäten zwischen Gate und Source

Cf

Cd Rd||Rds

Rg -

Eingang Ausgang

Cg

Cf Summe aller Kapazitäten zwischen Gate und Drain

Cd Summe aller Kapazitäten zwischen Drain und Masse

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd Rds

61 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg=10K

Rd

Cg=1p

Cf

Cd=1p Rds

A=200

Cf, gm, Rd = ?

Response speed - Optimieren

62 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd Uout(t)

Iin(t)

)()()( tututudfg CCC

63 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd

)(1

)1()(

12

2

1 tAuDaDa

Dbtu Gout

64 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

1100

)10()(

12

1

A

aa

buout

gdm RRgA

65 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd

)(1

)1()(

12

2

1 tuDaDa

DbRgRtu Gdmgout

66 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd

0*)(,01*:* 1 ssbss outu

)(1

)1()(

12

2

1 ssasa

sbRgRs dmgout Guu

67 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd

in1 vi fCs*

in1 vi mg

fmfm CgsCsg /*,*

mf gCb /1

0*)(,01*:* 1 ssbss outu

)(1

)1()(

12

2

1 ssasa

sbRgRs dmgout Guu

0*)( soutu

1i

68 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

Ausgang

Rg

Rd

Cg

Cf

Cd

*)(,01**:* 12

2 ssasass outu

)(1

)11(

)(1

22

ssasa

g

C

RgRs m

f

dmgout Guu

69 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Eingang

RgRdCg

Cf

Cd

0)( sGin

0)(*1

sGCsR

G eqgg

in

*)(,01**:* 12

2 ssasass outu

)(1

)11(

)(1

22

ssasa

g

C

RgRs m

f

dmgout Guu

0)( sGin

70 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Rd

Cf

Cd)(sZeq

71 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Rd

Cf

CdOC

SCeqeq T

TZsZ

1

1)( 0

dd

dfeq CsR

RsCZ

1

/10

72 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

Rd

Cf

Cd

OC

SCeqeq T

TZsZ

1

1)( 0

)1(

)(1

1

10

ddf

fdd

dd

d

feq CsRsC

CCsR

CsR

R

sCZ

0,1

scdd

dmOC T

CsR

RgT

dmdd

dd

ddf

dfdeq RgCsR

CsR

CsRsC

CCsRZ

1

1

)1(

)(1

)1(

)(1

dmddf

dfdeq RgCsRsC

CCsRZ

73 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

0*)(*1

sGCsR eqg

g

dmdd

dd

ddf

dfdeq RgCsR

CsR

CsRsC

CCsRZ

1

1

)1(

)(1

0*)(*1

sGR

CRseq

g

gg

0)(1

)1(*1

dfd

dmddf

g

gg

CCsR

RgCsRsC

R

CRs

01)))1(()(()(2 gdmfgdfddfdgfgdg CRgCRCCRsCCCCCCRRs

CgRg

Geq

74 Ausgewählte Themen des analogen Schaltungsentwurfs

„Common-Source“ Verstärker

01)))1(()(()(2 gdmfgdfddfdgfgdg CRgCRCCRsCCCCCCRRs

1)))1(()(()(

)/1(2

gdmfgdfddfdgfgdg

mfgdm

CRgCRCCRsCCCCCCRRs

gsCRRgEingang

Ausgang

Rg

Rd||Rds

Cg

Cf

Cd

)(1

)11(

)(1

22

ssasa

g

C

RgRs m

f

dmgout Guu

75 Ausgewählte Themen des analogen Schaltungsentwurfs

Verstärkung mit RK – die Formel

1)))1(()(()(

)()/1()(

2

gdmfgdfddfdgfgdg

mfgdmout CRgCRCCRsCCCCCCRRs

sgsCRRgs Giu

76 Ausgewählte Themen des analogen Schaltungsentwurfs

Verstärkung mit RK – die Formel

2112 )(

5.0zT

T

225.0)( fdgmdfdgfgdg CRRgCCCCCCRR

dm

dfdgfgf Rg

CCCCCCC

5.02

Bedingung für schnelle Signalantwort ohne Überschwinger

1)))1(()(()(

)/1(2

gdmfgdfddfdgfgdg

mfgdm

CRgCRCCRsCCCCCCRRs

gsCRRg

fFCpF

C ff 100100

)1( 22

nsCRRg fgdm 200~1

nsns 5.0200200

5.0~2

nsgC mf 5.0/ mgs 200

77 Ausgewählte Themen des analogen Schaltungsentwurfs

Pole Splitting

1)1()(

)/1()(

2

sRgCCRCCRsCCCCCCRR

sgCRgRsA

dmfggfdddfdgfgdg

mfdmg

11

)1()(

21

ss

sRgRsA z

dmg

1

1)(

2

sCRCRsCCRRRgRsA

ggdddgdgdmg

11

1)(

sCRsCRRgRsA

ggdddmg 1

)/1()(

2*

sRgRCsCRR

sgCRgRsA

dmgfdg

mfdmg

0fC

78 Ausgewählte Themen des analogen Schaltungsentwurfs

Pole Splitting

11

1)(

sCRsCRRgRsA

ggdddmg

1

)/1()(

2*

sRgRCsCRR

sgCRgRsA

dmgfdg

mfdmg

ddpggp CRCR 21 ,

fm

fggdfdfdmg Cg

CCCCCCCRgR

21 ,

1/τ

τp1τp2

Cf

ggCR/1 ddCR/1

fgmg CRgR/1 dg

m

CC

g

79 Ausgewählte Themen des analogen Schaltungsentwurfs

Millereffekt

testtest ICD

U1

Uin Uout

testOL

SCintest I

ACDT

TZUU

)1(

11

1

10

C

LCMeter

LCMeter

-A

C

(1+A)C

C

80 Ausgewählte Themen des analogen Schaltungsentwurfs

Beispiel (2)

R1

R2

C1

C2

U0h(t)

Jetzt ist die Schaltung in Ordnung (zwei unabhängige Kondensatoren)

Rx

81 Ausgewählte Themen des analogen Schaltungsentwurfs

Beispiel (2)

GC uDaDa

Dbu

1

1

12

2

12

220

110

1 CRCRa

2211211 )||()||( CRRCRRa

))(()( 2/

121 CoeCothtu at

C

Die Differentialgleichung hat die Form

Es gilt (nach der Formel von Folie 39 und 40):

R1

R2

C1

C2

U0h(t)Rx

wir benutzten Rx = 0!

02121

10

2 CCRRa

(1)

Lösung der Gleichung (1)

220

110

1 CRCRa

Finden wir Co1 und Co2…

82 Ausgewählte Themen des analogen Schaltungsentwurfs

Anfangsbedingung (1)

R1

R2

C1

C2

U0h(t)

t = 0+

∞

∞

021

10

12

22 /1/1

/1)0( U

CC

CU

DCDC

DCuC

Großer Strom

83 Ausgewählte Themen des analogen Schaltungsentwurfs

Endzustand

R1

R2

U0h(t)

t = ∞

021

22 )0( U

RR

RuC

uC

t

021

2 URR

R

021

1 UCC

C

))||)(/(( 2121 RRCCte

84 Ausgewählte Themen des analogen Schaltungsentwurfs

Beispiel (2)

R1

R2

C1

C2

U0h(t)

Nur ein unabhängiger Kondensator! – fügen wir zusätzlichen Widerstand Rx. Es gilt: Rx -> 0!!!

85 Ausgewählte Themen des analogen Schaltungsentwurfs

Beispiel (2)

R1

R2

C1

C2

U0h(t)

Jetzt ist die Schaltung in Ordnung (zwei unabhängige Kondensatoren)

Rx

86 Ausgewählte Themen des analogen Schaltungsentwurfs

Beispiel (2)

GC uDaDa

Dbu

1

1

12

2

12

220

110

1 CRCRa

2211211 )||()||( CRRCRRa

))(()( 2/

121 CoeCothtu at

C

Die Differentialgleichung hat die Form

Es gilt (nach der Formel von Folie 39 und 40):

R1

R2

C1

C2

U0h(t)Rx

wir benutzten Rx = 0!

02121

10

2 CCRRa

(1)

Lösung der Gleichung (1)

220

110

1 CRCRa

Finden wir Co1 und Co2…

87 Ausgewählte Themen des analogen Schaltungsentwurfs

Anfangsbedingung (1)

R1

R2

C1

C2

U0h(t)

t = 0+

∞

∞

021

10

12

22 /1/1

/1)0( U

CC

CU

DCDC

DCuC

Großer Strom

88 Ausgewählte Themen des analogen Schaltungsentwurfs

Endzustand

R1

R2

U0h(t)

t = ∞

021

22 )0( U

RR

RuC

uC

t

021

2 URR

R

021

1 UCC

C

))||)(/(( 2121 RRCCte

![edu.semgu.kzedu.semgu.kz/ebook/rk/3581/1265fdc6-82b3-11e5-8348... · Web view$$$ 1 A. Indicate the backlingual sound. A. [k] B. [r] C. [s] D. [m] E. [ t] $$$ 2 B. Indicate bilabial,](https://static.fdocument.org/doc/165x107/5aacc2567f8b9a8f498d7097/edusemgukzedusemgukzebookrk35811265fdc6-82b3-11e5-8348web-view-1-a.jpg)