SD-PXE-AOU-H0001 2-Channel, 500-MSPS, 16-Bit, … 2-Channel, 500-MSPS, 16-Bit, FPGA-Based AWG /...

Transcript of SD-PXE-AOU-H0001 2-Channel, 500-MSPS, 16-Bit, … 2-Channel, 500-MSPS, 16-Bit, FPGA-Based AWG /...

SD-PXE-AOU-H0001

2-Channel, 500-MSPS, 16-Bit, FPGA-Based AWG / Vector Signal Generator Module

Features

• 2 analog output channels

• 500 MSPS per channel, 200 MHz bandwidth

• 16-bits resolution (∼ 45.8 μV @ ±1.5 V output range)

• Embedded AWGs and Function Generators:

• 45-bit frequency resolution (∼ 5.68 μHz)• 24-bit phase resolution (∼ 21.5 μdeg)

• Ultra-flexible modulation capabilities:

• AM, FM, PM, ASK, FSK, PSK, IQ, QAM, CDMA, etc.• Modulating signals generated with the AWGs

• 4 MB, 128 MB or 1GB of waveform RAM

• Mechanical/Interface:

• 1 slot 3U: PXI Express or CompactPCI Express• 350 MB/s (2.8 Gbps) transfer speed: PCIe x2• Independent DMA channels per output channel

• Software front panels with Signadyne VirtualKnob

• Software programming (VI):

• Any programming language: C, C++, LabVIEW, C#,MATLAB, Mathematica, Visual Basic, Python, etc.

• Hardware programming (HVI) using ProcessFlow:

• User-friendly flowchart-style programming interface• Ultra-fast hard real-time processing & decision making• Built-in inter-module synchronization & data exchange• Completely robust, no OS & PC-independent execution• Signadyne FPGA-based algorithms: FIR, PID, FFT, etc.• Custom FPGA-based algorithms (VHDL/Simulink):

• Xilinx Virtex-5 SX95T FPGA

Applications

• General purpose analog output

• RF / arbitrary waveform generation

• Telecom transmitter

• Software-Defined Radio (SDR)

• Hardware-In-the-Loop (HIL) testing

• High performance sequencing / process control

• ATE (Automated Test Equipment)

• R&D Equipment

• Rugged Embedded COTS Equipment (OEM)

Industries

• General electronics & telecom

• Aerospace & defense

• Industrial Machinery

• Scientific research

• Medical devices

• Automotive

• Transportation

General Description

The SD-PXE-AOU-H0001 is a high performance PXI Express module with 2 analog outputs. It includes embedded ArbitraryWaveform Generators (AWGs), Function Generators (FG) and modulators, converting the module into a powerful ready-to-use Vector Signal Generator. The SD-PXE-AOU-H0001 is capable of generating any standard waveform (sinusoidal,triangular, square, DC voltages) or any arbitrary waveform defined by the user and stored in its onboard RAM. Using theembedded modulators, the output channels can be modulated in phase, frequency, amplitude or IQ in order to create anyexisting analog or digital modulation.

The SD-PXE-AOU-H0001 can be controlled like a turnkey workbench instrument using the intuitive software front pan-els provided by Signadyne VirtualKnob [1]. For user-defined operation, the module can be controlled by software (VirtualInstrumentation) with Signadyne Programming Libraries [2], or can be hardware-programmed (Hard Virtual Instrumen-tation) using Signadyne ProcessFlow [3], without any knowledge of FPGA technology. For experienced users, customFPGA-based processing can be implemented with MATLAB/Simulink or VHDL code.

Rev. 1.4 (May 30, 2013)Product specifications are subject to change without notice.

c© 2013 Signadyne. All rights reserved.

SD-PXE-AOU-H0001

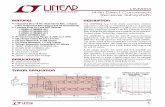

Functional Block Diagram

Figure 1: SD-PXE-AOU-H0001 functional block diagram

Ordering Information

Product Number Description FPGA RAM (MB)

Standard Configuration

SD-PXE-AOU-H0001 2-Ch, 500-MSPS, 16-Bit, FPGA, Analog Out PXIe Virtex-5 SX95T 4

Memory Upgrades

SD-PXE-AOU-U0001-128 Upgrade to 128 MB RAM for SD-PXE-AOU-H0001

SD-PXE-AOU-U0001-1G Upgrade to 1 GB RAM for SD-PXE-AOU-H0001

Related Products

Product Number Description

SD-PXE-AOU-H0002 4 Ch, 500 MSPS, 200 MHz [4]

SD-PXE-AOU-H0003 2 Ch, 1 GSPS, 400 MHz [5]

SD-PXE-AOU-H0004 4 Ch, 1 GSPS, 400 MHz [6]

SD-SOF-LIB-WIN Programming Libraries [2]

SD-SOF-VKN-WIN Signadyne VirtualKnob [1]

SD-SOF-PFL-WIN Signadyne ProcessFlow [3]

Rev. 1.4 (May 30, 2013)Product specifications are subject to change without notice.

c© 2013 Signadyne. All rights reserved.

SD-PXE-AOU-H0001

Specifications

Parameter Min Typ Max Units Comments

General

Analog Channels 2 O

Reference Clock 1 O Reference clock output

External Trigger 1 I/O Configurable operation

Arbitrary Waveform Generators 2 Blocks Available for carriers and modulating signals

Analog Outputs

Voltage -1.5 1.5 V On a 50 Ω load

Voltage Resolution 16 Bits ∼ 45.8 μV

Source Impedance 50 Ω

Sampling Rate 500 MSPS

Bandwidth 200 MHz Limited by a reconstruction filter

Reference Clock Output

Voltage 800 mVpp On a 50 Ω load

Power 2 dBm On a 50 Ω load

Source Impedance 50 Ω AC coupled

Frequency 10 or 100 MHz Generated from the internal clock. User se-lectable

Trigger I/O

VIH 2 5 V

VIL 0 0.8 V

VOH 2.4 3.3 V On a high Z load

VOL 0 0.5 V On a high Z load

Input Impedance 10 KΩ

Source Impedance TTL −

Output Speed 500 Mbps

Onboard Memory

Memory 4 1024 MBytes Product dependent, see Ordering Info. onpage 2

Points 2 512 MPoints Shared by all the channels

Sustainable Throughput 3000 MPoints/s Shared by all the channels

System Bus

Slots 1 Slot PXI Express or CompactPCI Express com-patible

PCI Express Link 1 2 4 Lanes Automatic negotiation, chassis dependent

PCI Express Speed 200 350 350 MBytes/s Automatic negotiation, chassis dependent

Sustainable Throughput 100 170 170 MPoints/s Automatic negotiation, chassis dependent

Internal Clock

Accuracy and Stability 100 ppm Chassis dependent. This value correspondsto a chassis that fulfils the PXI Expressspecifications

Power and Temperature

3.3 V Power Supply (PXIe) 1.5 A ∼ 5 W

12 V Power Supply (PXIe) 2 A ∼ 24 W

Operating Temperature -20 +55 oC In a standard chassis with forced ventilation

Rev. 1.4 (May 30, 2013) 3 / 73

SD-PXE-AOU-H0001

Specifications

Parameter Min Typ Max Units Comments

AC Performance

Frequency Resolution 45 Bits ∼ 5.68 μHz

Phase Resolution 24 Bits ∼ 21.5 μdeg

SFDR (Spurious-Free Dynamic Range) Vout = 1 Vpp (4 dBm). Measured from DCto 500 MHz

fout = 10 MHz 60 63 dBc

fout = 40 MHz 60 63 dBc

fout = 80 MHz 61 64 dBc

fout = 120 MHz 66 69 dBc

fout = 160 MHz 64 67 dBc

fout = 200 MHz 60 63 dBc

Crosstalk (Adjacent Channels)

fout = 10 MHz <-105 -105 dB

fout = 40 MHz -85 -82 dB

fout = 80 MHz -75 -72 dB

fout = 120 MHz -88 -85 dB

fout = 160 MHz -73 -70 dB

fout = 200 MHz -85 -82 dB

Crosstalk (Non-adjacent Channels)

fout = 10 MHz <-105 -105 dB

fout = 40 MHz -86 -83 dB

fout = 80 MHz -78 -75 dB

fout = 120 MHz <-105 -105 dB

fout = 160 MHz -92 -89 dB

fout = 200 MHz -100 -97 dB

Average Noise Density -144 -140 dBm/Hz

4 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

Typical AC Performance

Figure 2: Single-tone spectrum @ fout = 10 MHz

Figure 3: Single-tone spectrum @ fout = 80 MHz

Figure 4: Single-tone spectrum @ fout = 160 MHz

Figure 5: Single-tone spectrum @ fout = 40 MHz

Figure 6: Single-tone spectrum @ fout = 120 MHz

Figure 7: Single-tone spectrum @ fout = 200 MHz

Rev. 1.4 (May 30, 2013) 5 / 73

SD-PXE-AOU-H0001

Interface

Connector Signal Name Direction Connector Type Description

0 TRG I/O SMA Digital trigger input or output

1 CLK O SMA Reference clock output

2 CH 0 O SMA Analog output channel 0

3 CH 1 O SMA Analog output channel 1

Figure 8: SD-PXE-AOU-H0001 front panel

6 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

2-Channel, 500-MSPS, 16-Bit, FPGA-Based AWG / Vector Signal Generator Module

Contents

1 Theory of Operation 91.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91.2 Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.2.1 Standard Waveform Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101.2.2 Arbitrary Waveform Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.2.3 Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151.2.4 Amplitude and DC Offset Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.3 Signal Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171.3.1 Angle Modulation (Frequency and Phase) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171.3.2 Amplitude Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191.3.3 IQ Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.4 Clock and Trigger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231.4.1 Clock System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231.4.2 Trigger I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.5 Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241.5.1 Ready-to-use Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241.5.2 User-defined Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2 VirtualKnob Front Panel 292.0.3 Front Panel Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.1 Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302.1.1 Arbitrary Waveform Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.2 Signal Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3 VI / HVI Programming 323.1 VI Programming Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323.2 HVI Programming Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333.3 SD-AOU Class Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.3.1 channelWaveShape . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343.3.2 channelFrequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 353.3.3 channelPhase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 363.3.4 channelPhaseReset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373.3.5 channelAmplitude . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383.3.6 channelOffset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393.3.7 modulationAngleConfig . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403.3.8 modulationAmplitudeConfig . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413.3.9 modulationIQconfig . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 423.3.10 clockIOconfig . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433.3.11 triggerIOdirection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 443.3.12 triggerIOwrite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 453.3.13 triggerIOread . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 463.3.14 waveformLoad . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 473.3.15 waveformFlush . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 483.3.16 AWG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493.3.17 AWGqueueWaveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513.3.18 AWGflush . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 523.3.19 AWGstart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 533.3.20 AWGstartMultiple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543.3.21 AWGpause . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 553.3.22 AWGpauseMultiple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 563.3.23 AWGresume . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 573.3.24 AWGresumeMultiple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 583.3.25 AWGstop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 593.3.26 AWGstopMultiple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Rev. 1.4 (May 30, 2013) 7 / 73

SD-PXE-AOU-H0001

3.3.27 AWGtriggerExternalConfig . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 613.3.28 AWGtrigger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 623.3.29 AWGtriggerMultiple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 633.3.30 MathAssign (D=S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 643.3.31 MathArithmetics (R=A[+-*/]B) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 653.3.32 MathMultAcc (R=A[+-]B[*/]C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 663.3.33 open . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 673.3.34 close . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.4 SD-Wave Class Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 693.4.1 new . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 693.4.2 delete . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

3.5 Error Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

8 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1 Theory of Operation

1.1 Overview

The SD-PXE-AOU-H0001 has a very flexible and powerful output structure that allows the user to create complex wave-forms.

Figure 9: SD-PXE-AOU-H0001 functional block diagram. All channels have identical output structure.

As shown in Figure 10 on the following page, the SD-PXE-AOU-H0001 includes embedded Arbitrary Waveform Gener-ators (AWGs), Function Generators (FG) and modulators, converting the module into a powerful ready-to-use Vector SignalGenerator. The SD-PXE-AOU-H0001 is capable of generating any standard waveform (sinusoidal, triangular, square, DCvoltages) or any arbitrary waveform defined by the user and stored in its onboard RAM. Using the embedded modulators,the output channels can be modulated in phase, frequency, amplitude or IQ in order to create any existing analog or digitalmodulation.

Rev. 1.4 (May 30, 2013) 9 / 73

SD-PXE-AOU-H0001

1.2 Signal Generation

1.2.1 Standard Waveform Generation

Each output channel has a dedicated Function Generator (FG) which generates basic periodic signals. The FG is com-monly used to generate the RF carrier in modulation schemes.

Figure 10: The Function Generator within the SD-PXE-AOU-H0001 functional block diagram

Specifications

Parameter Min Typ Max Units Comments

General Specifications

Waveform Types 4 - Sinusoidal, triangular, square and DC

Frequency Range 0 200 MHz

Frequency Resolution 45 Bits ∼ 5.68 μHz

Phase Range 0 360 Deg

Phase Resolution 24 Bits ∼ 21.5 μdeg

Timing Specifications

Waveshape Change Latency 100 ns Using HVI Technology (Section 1.5.2 on page 25)

Waveshape Change Rate 10 ns Using HVI Technology (Section 1.5.2 on page 25)

Frequency Change Latency 120 ns Using HVI Technology (Section 1.5.2 on page 25)

Frequency Change Rate 10 ns Using HVI Technology (Section 1.5.2 on page 25)

Phase Change Latency 120 ns Using HVI Technology (Section 1.5.2 on page 25)

Phase Change Rate 10 ns Using HVI Technology (Section 1.5.2 on page 25)

Table 1: SD-PXE-AOU-H0001 Function Generators specifications

NOTE:

Waveform harmonics: Non-sinusoidal wave shapes (triangular, square, etc.) have high frequency components thatmay fall outside the bandwidth of the reconstruction filter if the fundamental frequency is too high. In this situation, theoutput analog signal may suffer some distortion due to the missing harmonics, becoming a sinusoidal as the fundamen-tal frequency approaches the cutoff frequency of the filter.

10 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

ADVANCED:

Phase coherent vs. phase continuous: Changes in the output signal are always phase continuous, not phasecoherent. Therefore, when, for example, the frequency is changed from freq1 to freq2 and changed back to freq1,the phase will not be the initial one. To achieve phase coherent behaviour, the channel accumulated phase can bereset (function channelPhaseReset, Section 3.3.4 on page 37). In addition, in HVI operation (Section 1.5 on page 24)the execution time is deterministic, which allows the user to calculate the new phase and adjust it after any frequencychange.

NOTE:

FGs vs AWGs: When the generation of periodic signals is needed, an FG has many advantages over a pure AWGsolution:

• The FG does not use onboard RAM.

• The waveshape, the frequency and the phase can be changed in real time without having to modify a staticwaveform loaded in memory.

• Achieving the same precision in frequency and phase with a pure AWG solution requires a prohibited amount ofmemory.

Programming Information

Function Comments Details

channelWaveShape It selects the output signal Section 1.2.3 on page 15 and Section 3.3.1 on page 34

channelFrequency It sets the frequency of the FG Section 3.3.2 on page 35

channelPhase It sets the phase of the FG Section 3.3.3 on page 36

channelPhaseReset It resets the accumulated phase Section 3.3.4 on page 37

Table 2: Programming functions related to the Function Generators

Rev. 1.4 (May 30, 2013) 11 / 73

SD-PXE-AOU-H0001

1.2.2 Arbitrary Waveform Generation

An Arbitrary Waveform Generator (AWG) is a powerful and flexible block designed to generate arbitrary analog waveforms(Figure 11). The number of AWGs available in the SD-PXE-AOU-H0001 is shown in Specifications on Page 3.

Figure 11: Arbitrary Waveform Generators (AWGs) in the SD-PXE-AOU-H0001

Each AWG has a queue system that allows the user to configure simple generation sequences, choosing many param-eters such as the trigger method (Table 3 on page 14), the start delay, the number of cycles, etc. Figure 12 shows somegeneration examples.

Figure 12: Examples of the AWGs queue configuration

12 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

TIP:

HVI Generation Sequences: The queue system of the Arbitrary Waveform Generators (AWGs) provides a way tocreate simple generation sequences. For more complex sequences, the best solution is the use of a Hard VirtualInstrument (HVI) programmed with Signadyne ProcessFlow [3]. HVIs are time deterministic with nanosecond resolution(Section 1.5 on page 24), and ProcessFlow provides a user-friendly flowchart programming environment.

Arbitrary waveform generation can performed using two methods:

a) AWG function: This function provides a one step solution to load, queue and run a single waveform directly from afile or an array in memory, as shown in Figure 11 on the facing page.

b) Step by step programming: AWG simplifies the setup of a single waveform, but does not allow the user to controlimportant aspects of the waveform generation:

• The precise moment when waveforms are transferred from file to the PC RAM and to the onboard RAM. Thismay be important for long waveforms and time-critical applications.

• The possibility to have a variety of waveforms in the PC RAM or in the onboard RAM in order to queue themrepeatedly in the AWGs in an efficient way.

• The possibility to prepare the AWG queue with multiple waveforms in advance before starting the generation.This is important to create more complex generation sequences and control the start time precisely (Figure 12on the preceding page).

Signadyne Programming Libraries allow the user to control every aspect of the arbitrary waveform generation (Fig-ure 13):

1) Create waveforms in the PC RAM with the SD-Wave Class (function New).2) Transfer the waveforms to the onboard RAM with waveformLoad.3) Queue the waveforms in any AWG to create the desired generation pattern (function AWGqueueWaveform).4) Start the generation with AWGstart and provide triggers if required.

Figure 13: Process to prepare and run arbitrary waveforms

TIP:

Pausing and Resuming an AWG: The function AWGpause pauses the AWG operation, leaving the last waveform pointat the output. The waveform generation can be resumed calling AWGresume.

Note: After a call to AWG, the selected AWG is running, because this function performs an AWGstart automatically.

Prescaler: Each queued waveform can have a sampling clock prescaler associated with it. This prescaler divides theeffective waveform sampling rate providing a way to reduce waveform sizes.

ADVANCED:

Prescaler and aliasing: Note that reducing the effective sampling rate produces aliasing inside the reconstruction filterbandwidth. Therefore, this unfiltered alias appears at the output.

Rev. 1.4 (May 30, 2013) 13 / 73

SD-PXE-AOU-H0001

Function triggerMode (const & value) Trigger Type Description

Auto AUTOTRIG 0 (default) Hardware Triggers are generated continuously in an automaticway

VI/HVITrigger

VIHVITRIG 1 Software (VI)Hardware (HVI)

The AWG is triggered by the function AWGtrigger(Section 3.3.28 on page 62) provided that the AWG isrunning. AWGtrigger can be executed from a VI or anHVI (see HVI and VI details, Section 1.5.2 on page 25)

ExternalTrigger

EXTTRIG 2 Hardware The AWG waits for an external trigger (Table 4)

Table 3: Trigger methods for the waveforms queued in an AWG (function AWG, Section 3.3.16 on page 49, or AWGqueue-Waveform, Section 3.3.17 on page 51)

Programming Definitions

Waveform Description Name Value

External Trigger The external trigger is the TRG connector of the module TRIG EXTERNAL 0

PXI Trigger The external trigger is a PXI trigger line TRIG PXI 4000

Table 4: External trigger source for the AWGs (parameter externalSource in function AWGtriggerExternalConfig, Sec-tion 3.3.27 on page 61)

Programming Definitions

Waveform Description Name Value

Active High Trigger is active when it is at level high TRIG HIGH 1

Active Low Trigger is active when it is at level Low TRIG LOW 2

Rising Edge Trigger is active on the rising edge TRIG RISE 3

Falling Edge Trigger is active on the falling edge TRIG FALL 4

Table 5: External trigger behaviour for the AWGs (parameter triggerBehaviour function AWGtriggerExternalConfig, Sec-tion 3.3.27 on page 61)

Programming Definitions

Waveform Description Name Value

Analog Analog normalized waveforms (-1..1) defined with doubles WAVE ANALOG 0

IQ Analog normalized waveforms (-1..1) defined with doubles, withtwo components (I and Q)

WAVE IQ 2

IQ Polar Analog normalized waveforms (-1..1) defined with doubles, withtwo components (Amplitude and Phase)

WAVE IQPOLAR 3

Digital Digital waveforms (-1..1) defined with integers WAVE DIGITAL 5

Table 6: Waveform Types for the (parameter waveformType in function new, Section 3.4.1 on page 69)

14 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1.2.3 Signal Selection

The function channelWaveShape (Section 3.3.1 on page 34) controls the signal generation of the SD-PXE-AOU-H0001,allowing the user to select between the different waveshapes of the Function Generator (Section 1.2.1 on page 10) and theAWG (Section 1.2.2 on page 12) of the corresponding channel.

Options

Programming Definitions

Function Description Name Value

No Signal The output signal is set to 0. All other channel settings are main-tained

AOU OFF (default) -1

Sinusoidal Generated by the Function Generator AOU SINUSOIDAL 1

Triangular Generated by the Function Generator AOU TRIANGULAR 2

Square Generated by the Function Generator AOU SQUARE 4

DC Normalized constant value in order to generate DC voltages. Inthis configuration, the output voltage will be set by the channelamplitude setting

AOU DC 5

Arbitrary Waveform Selects the Arbitrary Waveform Generator associated to the chan-nel (for channel x, only Arbitrary Waveform Generator x can beused)

AOU AWG 6

Table 7: Output signal selection (parameter waveShape in function channelWaveShape, Section 3.3.1 on page 34)

Specifications

Parameter Min Typ Max Units Comments

Timing Specifications

Signal Change Latency 100 ns Using HVI Technology (Section 1.5.2 on page 25)

Signal Change Rate 10 ns Using HVI Technology (Section 1.5.2 on page 25)

Table 8: Output signal selection timing specifications

Programming Information

Function Comments Details

channelWaveShape It selects the output signal Section 3.3.1 on page 34

Table 9: Programming functions related to the signal selection

Rev. 1.4 (May 30, 2013) 15 / 73

SD-PXE-AOU-H0001

1.2.4 Amplitude and DC Offset Settings

Each output channel in the SD-PXE-AOU-H0001 has an amplitude and offset control as shown in Figure 14.

Figure 14: Amplitude and offset control within the SD-PXE-AOU-H0001 functional block diagram

Specifications

Parameter Min Typ Max Units Comments

General Specifications

Amplitude Range -1.5 1.5 Volts

Amplitude Resolution 16 Bits ∼ 45.8 μV

Offset Range -1.5 1.5 Volts

Offset Resolution 16 Bits ∼ 45.8 μV

Timing Specifications

Amplitude Change Latency 70 ns Using HVI Technology (Section 1.5.2 on page 25)

Amplitude Change Rate 2 ns Using HVI Technology (Section 1.5.2 on page 25)

Offset Change Latency 70 ns Using HVI Technology (Section 1.5.2 on page 25)

Offset Change Rate 2 ns Using HVI Technology (Section 1.5.2 on page 25)

Table 10: Output amplitude and DC offset specifications

Programming Information

Function Comments Details

channelAmplitude It sets the output amplitude Section 1.2.3 on the previous page and Section 3.3.1 on page 34

channelOffset It sets the output DC offset Section 3.3.6 on page 39

Table 11: Programming functions related to the amplitude and DC offset controls

16 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1.3 Signal Modulation

1.3.1 Angle Modulation (Frequency and Phase)

The output signal of the Function Generator (Section 1.2.1 on page 10) can be modulated in frequency or in phase usingthe angle modulator as shown in Figure 15.

Figure 15: The angle modulator within the SD-PXE-AOU-H0001 functional block diagram

Specifications

Parameter Min Typ Max Units Comments

General Specifications (Frequency)

Deviation -Dev. Gain +Dev. Gain MHz

Deviation Resolution 16 Bits ∼3.05KHz..47.6μHz (dev. gain dependent)

Deviation Gain 0 200 MHz

Deviation Gain Resolution 16 Bits ∼ 3.05 KHz

Modulating Signal BW 0 250 MHz AWG Nyquist limitation (500 MSPS)

Modulating Signal Resolution 16 Bits AWG resolution (deviation resolution)

General Specifications (Phase)

Deviation -Dev. Gain +Dev. Gain Deg

Deviation Resolution 16 Bits ∼5.5 mdeg..83 ndeg (dev. gain dependent)

Deviation Gain 0 180 Deg

Deviation Gain Resolution 16 Bits ∼ 5.5 mdeg

Modulating Signal BW 0 250 MHz AWG Nyquist limitation (500 MSPS)

Modulating Signal Resolution 16 Bits AWG resolution (deviation resolution)

Timing Specifications

- - - - - Given by the AWG (Section 1.2.2 onpage 12)

Table 12: Angle modulator specifications

Rev. 1.4 (May 30, 2013) 17 / 73

SD-PXE-AOU-H0001

Options

Programming Definitions

Function Description Name Value

No Modulation Modulation is disabled AOU MOD OFF (default) 0

Frequency Modulation The AWG is used to modulate the channel frequency AOU MOD FM 1

Phase Modulation The AWG is used to modulate the channel phase AOU MOD PM 2

Table 13: Angle modulation options (parameter modulationType in function ModulationAngleConfig, Section 3.3.7 onpage 40)

The modulating signal is generated using the Arbitrary Waveform Generator (AWG, Section 1.2.2 on page 12) associ-ated to that particular channel, e.g. AWG0 for channel 0. The angle modulator allows the user to create any analog/digitalfrequency or phase modulation, e.g. FM, FSK, PM, PSK, DPSK, etc.

The output signal of a channel using the frequency modulation is the following:

Output(t) = A ∙ cos[2π(fc + G ∙ AWG(t)) ∙ t + φc] (1)

where:

• A is the channel amplitude (set by the function channelAmplitude, Section 3.3.5 on page 38)

• G is the deviation gain or peak frequency deviation (set by modulationAngleConfig, Section 3.3.7 on page 40).

• AWG(t) is the normalized modulating signal generated by the AWG (Section 1.2.2 on page 12)

• cos(2πfc + φc) is the carrier signal, generated with the Function Generator (Section 1.2.1 on page 10)

As an example, for the generation of an FM signal with an amplitude of 0.8 Vp, a modulation index (h) equal to 0.5and a maximum frequency of the modulating signal of 10 MHz, the settings must be A=0.8 and G=5,000,000 (G =h ∙ maxfreq[AWG(t)]).

The output signal of a channel using the phase modulation is the following:

Output(t) = A ∙ cos(2πfc + φc + G ∙ AWG(t)) (2)

where:

• A is the channel amplitude (set by the function channelAmplitude, Section 3.3.5 on page 38)

• G is the deviation gain or peak phase deviation (set by modulationAngleConfig, Section 3.3.7 on page 40).

• AWG(t) is the normalized modulating signal generated by the AWG (Section 1.2.2 on page 12)

• cos(2πfc + φc) is the carrier signal, generated with the Function Generator (Section 1.2.1 on page 10)

As an example, for the generation of a PM signal with an amplitude of 0.8 Vp and a modulation index (h) equal to 1800, thesettings must be A=0.8 and G=180 (G=h).

Programming Information

Function Comments Details

modulationAngleConfig It configures the angle modulator Section 3.3.7 on page 40

AWG functions They control the modulating signal Section 1.2.2 on page 12

FG functions They control the carrier signal Section 1.2.1 on page 10

Table 14: Programming functions related to the angle modulator

18 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1.3.2 Amplitude Modulation

The amplitude modulator can be used to modulate the amplitude of the output signal as show in Figure 16. This modulatorcan be used also to change the DC offset of the output signal.

Figure 16: The amplitude modulator within the SD-PXE-AOU-H0001 functional block diagram

Specifications

Parameter Min Typ Max Units Comments

General Specifications (Amplitude & Offset)

Deviation -Dev. Gain +Dev. Gain Vp

Deviation Resolution 16 Bits ∼ 45.78 μV (limited by the DAC Precision)

Deviation Gain 0 1.5 Vp

Deviation Gain Resolution 16 Bits ∼ 45.78 μV (limited by the DAC Precision)

Modulating Signal BW 0 250 MHz AWG Nyquist limitation (500 MSPS)

Modulating Signal Resolution 16 Bits AWG resolution (deviation resolution)

Timing Specifications

- - - - - Given by the AWG (Section 1.2.2 onpage 12)

Table 15: Amplitude modulator specifications

The modulating signal is generated using the Arbitrary Waveform Generator (AWG, Section 1.2.2 on page 12) as-sociated to that particular channel, e.g. AWG0 for channel 0. The amplitude modulator allows the user to create anyanalog/digital amplitude modulation, e.g. AM, ASK, etc.

The output signal of a channel using the amplitude modulator is the following:

Output(t) = (A + G ∙ AWG(t)) ∙ cos(2πfc + φc) (3)

where:

• A is the channel amplitude (set by the function channelAmplitude, Section 3.3.5 on page 38)

• G is the deviation gain (set by the function modulationAmplitudeConfig, Section 3.3.8 on page 41).

Rev. 1.4 (May 30, 2013) 19 / 73

SD-PXE-AOU-H0001

• AWG(t) is the normalized modulating signal generated by the AWG (Section 1.2.2 on page 12)

• cos(2πfc + φc) is the carrier signal, generated with the Function Generator (Section 1.2.1 on page 10)

As an example, for the generation of an AM signal with an amplitude of 0.8 Vp and a modulation index (h) equal to 0.5, thesettings must be A=0.8 and G=0.32 (G = h ∙ A2).

The output signal of a channel using the amplitude modulator to modulate the offset is the following:

Output(t) = A ∙ cos(2πfc + φc) + G ∙ AWG(t) (4)

Options

Function modulationType (const & value) Description

No Modulation AOU MOD OFF 0 (default) Modulation is disabled. The channel amplitude and off-set are only set by the main registers

Amplitude Modulation AOU MOD AM 1 The modulating signal is used to modulate the channelamplitude

Offset Modulation AOU MOD OFFSET 2 The modulating signal is used to modulate the channeloffset

Table 16: Amplitude modulation options (function modulationAmplitudeConfig, Section 3.3.8 on page 41)

NOTE:

Mutual Exclusions for Modulations: As shown in the functional diagram of Figure 16 on the preceding page, the ampli-tude modulator can be used with signals coming from the Function Generator directly, the AWG or the frequency/phasemodulators. Therefore, the latter can be combined with amplitude modulation at will (although it only makes sense forfrequency/amplitude modulations, because for phase/amplitude modulations there is a dedicated IQ operation, Sec-tion 1.3.3 on the next page), which uses internally the amplitude and the angle modulator.

Programming Information

Function Comments Details

modulationAmplitudeConfig It configures the amplitude modulator Section 3.3.8 on page 41

AWG functions They control the modulating signal Section 1.2.2 on page 12

FG functions They control the carrier signal Section 1.2.1 on page 10

Table 17: Programming functions related to the amplitude modulator

20 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1.3.3 IQ Modulation

The output signal of the Function Generator (Section 1.2.1 on page 10) can be modulated with in-phase (I) and quadrature(Q) components using the IQ modulator as shown in Figure 17.

Figure 17: The IQ modulator within the SD-PXE-AOU-H0001 functional block diagram

Specifications

Parameter Min Typ Max Units Comments

General Specifications

Amplitude Deviation -1.5 +1.5 Vp

Amplitude Deviation Resolution 16 Bits ∼ 45.78 μV

Phase Deviation -180 +180 Deg

Phase Deviation Resolution 16 Bits ∼ 5.5 mdeg

Modulating Signals BW 0 250 MHz AWG Nyquist limitation (500 MSPS)

Modulating Signals Resolution 16 Bits AWG resolution (deviation resolution)

Timing Specifications

- - - - - Given by the AWG (Section 1.2.2 on page 12)

Table 18: IQ modulator specifications

The modulating signal is generated using the Arbitrary Waveform Generator (AWG, Section 1.2.2 on page 12) associ-ated to that particular channel, e.g. AWG0 for channel 0. In this case, the waveform loaded into the AWG is composed bytwo waveforms (I and Q components). Please notice that IQ waveforms are sometimes called complex waveforms due tothe mathematical form I(t)+iQ(t).

The output signal of a channel using the IQ modulator of the SD-PXE-AOU-H0001 is the following:

Output(t) =A√

2∙ [AWGI(t) ∙ cos(2πfc + φc) − AWGQ(t) ∙ sin(2πfc + φc)] (5)

where:

• A is the channel amplitude (set by the function channelAmplitude, Section 3.3.5 on page 38)

• AWGQ(t) and AWGI(t) are the normalized modulating signals generated by the AWG (Section 1.2.2 on page 12)

Rev. 1.4 (May 30, 2013) 21 / 73

SD-PXE-AOU-H0001

• cos / sin(2πfc + φc) is the carrier signal, generated with the Function Generator (Section 1.2.1 on page 10)

It is also possible to use the IQ modulator with amplitude and phase components:

Output(t) = A ∙ AWGA(t) ∙ cos(2πfc + φc +π

2∙ AWGφ(t)) (6)

where:

• A is the channel amplitude (set by the function channelAmplitude, Section 3.3.5 on page 38)

• AWGA(t) and AWGφ(t) are the normalized modulating signals generated by the AWG (Section 1.2.2 on page 12)

• cos(2πfc + φc) is the carrier signal, generated with the Function Generator (Section 1.2.1 on page 10)

NOTE:

Mathematical Background of IQ Modulation

The IQ modulation is based on the decomposition of the output signal in sinus and cosinus

A ∙ cos(2πfc + φc + φ) = A ∙ cos(2πfc + φc) cos(φ) − A ∙ sin(2πfc + φc) sin(φ) (7)

where the I and Q components are defined as follows

I = A ∙ cos(φ)

Q = A ∙ sin(φ)(8)

and therefore, the IQ components become very useful to set the amplitude (A) and the phase (φ) of the output signal,giving as a result the IQ modulation (or QAM, Quadrature Amplitude Modulation):

A ∙ cos(2πfc + φc + φ) = I ∙ cos(2πfc + φc) − Q ∙ sin(2πfc + φc) (9)

NOTE:

Mutual Exclusions for Modulations: Internally, the IQ modulation uses the amplitude and the angle modulators, andtherefore they cannot be used when the module is working in IQ mode

Programming Information

Function Comments Details

modulationIQconfig It configures the IQ modulator Section 3.3.9 on page 42

AWG functions They control the modulating signal Section 1.2.2 on page 12

FG functions They control the carrier signal Section 1.2.1 on page 10

Table 19: Programming functions related to the IQ modulator

22 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1.4 Clock and Trigger

1.4.1 Clock System

The SD-PXE-AOU-H0001 clock system (Figure 18) uses the internal clock provided by the chassis as a reference clock.This reference clock is jitter cleaned by the module, resulting in a very high quality clock. This implementation achieves ajitter and phase noise above a 100 Hz independently of the source clock, depending on the chassis only for the frequencyabsolute precision and long term stability. A copy of the system clock is available at the CLK connector, which operationcan be configured by the user (Table 20).

ADVANCED:

The reference clock is taken from the signals PXIe CLK100, in the case of PXI Express, and RefClk, in the case ofCompactPCI Express. In some PXI Express chassis, the user can replace the PXIe CLK100 with an external reference(with a reference input connector or with a PXI Express timing module, see chassis specifications).

Figure 18: SD-PXE-AOU-H0001 simplified clock system diagram

CLK Connector Function clockConfig Description

Disable n/a 0 (default) The CLK connector is not used

Output 10 MHz 10 A 10 MHz copy of the system clock is available at the CLKconnector

50 MHz 50 A 50 MHz copy of the system clock is available at the CLKconnector

Table 20: SD-PXE-AOU-H0001 output clock configuration (function clockIOconfig, Section 3.3.10 on page 43)

1.4.2 Trigger I/O

The SD-PXE-AOU-H0001 has a general purpose input/output trigger (TRG connector). This signal can be used as generalpurpose digital IO or as a trigger input as shown in Table 21.

Function Direction triggerConfig (const & value) Description

Digital Output O AOU TRG OUT 0 TRG operates as a general purpose digital out-put signal, which can be written by the user soft-ware

Digital Input / Trigger I AOU TRG IN 1 (default) TRG operates as a trigger (Table 3 on page 14),or as general purpose digital input signal, whichcan be read by the user software

Table 21: SD-PXE-AOU-H0001 TRG connector configuration (function triggerIOdirection, Section 3.3.11 on page 44)

Rev. 1.4 (May 30, 2013) 23 / 73

SD-PXE-AOU-H0001

1.5 Operation Modes

NOTE:

The following information describes how Signadyne hardware modules can be operated. These modes of operation arenot mutually exclusive , and therefore can be combined to develop any control, test and measurement application.

1.5.1 Ready-to-use Operation

All Signadyne modules can be used as a classical workbench instrument using Signadyne VirtualKnob [1], our ready-to-use software front panels for live operation. VirtualKnob converts Signadyne modules into turnkey instruments for standardtest and measurement applications.

Figure 19: ProcessFlow provides software front panels to operate the modules as classical workbench instruments.

24 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

1.5.2 User-defined Operation

Signadyne modules are fully programmable and controllable from the PC, allowing the user to completely customize theiroperation. The modularity, scalability, latency and speed of the PXI Express standard outperforms any other programablecontrol, test and measurement solution.

a) Virtual Instrument (VI)

Virtual instrumentation is the use of customizable software to create user-defined control, test and measurement sys-tems, called Virtual Instruments (VI). In a normal VI, instructions are executed by the user PC, and only the input/outputcommands are sent to the modules (Figure 20). Therefore, the speed, latency, and real-time performance is limited by thePC.

Figure 20: Virtual Instrument (VI) operation. The user-defined software (VI) is executed in the system computer and thecommands are transferred to the modules.

Signadyne delivers highly optimized programming libraries to program VIs in nearly any programming language, e.g.C/C++, LabVIEW, MATLAB, etc.

ADVANCED:

Using advanced programming techniques -e.g. multithreading, callback functions, onboard waveform buffering, DMA,etc.- increases the performance of the system execution. Our libraries do make use of these advanced techniques.

NOTE:

Some manufacturers refer to some of these advanced techniques as ”hardware triggering”, but this concept must notbe confused with Signadyne’s Hard Virtual Instrument (HVI).

Rev. 1.4 (May 30, 2013) 25 / 73

SD-PXE-AOU-H0001

b) Hard Virtual Instrument (HVI)

With Signadyne’s exclusive hard virtual instrumentation technology the user can write custom software directly into anySignadyne hardware module, extending the concept and capabilities of virtual instrumentation. In a Hard Virtual Instrument(HVI), the user program is executed by the hardware modules independently of the computer, which stays free for otherVI tasks, like visualization, user interaction, etc. The I/O modules run in parallel, completely synchronized, and exchangedata and decisions in real-time (Figure 21). The result is a set of modules that behave like a single integrated real-timeinstrument.

Figure 21: Hard Virtual Instrument (HVI) operation. The user HVI program is executed inside the Signadyne PXIe modules,and the computer is only occupied with other VI processes (e.g. data post-processing, visualization, etc.). All cards in anHVI work perfectly synchronized.

NOTE:

Signadyne ProcessFlow (HVI Programming Environment): HVIs are programmed with Signadyne ProcessFlow [3],an HVI programming environment with a user-friendly flowchart-style interface, compatible with all Signadyne hardwaremodules.

Signadyne’s hard virtual instrumentation technology provides:

• User-friendly flowchart-style programming interface: Signadyne ProcessFlow provides an intuitive flowchart-style programming environment that makes HVI programming extremely fast and easy (Figure 22 on the next page).Using ProcessFlow and its set of built-in instructions (the same instructions available for VIs), the user can programthe hardware modules without any knowledge of FPGA technology, VHDL, etc.

• Ultra-fast hard real time execution, processing and decision making: Execution is hardware timed and can beas fast as 1 nanosecond, outperforming any real-time operating system.

• Complete robustness: Execution is performed by hardware, without operating system, and independently of theuser PC.

• Off-the-shelf intermodule synchronization and data exchange: Each HVI is defined by a group of PXIe moduleswhich work perfectly synchronized, without the need of any external trigger, additional external hardware or any PXISystem Timing Module. In addition, Signadyne modules exchange data and decisions for ultra-fast control algorithms.

• Signadyne/user-defined FPGA-based processing: Signadyne delivers ready-to-use FPGA-based functions likeFFTs, FIRs, PIDs, etc., which can be easily included in an HVI. In addition to these predefined functions, the user canalso include custom FPGA-based functions implemented with MATLAB/Simulink or VHDL (Figure 23 on the facingpage).

26 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

Figure 22: Signadyne ProcessFlow provides an intuitive flowchart environment to program hard real-time systems withof-the-shelf inter-module synchronization.

Figure 23: Signadyne ProcessFlow provides tools to easily program any Signadyne hardware module with build-in instruc-tions and FPGA-based functions.

Rev. 1.4 (May 30, 2013) 27 / 73

SD-PXE-AOU-H0001

c) VIs and HVIs Interaction

HVIs outperform VIs in terms of speed, real-time processing, intermodule synchronization, robustness, etc., but thereare still some non-time-critical tasks that can only be performed by a VI, like for example: user interaction, visualization,or processing and decisions tasks which are too complex to be implemented by hardware. Therefore, a complex control,test and measurement system may require the combination of VIs and HVIs, and with Signadyne programming tools thiscombination can be performed seamlessly.

A Signadyne HVI can be fully control by a VI with instructions like start, stop, pause, etc. Signadyne ProgrammingLibraries provide also highly optimized DMA-based data transfer between VIs and HVIs, and an efficient event system tosynchronize them (Figure 24).

Figure 24: With Signadyne Programming Libraries, VIs and HVIs can be combined seamlessly for complex control, testand measurement systems.

28 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

2 VirtualKnob Front Panel

As mentioned in Section 1.5.1 on page 24, all Signadyne modules can be used as a classical workbench instrument usingSignadyne VirtualKnob [1], our ready-to-use software front panels for live operation. This Chapter describes the basicoperations of the SD-PXE-AOU-H0001 VirtualKnob front panel.

2.0.3 Front Panel Overview

Figure 25 shows the SD-PXE-AOU-H0001 VirtualKnob front panel, which appears automatically when VirtualKnob islaunched and the module is connected to the chassis. If there are no modules available, VirtualKnob will launch ”DemoOffline” modules.

Figure 25: SD-PXE-AOU-H0001 front panel overview.

When VirtualKnob is launched, the SD-PXE-AOU-H0001 front panel appears empty, waiting for the user to add ”Chan-nels”, which are windows that control the channel operation. For maximum visualization flexibility, output channels can be

Rev. 1.4 (May 30, 2013) 29 / 73

SD-PXE-AOU-H0001

added as new Panels or as Tabs within an existing Panel.

2.1 Signal Generation

Figure 26 shows the signal generation controls of the SD-PXE-AOU-H0001 in VirtualKnob.

Figure 26: SD-PXE-AOU-H0001 signal generation control.

2.1.1 Arbitrary Waveform Generation

Figure 27 on the next page shows the dialogs and the workflow to generate arbitrary waveforms in VirtualKnob using theAWGs (Section 1.2.2 on page 12).

AWG Workflow:

1) Configuration of the external AWG triggers (optional): If external triggers are required, this dialog must be usedto configure the source (external trigger connector, PXI trigger lines, etc.,) and the behaviour (logic level high/low,rising/falling edge, etc.).

2) Waveforms loading: Waveforms must be transferred to the onboard RAM in order to put them in the AWG queue.This dialog allows the user to select the waveform files and to assign custom waveform names. The waveforms aretrasnferred to the onboard RAM when the dialog is closed.

3) AWG queue configuration: The waveforms loaded into the onboard RAM can be pushed into the correspondingAWG queue. This dialog allows the user to select the AWG queue options described in Section 1.2.2 on page 12.

Once the waveforms are queued in the corresponding AWG, they can be launched using the AWG control button shownin Figure 26.

30 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

Figure 27: SD-PXE-AOU-H0001 AWG workflow.

2.2 Signal Modulation

Figure 28 shows the tab to configure the modulations in the Channel Panel.

Figure 28: SD-PXE-AOU-H0001 signal modulation control.

As descrived in Section 1.3 on page 17, the modulating signal for the modulators of one channel comes from the AWGcorresponding to that particular channel. Therefore, the user must configure the AWG (See AWG workflow in VirtualKnob(Section 2.1.1 on the preceding page) and the modulators as shown in Figure 28. After this process, the user must run theAWG in the channel panel (Figure 25 on page 29).

As the IQ modulator uses both the amplitude modulator and the phase modulator, it can be selected from any of the”modulation type” combo boxes.

Rev. 1.4 (May 30, 2013) 31 / 73

SD-PXE-AOU-H0001

3 VI / HVI Programming

3.1 VI Programming Overview

As described in Section 1.5.2 on page 25, virtual instrumentation is the use of customizable software to create user-defined control, test and measurement systems, called Virtual Instruments (VI). For this purpose, Signadyne delivershighly optimized static and dynamic programming libraries [2]:

a) Static Libraries

Ready-to-use static libraries are supplied for the following programming languages and compilers:

Language Compiler Files

C Any C compiler *.h, *.lib

MinGW (Qt), GCC *.h, *.a

C++ Microsoft Visual Studio *.h, *.lib

MinGW (Qt), GCC *.h, *.a

LabVIEW National Instruments LabVIEW *.vi

b) Dynamic Libraries

Dynamic libraries are compatible with any programming language that has a compiler capable of performing dynamiclinking. Here are some examples:

∙ C++ compilers not listed above.

∙ Other programming languages: Java, Python, Visual Basic, C#, PHP, Perl, Fortran, Pascal, etc.

∙ Computer Algebra Systems (CAS): MathWorks MATLAB, Wolfram Mathematica, Maplesoft Maple, etc.

Dynamic libraries available:

Exported Functions Language Operating System Files

C Microsoft Windows *.dll

NOTE:

DLL function prototypes: The exported functions of the dynamic libraries have the same prototype as their counter-parts of the static libraries.

NOTE:

Function Parameters: Some of the parameters of the library functions are language dependent. The table of inputs andoutputs parameters for each function is a conceptual description, therefore, the user must check the specific languagefunction to see how to use it. One example are the ID parameters (moduleID, etc.), which identify objects in non object-oriented languages. In object-oriented languages the objects are identified by their instances, and therefore the IDs arenot present.

Function Names: Some programming languages like C++ or LabVIEW have a feature called function overloading orpolymorphism, that allows creating several functions with the same name but with different input/output parameters. Inlanguages without this feature, functions with different parameters must have different names.

32 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.2 HVI Programming Overview

As described in Section 1.5.2 on page 25, with Signadyne’s exclusive hard virtual instrumentation technology the usercan write custom software directly into any Signadyne hardware module, extending the concept and capabilities of virtualinstrumentation. Most of the VI instructions described in this Chapter are available for HVI real-time hardware execution(programmed using Signadyne ProcessFlow [3], the HVI programming environment).

The user can find the ProcessFlow programming details and the real-time specifications of each instruction within thecorresponding function description.

Rev. 1.4 (May 30, 2013) 33 / 73

SD-PXE-AOU-H0001

3.3 SD-AOU Class Functions

3.3.1 channelWaveShape

This function sets the channel output waveform type (Section 1.2.3 on page 15).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

HVI Technology (ProcessFlow)

Execution Latency: 100 ns

Max Execution Rate: 10 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

waveShape int int selection list Waveshape type (Table 7 on page 15)

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU channelWaveShape(int moduleID, int nChannel, int waveShape);

C++ Function

int SD AOU::channelWaveShape(int nChannel, int waveShape);

ProcessFlow

channelWaveShapeChannelWave shape

LabVIEW

SD Module channelWaveShape.vi

34 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.2 channelFrequency

This function sets the frequency for the periodic signals generated by the Function Generators (Section 1.2.1 on page 10).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

HVI Technology (ProcessFlow)

Execution Latency: 120 ns

Max Execution Rate: 10 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

frequency double double - Frequency in Hz

- - - constant[unit] Frequency in [unit]

- - - variable The selected variable sets the frequency. Its valuemust be 0..(232−1), which corresponds to 0..MaxFre-quency (see Specifications on page 3)

errorIn - - - If it contains an error, the function will not be executedand errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU channelFrequency(int moduleID, int nChannel, double frequency);

C++ Function

int SD AOU::channelFrequency(int nChannel, double frequency);

ProcessFlow

channelFrequencyChannelFrequency

TypeValue

LabVIEW

SD Module channelFrequency.vi

Rev. 1.4 (May 30, 2013) 35 / 73

SD-PXE-AOU-H0001

3.3.3 channelPhase

This function sets the phase for the periodic signals generated by the Function Generators (Section 1.2.1 on page 10).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

HVI Technology (ProcessFlow)

Execution Latency: 120 ns

Max Execution Rate: 10 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

phase double double - Phase in degrees

- - - constant[unit] Phase in [unit]

- - - variable The selected variable sets the phase. Its value mustbe 0..(232 − 1), which corresponds to 0..360◦

errorIn - - - If it contains an error, the function will not be executedand errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU channelPhase(int moduleID, int nChannel, double phase);

C++ Function

int SD AOU::channelPhase(int nChannel, double phase);

ProcessFlow

channelPhaseChannelPhase

TypeValue

LabVIEW

SD Module channelPhase.vi

36 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.4 channelPhaseReset

This function resets the accumulated phase of the selected channels. This accumulated phase is a result of the phasecontinuous module operation (Section 1.2.1 on page 10).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

HVI Technology (ProcessFlow)

Execution Latency: 100 ns

Max Execution Rate: 10 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

channelMask int int - Mask to select the channels to reset (LSB is channel 0, bit 1is channel 1 and so forth)

channel - - - selection list Channel to reset

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU channelPhaseReset(int moduleID, int channelMask);

C++ Function

int SD AOU::channelPhaseReset(int channelMask);

ProcessFlow

channelPhaseResetChannel

LabVIEW

SD Module channelPhaseReset.vi

Rev. 1.4 (May 30, 2013) 37 / 73

SD-PXE-AOU-H0001

3.3.5 channelAmplitude

This function sets the amplitude of a channel (Section 1.2.4 on page 16).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

HVI Technology (ProcessFlow)

Execution Latency: 70 ns

Max Execution Rate: 2 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

amplitude double double - Amplitude in volts

- - - constant[unit] Amplitude in [unit]

- - - variable The selected variable sets the amplitude. Its valuemust be −(215 − 1)..(215 − 1), which corresponds to−MaxAmplitude..MaxAmplitude (see Specificationson page 3)

errorIn - - - If it contains an error, the function will not be executedand errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU channelAmplitude(int moduleID, int nChannel, double amplitude);

C++ Function

int SD AOU::channelAmplitude(int nChannel, double amplitude);

ProcessFlow

channelAmplitudeChannelAmplitude

TypeValue

LabVIEW

SD Module channelAmplitude.vi

38 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.6 channelOffset

This function sets the DC offset of a channel (Section 1.2.4 on page 16).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

HVI Technology (ProcessFlow)

Execution Latency: 70 ns

Max Execution Rate: 2 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

offset double double - DC offset in volts

- - - constant[unit] DC offset in [unit]

- - - variable The selected variable sets the DC offset.Its valuemust be −(215 − 1)..(215 − 1), which corresponds to−MaxAmplitude..MaxAmplitude (see Specificationson page 3)

errorIn - - - If it contains an error, the function will not be executedand errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU channelOffset(int moduleID, int nChannel, double offset);

C++ Function

int SD AOU::channelOffset(int nChannel, double offset);

ProcessFlow

channelOffsetChannelOffset

TypeValue

LabVIEW

SD Module channelOffset.vi

Rev. 1.4 (May 30, 2013) 39 / 73

SD-PXE-AOU-H0001

3.3.7 modulationAngleConfig

This function configures the modulation in frequency/phase for the selected channel (Section 1.3.1 on page 17).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

modulationType int int selection list Modulation type (Table 13 on page 18)

deviationGain double double constant Gain for the modulating signal

errorIn - - - If it contains an error, the function will not be exe-cuted and errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU modulationAngleConfig(int moduleID, int nChannel, int modulationType, int deviationGain);

C++ Function

int SD AOU::modulationAngleConfig(int nChannel, int modulationType, int deviationGain);

ProcessFlow

modulationAngleConfigChannelModulation typeDeviation gain

LabVIEW

SD Module modulationAngleConfig.vi

40 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.8 modulationAmplitudeConfig

This function configures the modulation in amplitude/offset for the selected channel (Section 1.3.2 on page 19).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

modulationType int int selection list Modulation type (Table 16 on page 20)

deviationGain double double constant Gain for the modulating signal

errorIn - - - If it contains an error, the function will not be exe-cuted and errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU modulationAmplitudeConfig(int moduleID, int nChannel, int modulationType, int deviationGain);

C++ Function

int SD AOU::modulationAmplitudeConfig(int nChannel, int modulationType, int deviationGain);

ProcessFlow

modulationAmplitudeConfigChannelModulation typeDeviation gain

LabVIEW

SD Module modulationAmplitudeConfig.vi

Rev. 1.4 (May 30, 2013) 41 / 73

SD-PXE-AOU-H0001

3.3.9 modulationIQconfig

This function sets the IQ modulation for the selected channel (Section 1.3.3 on page 21).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nChannel int int selection list Output channel number

enable int int selection list Enable (value 1) or Disable (value 0) the IQ modulation.

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU modulationIQconfig(int moduleID, int nChannel, in enable);

C++ Function

int SD AOU::modulationIQconfig(int nChannel, int enable);

ProcessFlow

modulationIQconfigChannelEnable

LabVIEW

SD Module modulationIQconfig.vi

42 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.10 clockIOconfig

This function configures the function of the clock output connector (CLK, Figure 18 on page 23).

Compatibility

Programming Libraries v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

clockConfig int int - Clock connector function (Table 20 on page 23)

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU clockIOconfig(int moduleID, int clockConfig);

C++ Function

int SD AOU::clockIOconfig(int clockConfig);

LabVIEW

SD Module clockIOconfig.vi

Rev. 1.4 (May 30, 2013) 43 / 73

SD-PXE-AOU-H0001

3.3.11 triggerIOdirection

This function configures the trigger connector direction (TRG, Section 1.4.2 on page 23).

Compatibility

Programming Libraries v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

direction int int - Input or output (Table 21 on page 23)

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU triggerIOdirection(int moduleID, int direction);

C++ Function

int SD AOU::triggerIOdirection(int direction);

LabVIEW

SD Module triggerIOdirection.vi

44 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.12 triggerIOwrite

This function sets the trigger output (the trigger must be configured as output using triggerIOdirection, Section 3.3.11 onthe preceding page).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Signadyne ProcessFlow

Execution Latency: 20 ns

Timing resolution: 2 ns

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

value int int selection list Trigger output value: 0 (OFF), 1 (ON)

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU triggerIOwrite(int moduleID, int value);

C++ Function

int SD AOU::triggerIOwrite(int value);

ProcessFlow

triggerIOwriteValue

LabVIEW

SD Module triggerIOwrite.vi

Rev. 1.4 (May 30, 2013) 45 / 73

SD-PXE-AOU-H0001

3.3.13 triggerIOread

This function reads the trigger input (Section 1.4.2 on page 23)

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

destination - - - selection list Destination variable to store the trigger value: 0 (OFF), 1(ON)

trigger int int - 0 (OFF), 1 (ON), or negative numbers for errors (see errorcodes in Table 22 on page 71)

errorOut - - - See error codes in Table 22 on page 71

C Function

int SD AOU triggerIOread(int moduleID);

C++ Function

int SD AOU::triggerIOread();

ProcessFlow

triggerIOreadDestination

LabVIEW

SD Module triggerIOread.vi

46 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.14 waveformLoad

This function loads the specified waveform into the module onboard RAM. Waveforms must be created first with the SD-Wave class (Section 3.4 on page 69).

ADVANCED:

Memory usage: When a waveform is replaced (same waveformNumber used more than once) and the new waveformhas a different size than the old one, the module’s RAM memory has to be defragmented. In this case the process takesmore time to be accomplished.

Compatibility

Programming Libraries v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

waveformID int - - Waveform identifier (see SD-Wave Class, Sec-tion 3.4 on page 69)

waveformObject - SD Wave* - - Pointer to the waveform object (see SD-WaveClass, Section 3.4 on page 69)

waveformNumber int int - Waveform number to identify the waveform in sub-sequent related fution calls. This value must be inthe [0..n] range, and in order to optimized onboardmemory usage, it should as low as possible

errorIn - - - If it contains an error, the function will not be exe-cuted and errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

availableRAM int int - Available onboard RAM in waveform points, or anegative number for errors (see error codes in Ta-ble 22 on page 71)

errorOut - - - See error codes in Table 22 on page 71

C Function

int SD AOU waveformLoad(int moduleID, int waveformID, int waveformNumber);

C++ Function

int SD AOU::waveformLoad(SD Wave* waveformObject, int waveformNumber)

LabVIEW

SD Module waveformLoad.vi

Rev. 1.4 (May 30, 2013) 47 / 73

SD-PXE-AOU-H0001

3.3.15 waveformFlush

This function deletes all the waveforms from the module onboard RAM and flushes all AWG queues (AWGflush, Sec-tion 3.3.18 on page 52).

Compatibility

Programming Libraries v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU waveformFlush(int moduleID);

C++ Function

int SD AOU::waveformFlush()

LabVIEW

SD Module waveformFlush.vi

48 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.16 AWG

This function provides a one-step method to load, queue and run a single waveform in one of the module Arbitrary Wave-form Generators (AWGs) (Section 1.2.2 on page 12). The waveform can be loaded from an array of points in memory orfrom a file.

ADVANCED:

Step by step programming: This function is equivalent to create a waveform with new (SD-Wave class, Section 3.4on page 69), and to call WaveformLoad, AWGqueueWaveform and AWGstart. With these functions, the user hascomplete control of the memory usage, data transfer times between the PC and the module, and the possibility tocreate generation sequences and to control the generation start time precisely (Section 1.2.2 on page 12).

Compatibility

Programming Libraries v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nAWG int int - AWG number where the waveform is queued

triggerMode int int - Trigger method to launch the waveform (Ta-ble 3 on page 14)

startDelay int int - Defines the delay between the trigger and thewaveform launch in tens of ns

cycles int int - Number of times the waveform is repeatedonce launched (negative means infinite)

prescaler int int - Prescaler value (0..4095). It reduces thewaveform output sampling rate as follows:Tsout = prescaler ∙ 10 ns. 0 means prescalerdisabled.

waveformType int int - Waveform Type (Table 6 on page 14)

waveformPoints int int - Number of points of the waveform, which mustbe a multiple of 10 points and a minimum of20

waveformDataA double* double* - Array with waveform points. Analog wave-forms are defined with floating point numbers,which correspond to a normalized amplitude(-1 to 1)

waveformDataB double* double* - Array with waveform points, only for the wave-forms which have a second component (e.g.Q in IQ modulations defined in cartesian, orphase in IQ modulations defined with polars)

waveformFile char* char* - File containing the waveform points

errorIn - - - If it contains an error, the function will not beexecuted and errorIn will be passed to erro-rOut

Outputs

moduleIDOut - - - A copy of moduleID

availableRAM int int - Available onboard RAM in waveform points, ornegative number for errors (see error codes inTable 22 on page 71)

errorOut - - - See error codes in Table 22 on page 71

Rev. 1.4 (May 30, 2013) 49 / 73

SD-PXE-AOU-H0001

C Function

int SD AOU AWGfromArray(int moduleID, int nAWG, int triggerMode, int startDelay, int cycles, int prescaler,int waveformType, int waveformPoints, double* waveformDataA, double* waveformDataB=0);

int SD AOU AWGfromFile(int moduleID, int nAWG, char* waveformFile, int triggerMode, int startDelay, int cycles,int prescaler);

C++ Function

int SD AOU::AWG(int nAWG, int triggerMode, int startDelay, int cycles, int prescaler, int waveformType,int waveformPoints, double* waveformDataA, double* waveformDataB=0);

int SD AOU::AWG(int nAWG, char* waveformFile, int triggerMode, int startDelay, int cycles, int prescaler);

LabVIEW

SD Module AWGfromArray.vi SD Module AWGfromFile.vi

50 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.17 AWGqueueWaveform

This function queues the specified waveform in one of the Arbitrary Waveform Generators (AWGs) of the module (Sec-tion 1.2.2 on page 12). The waveform must be already loaded in the module onboard RAM (function waveformLoad,Section 3.3.14 on page 47).

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nAWG int int - AWG number where the waveform is queued

waveformNumber int int constant Waveform to be queued into the AWG. It must be al-ready loaded with WaveformLoad

triggerMode int int - Trigger method to launch the waveform (Table 3 onpage 14)

startDelay int int - Defines the delay between the trigger and the waveformlaunch in tens of ns

cycles int int - Number of times the waveform is repeated oncelaunched (negative means infinite)

prescaler int int - Prescaler value (0..4095). It reduces the waveform out-put sampling rate as follows: Tsout = prescaler ∙ 10 ns.0 means prescaler disabled.

errorIn - - - If it contains an error, the function will not be executedand errorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU AWGqueueWaveform(int moduleID, int nAWG, int waveformNumber, int triggerMode, int startDelay,int cycles, int prescaler);

C++ Function

int SD AOU::AWGqueueWaveform(int nAWG, int waveformNumber, int triggerMode, int startDelay, int cycles, int prescaler);

ProcessFlow

AWGqueueWaveformAWGWaveform numberTrigger modeStart delay

TypeValue

Cycles

LabVIEW

SD Module AWGqueueWaveform.vi

Rev. 1.4 (May 30, 2013) 51 / 73

SD-PXE-AOU-H0001

3.3.18 AWGflush

This function empties the queue of the selected Arbitrary Waveform Generator (AWG) (Section 1.2.2 on page 12). Wave-forms are not removed from the module onboard RAM.

Compatibility

Programming Libraries v0.9 or newerSignadyne ProcessFlow v0.9 or newer

Parameters

NameType

DescriptionC C++ LabVIEW ProcessFlow

Inputs

moduleID int - - Module identifier (returned by Open)

nAWG int int selection list AWG number

errorIn - - - If it contains an error, the function will not be executed anderrorIn will be passed to errorOut

Outputs

moduleIDOut - - - A copy of moduleID

errorOut int int - See error codes in Table 22 on page 71

C Function

int SD AOU AWGflush(int moduleID, int nAWG);

C++ Function

int SD AOU::AWGflush(int nAWG);

ProcessFlow

AWGflushAWG

LabVIEW

SD Module AWGflush.vi

52 / 73 Rev. 1.4 (May 30, 2013)

SD-PXE-AOU-H0001

3.3.19 AWGstart