Design of a 22V 32V-to-15V DC/DC Power Converter under...

Click here to load reader

Transcript of Design of a 22V 32V-to-15V DC/DC Power Converter under...

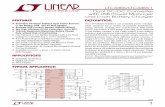

Design of a 22V∼32V-to-15V DC/DC PowerConverter under Input and Load Variations

Zheng ZhangDepartment of Electrical Engineering and Computer Science, MIT

Email: z [email protected] on May 16, 2012

Abstract—This report presents the design procedure of a buckconverter, which converts a 22V∼32V DC input voltage to a15V DC output, under a resistive load variation from 1.5Ω to4.5Ω. Detailed analysis and simulation results, as well as electricaland thermal device specifications are provided. A voltage-modePI controller is designed to stabilize the averaged system underinput and load variations. The worst-case efficiency of this buckconverter is above94.59%.

I. DESIGN REQUIREMENTS

The design requirements of the electrical parameters for thebuck converter are listed in Table I.

TABLE IDESIGN REQUIREMENTS.

Input voltage range 22 ∼ 32 VInput voltage transient limit 44 V for up to 1 msOutput power range 50 ∼ 150 VOutput voltage (static) 15 V±3%Output voltage (transient) 15 V±20%Output voltage ripple (p-p value) ≤ 100 mVInput current ripple (p-p value, ideal source)≤ 100 mAEfficiency ≥ 88%

Besides, it is required that the junction temperature ofthe power devices should remain sufficiently (at least 25C)below the allowable maximum junction temperature, while theambient temperature is in the range of−20C∼ +50C. It isalso required that the temperature rise of inductor should bebelow 50C.

II. TOP-LEVEL DESIGN V IEW

As shown in Fig. 1, assume that the duty ratio of the switchis d and the input DC voltage isV1, then the output DC voltagecan be decided as

Vo = dV1. (1)

And the power at the output stage is

Po = V 2o /Ro. (2)

SinceVo = 15 V, andPo = 50 ∼ 150 W, the load resistanceRo can vary in the range of1.5 ∼ 4.5Ω. And accordingly, theaveraged current through the inductor shall vary in the rangeof 10

3 ∼ 10 A.In our design, we seeV1 = 27 V andd = 5

9 as the nominaldesign. The switching frequency is set asfsw = 200 KHzbased on the following tradeoffs:

V 1

Ro

Lo

Co

+

-

V o S

D

+V D

-

I D

I s I Lo

q(t)

Fig. 1. Top-level schematic of a buck converter.

1) The switching frequency shall be high enough, since asfsw gets higher the ripples iniLo andvo become smaller;

2) The switching frequency cannot be arbitrarily high. Asfsw increases, the switching losses in the power deviceswill increases. Meanwhile, the core power loss and lossdue to the skin effects also become more significant asfsw increases.

The following main problems need to be addressed in ourdesign:

1) The output stage should be designed such that the outputvoltage has small ripples.

2) An input EMI filter should be added between the switchand the input source, to ensure that the current flowingthrough the input source has small ripples.

3) The circuit should be designed such that this DC buckconverter can work well under load variations from1.5Ωto 4.5Ω (or vise versa).

4) The power and passive devices and thermal devicesshould be carefully selected such that designed circuitworks well under parasitic and thermal effects.

5) As the input voltage change in the range of22 ∼ 32 V,the duty ratiod should be tuned according to the inputlevel to ensureVo stay at15 V. This requires us to designa feedback controller to form a stable close-loop systemsuch that the output stays at the nominal value.

III. C IRCUIT SCHEMATIC DESIGN

A. Output Stage

The output stage is designed under two constraints:

1) The inductorLo should be large enough to make thecurrent rippels ofiLo small enough;

t

T dT 2T t 1 t 2

-0.5I L o,p-p

0.5I Lo,p-p i Lo,ac

Fig. 2. AC component of the current through inductorLo.

V 1

Ro

Lo

Co

+

-

V o S

D

+V D

-

I D

I s I Lo

q(t)

R d

C d C f

L f

EMI filter

Fig. 3. The buck converter with an EMI input filter.

2) The capacitorCo should be large enough to make thevoltage ripple ofvo small enough.

Denote the voltage across the inductorLo as vLo. Whenthe switch turns onVD = V1 andvLo = V1 − Vo = V1 − 15;otherwise, the diode turns on andvLo = −15 V. Therefore,the peak-to-peak current ofLo can be computed as

ILo,p−p =1

Lo

(V1 − 15) dT =1

Lo

(V1 − 15)15

V1T, (3)

which approaches the maximum (worst-case) value whenV1 =32V. To ensure the peak-to-peak value of the inductor currentbelow a specified boundδ1, the inductor value should be

Lo ≥(

15− 22532

)

T

δ1=

39.8438

δ1µH. (4)

Here we chooseδ1 = 1.4A, then we have

Lo ≥ 28.46 µH. (5)

The ac component ofiLo is shown in Fig. 2. Assume thatcapacitorCo is large enough, and this ac current all flowsthroughCo, the output voltage ripple (peak-to-peak value) canbe computed as

Vo,p−p =1

Co

∫ t2

t1

iL,acdt =IL,p−pT

8Co

, (6)

Given an upper boundδ2 for Vo,p−p, the capacitance shouldbe selected according to

Co ≥ IL,p−pT

8δ2. (7)

Since it is required thatVo,p−p ≤ 1 mV, we can selectδ2 = 0.1V and lead to

Co ≥ 3.5 µF. (8)

i s,ac R d

C d C f

L f

i x

t T dT

i s,ac

(1-d)I Lo

-dI Lo

Fig. 4. Left: the ac signal model to analyze input current ripple. Right:waveform of the ac component of the switch current.

Our simulation results show that when we increasesCo

and decreasesLo, the maximum transient magnitude ofVo

would decrease. Based on this observation, we remarkablyincreaseCo and slightly increaseLo which leads to smallerinductor current ripples, much smaller output voltage ripplesand much smaller transient peak ofvo. Based on the data sheetinformation, we select

Co = 100 µF, Lo = 31.5 µH. (9)

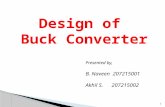

B. Input-Stage EMI Filter

To reduce the current ripples of the input stage, we canadd a damped LC filter, as shown in Fig. 3. Since the switchcurrent is(t) ≈ ILo when the switch turns on andis(t) = 0when the switch turns off, we can model the output stage bya current source and get an equivalent circuit for analyzingthe input current of this converter, as shown in the left partofFig. 4. The input current of this circuit model is in fact theac component of the switch current, the waveform of whichis plotted in the right part of Fig. 4.

To reduce the ripple of the input current, we need to reduceits ac componentix. For simplicity, we perform the ac analysisusingV1=30 andd = 0.5, since in this case the ac componentof is,ac is odd in time and its n-th Fourier coefficient can beeasily obtained as

Ins,ac =2ILnπ

. (10)

We only consider the fundamental harmonic, since the higher-order harmonics in the input current are negligible due to thelow-pass property of the damped EMI filter. In Laplace domain

ix(s) = g(s)is,ac(s), (11)

whereg(s) is the transfer function from switch current to inputcurrent. We can select a large damping capacitorCd such that2πfswCd 1/Rd, and thus

g(s) ≈ ix(s)

is,ac(s)=

1

s2LfCf + sLf

Rd+ 1

(12)

in the frequency band of interest. We notice that whens = 0,20lg|g(s)| = 0, and|g(s)| decreases by40 dB/Dec whenω >

1√CfLf

.

There is a “negative resistance” under constant power trans-fer (seen from the switch), which is calculated as

rl =−Po

I2in=

−V 21

Po

, . (13)

10−2

100

102

104

106

108

1010

−150

−100

−50

0

ω (rad/sec)

20lg

(|g(

jω)|

)

Fig. 5. Magnitude of the transfer functiong(s) (current gain of the EMIfilter).

Fig. 6. Circuit schematic used for simulation of the steady-state and transientbehavior ofVo.

The minimum value of|rl| is 3.2267Ω whenV1 = 22 V. Tomake the EMI filter well damped,Rd should be adequatelybelow3.2267Ω. In our design, we selectRd = 0.4Ω. To make2πfswCd 1/Rd, we selectCd = 3.3 mF.

We consider the worst case:ILo = 10 A, which occurswhen the output power is150 W. In this case, the magnitudeof the fundamental component ofis,ac is

i1s,ac =2ILo

πsin(2πfswt) = 6.3662sin(2πfswt). (14)

To make the ripple of the input current belowδ3 = 100 mA,we can selectLf andCf such that

40

(

lg (2πfsw)− lg

(

1√CfLf

))

≥ 20(

lg (6.3662)− lg(

δ32

))

(15)

from which we get

1√

CfLf

≤ 1.113× 105 rad/ sec . (16)

To be on the safe side, we selectCf = 20µF andLf = 9µH, which leads to 1√

CfLf

= 7.45× 104 rad/sec.

With Cf = 20µF,Lf = 9µH, Cd = 3.3mF andRd = 0.4Ω,the magnitude ofg(s) is plotted in Fig. 5. Clearly, this EMIfilter is a well-damped low-pass filter. Atfsw = 20 KHz, |g(s)|is −49 dB, and thus the ac component of the switch currentcan be well filtered, leading to very small ripples in the inputcurrent.

Fig. 7. Transient behavior of the output voltage, showing the transient limit.

Fig. 8. Steady-state waveform of the output voltage, showing the worst-casevoltage ripple.

C. Simulation Results

Using the above specified design parameters, we setV1 =32 V and d = 0.4688 to check the transient and steady-statewaveforms ofVo. The circuit schematic used for simulationis shown in Fig. 6. In this simulation, the load is first set as1.5Ω, and then it was changed to4.5Ω.

1) Output Voltage:As shown in Fig. 7, during the stepsbetween the minimum and maximum load, the maximumoutput voltage is about17.8 V. The steady-state waveformof Vo is plotted in Fig. 8, which shows thatVo,p−p = 8.1 mVand the average value is14.735 V.

2) Input Current:To see the worst-case input current ripple,we set the input voltage as 22 V,Ro = 1.5Ω andd = 0.6818.As shown in Fig. 9, the worst-case peak-to-peak value is27mA.

Fig. 9. Steady-state waveform of the input current, showingthe worst-caseripples.

3) Output Power:Fig. 10 shows the transient behavior ofthe current throughILo. Clearly, when the load is1.5Ω, theaveraged value is 10 A, leading to 150-W output power. Whenthe load is4.5Ω, the averaged value is 3.33 A, delivering50-

W power to the load. The maximum peak-to-peak current ofthis inductor is 1.2 A whenV1 = 32 V.

Fig. 10. Transient behavior of the current through output-stage inductorLo,showing the output power range.

4) Summary: The simulated performance parameters aresummarized in Table II. Clearly, the listed electrical parametersall meet the corresponding design requirements.

TABLE IISIMULATION RESULTS OF THE PROPOSED DESIGN.

Switching frequency 200 KHzInput voltage range 22 ∼ 32 VOutput power range 50 ∼ 150 VOutput voltage (static) 15 V±1.67%Maximum output voltage (transient) 17.8 V (+18.67%)Maximum output voltage ripple (p-p value) 8.1 mVMaximum input current ripple (p-p value) 27 mA

IV. ELECTRICAL AND THERMAL DEVICE SELECTION

A. Switch and Diode

1) Switch: The worst-case conduction loss of the switch is

Psw,on = dI2LoRds = d

(

Po

Vo

)2

Rds. (17)

whereRds is the drain-to-source resistance at the maximumallowable junction temperature.

The switching loss can be calculated as the sum of the lossduring the rise and fall time. Since the maximum drain-to-source voltage isV1 and the maximum current isILo = Po

Vo,

the switching loss is

Psw,rf =1

2V1

Po

Vo

(tr + tf ) fsw =Po

2d(tr + tf ) fsw. (18)

To make the total loss small, we should select a switchthat has small conduction resistance and small rise/fall time.In our design,IRFZ48N Power MOSFET is selected due tothe good tradeoff betweenRds and tr + tf . At the maximumallowable temperature175C, the drain-to-source resistance is

Rds = 0.014× 2.3 = 0.0322 Ω. (19)

Clearly shown in (17) and (18), the worst-case power losshappens whenPo = 150 W. With tr = 78 ns and tf =34ns, the worst-case conduction loss, switching loss and totalloss are plotted in Fig. 11 as functions of the duty ratio. Thesimulation results in Fig. 11 show that the maximum worst-case switch device loss is

Psw,worst−case = max (Psw,on + Psw,rf) = 5.0934 W, (20)

which occurs whend = 1532 .

0.45 0.5 0.55 0.6 0.65 0.71

2

3

4

5

6

d (duty ratio)

max

imum

wor

st−

case

pow

er lo

ss

conduction lossswitching losstotal loss

Fig. 11. Loss of the IRFZ48N Power MOSFET under different duty ratios.

2) Diode: Since the maximum reverse voltage is32 Vand the maximum forward current can be10 A, we select30CPQ45as our diode device. The conduction loss is

Pd,on = ILo(1− d)VF =Po

Vo

(1− d)VF , (21)

whereVF is the forward voltage at the maximum allowablejunction temperature. Clearly, the worst-case conductionloss isobtained whenPo = 150W andd = 15

32 . In this caseILo = 10A and VF = 0.4 F, leading to the worst-case conduction loss

max (Pd,on) = 2.12 W. (22)

The worst-case discharge loss due to the diode capacitancecan be calculated as

Pd,cap = fsw

∫ 32

0

CV dV ≈ 0.40 W (23)

which is very small compared with the conduction loss.Therefore, the worst-case diode power loss is

Pd,worst−case = max (Pd,on) + Pd,cap = 2.52 W. (24)

B. Passive Components: Capacitors

1) Cf : The simulation results show that the current throughCf can approach7 A, therefore use the20-µF CS4 capacitorfor the LC filter. The parasitic resistance of this capacitoris2.5 mΩ and the parasitic inductance is11 nH.

2) Cd: The maximum voltage acrossCd is around32 V(whenV1 = 32 V), and the maximum current can be around0.6 A, therefore we use the3.3-mF U767D capacitor. Theparasitic resistance of this capacitor is about11 mΩ, which isnegligible compared with the damping resistor.

3) Co: Simulation results show that the peak-to-peak cur-rent of this capacitor is around0.6 A and the averaged currentis 0. Since Vo = 15 V, we select the100-µF HD-seriescapacitor, which allows the simulated capacitor current.

C. Passive Components: Inductors

1) Lf : The maximum input current is

Iin,max =max (Po)

min V1)= 6.82 A. (25)

There is a constraint for the wire areaAwire by the maximumcurrent density:

Iin,max

Awire≤ 500 A/cm

2. (26)

The second constraint is that the maximum flux densityBmax

should be below the saturated flux densityBsat, i.e.,

Bmax =LfIin,max

NAc

< Bmax (27)

whereN is the turn number,Ac is the effective core area.Based on these two constraints, we select theRM10/I core

set, with AL = 250 nH andN = 6. The diameter of the wire(size-13 copper wire) is

dwire = 1.83 mm. (28)

The wire resistanceof the inductor is

RLf = N × lturn × ρcu,wire = 2.49 mΩ (29)

where lturn = 52 mm is the average length of turn, andρcu,wire = 7.99×10−3Ω/m is the resistivity of size-13 copperwire.

2) Lo: The output-stage inductorLo can be designed in asimilar way. For this inductor, we use theRM12/I core set,with AL = 315 nH andN = 10. We use the size-14 copperwire (diameter is1.63 mm). The resultingwire resistance is

RLo = N × lturn × ρcu,wire = 6.161 mΩ. (30)

3) Power Loss of Inductors:The inductor loss includes thewinding and core loss. The winding loss of inductorLf is

PLf,winding = I2LfRLf =

(

Po

V1

)2

RLf . (31)

WhenPo = 150 W andV1 = 22 V, we have the worst-casewinding loss forLf :

max (PLf,winding) = 6.822 × 0.00249 = 0.1158 W. (32)

For the inductorLf , we haveCM = 2.5×10−4, fsw = 2×105

Hz, α = 1.63, β = 2.45, Bac,peak ≈ 2.2282 × 10−3 T, andVcore = 4.31cm3, therefore, the core loss can be decided as

PLf,core = CMf2sw (Bac,peak)

βVcore = 0.15 mW, (33)

which is much smaller than the winding loss. Therefore, theworst-case loss ofLf is

PLf,worst−case = max (PLf,winding) + PLf,core = 0.116 W.(34)

Similarly, for the output-stage inductorLo the maximumwinding loss can be calculated as

max (PLo,winding) = 102 × 0.006161 = 0.6161 W. (35)

The core loss is

PLo,core = CMf2sw (Bac,peak)

βVcore = 7.80 mW. (36)

THE worst-case loss ofLo is

PLo,worst−case = max (PLf,winding) + PLf,core = 0.6239 W.(37)

4) Temperature Rise of Inductors:For the inductorLf , themaximum temperature rise is

∆TLf,max = PLf,worst−case × Zθ,RM10 = 3.48C. (38)

The maximum temperature rise for the inductorLo is

∆TLo,max = PLo,worst−case × Zθ,RM12 = 14.35C. (39)

D. Heat Sinks

The junction temperature of a power device can be ex-pressed as a function of the power dissipationPdiss, ambienttemperatureTA, junction-to-case thermal resistanceRθ,JC ,case-to-sink thermal resistanceRθ,CS and sink-to-ambientthermal resistanceRθ,SA:

TJ = TA + Pdiss (Rθ,JC +Rθ,CS +Rθ,SA) . (40)

Since our design should work for the worst case, we assumethatTA = 50C, and we require the junction temperature is atleast25C below the maximum allowable temperature at thedevice junction specified by the data sheet.

1) Heat Sink for the Switch:For the IRFZ48N PowerMOSFET, the calculated worst-case device loss is5.0943W. From the data sheet we haveRθ,JC = 1.15C/W,Rθ,CS = 0.50C/W, and the specified maximum allowablejunction temperature is 175C, therefore, the heat sink thermalresistance should be

Rθ,SA ≤ 175− 25− 50

5.0943− 1.15− 0.5 = 17.98C/W. (41)

Therefore, we have many choices for the heat sink. In ourdesign, we selectML73/1.5 as the heat sink, the thermalresistance of which is11.0C/W.

2) Heat Sink for the Diode:For the 30CPQ45 Schot-tky Diode, the calculated worst-case power loss is2.52W. From the data sheet we haveRθ,JC = 1.10C/W,Rθ,CS = 0.24C/W, and the specified maximum allowablejunction temperature is 150C, therefore, the heat sink thermalresistance should be

Rθ,SA ≤ 150− 25− 50

2.52− 1.10− 0.24 = 28.42C/W.

(42)

Therefore, we have many choices for the heat sink. In ourdesign, we useML24 to remove the heat of the diode, thethermal resistance of which is16.7C/W.

E. Power Efficiency

The power efficiencycan be estimated as

η =Po

Po + Ploss(43)

wherePloss is the total power loss which can be calculated as

Ploss = Psw,on + Psw,rf + Pd,on + Pd,cap + PLf,winding+PLf,core + PLo,winding + PLo,core.

(44)

In our estimation, we use the worst-case capacitance dischargeloss (i.e., 0.40 W) forPd,cap. According to (17), (18), (21),(31)and (35), we know that the power efficiencyη depends on theduty ratiod and output powerPo. Fig. 12 has plottedη as afunction of d andPo. From the simulation results we knowthat the minimum power efficiency is

ηmin = 94.59%. (45)

Note that the practical minimum power efficiency can belarger, since in our calculation the worst-casePd,cap is used.

Fig. 12. Power efficiency of the buck converter under different duty ratioand output power values.

−3000 −2500 −2000 −1500 −1000 −500−2

−1

0

1

2x 10

4

real

imag

p1

p2

p3

Fig. 13. The voltage-mode controlled system is stable, sincethe real part ofits poles are all negative for anyRo ∈ [1.5, 4.5]Ω.

V. FEEDBACK CONTROL

This section designs a voltage-model feedback controller forthe buck converter such that:

1) The averaged output voltage can stay at15 V when thereis a step change in the input voltage;

2) The closed-loop system is stable when the load resistorvaries in the range of1.5 ∼ 4.5Ω.

A. State-Space Model

From Fig. 1, we can set up a state-space model for the buckconverter:

LodiLo

dt= q(t)v1 − vo(t)

Codvo

dt= iLo(t)− vo(t)

Ro.

(46)

Averaging the above state-space model we have

LodiLo

dt= dv1 − vo

Codvo

dt= iLo − vo

Ro

(47)

whered = q(t).At the nominal point, we havevo = Vo = 15 V, v1 = V1 =

27V , iLo = ILo = Vo

Ro, d = D = Vo

V1

= 1527 , and the left-hand

side of (47) is zero. Now assume that the system is perturbedaway from the equilibrium point:v1 = V1 + v1, d = D + d,vo = Vo + vo and iLo = ILo + iL. By linearizing (47), weobtained the linearized model:

diLo

dt= 1

Lo

(

Dv1 + V1d− vo

)

dvo

dt= 1

Co

(

iLo − vo

Ro

)

.(48)

In Laplace domain we have(

s2LoCo + sLo

Ro

+ 1

)

vo(s) = Dv1(s) + V1d(s), (49)

from which we get two transfer functions

H1(s) =vo(s)

v1(s)=

D(

s2LoCo + sLo

Ro+ 1

) (50)

and

H2(s) =vo(s)

d(s)=

V1(

s2LoCo + sLo

Ro+ 1

) . (51)

B. PI Controller Design

We need to design a PI controller (of course we can alsouse a PID controller)

K(s) = a1 +a2s, (52)

such that

d(s) = K(s) (vo(s)− vref(s)) , (53)

and the close-loop system is stable and its step responsey(t)approaches0 as t → ∞. Since we wantvo(s) = 0, we setvref = 0. Substitute (53) into (49) we get the transfer functionof the close-loop system:

G(s) =sD

(

s3LoCo + s2 Lo

Ro+ s (1− V1a1)− V1a2

) . (54)

From (54) we know that due to the integrator in thecontroller, the step responsey(t) is zero whent → ∞ sinceG(0) = 0. If the system is stable, its polesp1, p2, p3 ∈ C

−,which leads to

1− V1a1 > 0 and V1a2 < 0. (55)

Therefore, we should selecta1 and a2 such thata1 is smalland a2 < 0 to make the system stable forRo ∈ [1.5, 4.5]Ω.A simple MATLAB experiment shows that if we selecta1 =0.008 anda2 = −20, the system is stable under load variation.To see this, the three poles are plotted in Fig. 13 as the loadresistorRo changes from1.5Ω to 4.5Ω. Clearly, under loadvariations all poles are located on the left-hand rise (LHS)ofthe complex plane, thus the close-loop system is guaranteedstable.

C. Results

1) Whole System Structure:The block diagram of the buckconverter with the voltage-mode PI controller is given inFig. 14. The block diagram includes the following blocks

• H1(s), the signal path fromv1(s) to vo(s), marked inblack;

• H2(s), the signal path from the controlled duty ratiod(s)to vo(s) marked in blue;

• K(s), the PI controller block which transfers the outputoffset to the control signald(s), hilighted in red.

TABLE IIIDEVICE SUMMARY.

Devices Component Selection RemarksSwitch IRFZ48N MOSFET worst-case loss 5.0934 W, break-downVDS 55VDiode 30CPQ45 Schottky Diode worst-case loss 2.52 W, max. reverse voltage45 VRd (resistor in the damping leg of the EMI filter) 0.4ΩCf (capacitor for the input filter) CSZ 20.0µF parasitic resistance0.0025Ω, parasitic inductance11 nHCd (capacitor for the damping leg in EMI filter) U767D 3.3 mF parasitic resistance0.011ΩCo (capacitor at output stage) HD Series100µF parasitic resistance0.074ΩLf (inductor for EMI filter) 9µH, RM10/I core AL = 250 nH, turn# 6, size-13 copper wire (diameter: 1.83 mm),

wire resistance2.49mΩ, max. loss 0.116 W, temperature rise 3.48CLo (inductor at output stage) 31.5µH, RM12/I core AL = 315 nH, turn# 10, size-14 copper wire (diameter: 1.68 mm),

wire resistance6.161mΩ, max. loss 0.6239 W, temperature rise 14.35CHeat sink for MOSFET switch ML73/1.5 Rθ = 11.0C/WHeat sink for diode ML24 Rθ = 16.7C/W

Fig. 14. MATLAB Simulink model of the whole buck converter withvoltage-mode PI controller.

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1−1

0

1

2

3

4

5

6

time (s)

$\ha

t v_o

$

Fig. 15. Time-domain response when the input steps from27 V to 32 V.The y-axis data meansvo(t), the deviation of the averaged output from thedesired value15 V, which decays to0 within 0.01 second.

2) Simulation Result:We use a step input of magnitude5Vto perform the time-domain simulation, which means a step ofthe DC input from the nominal value27 V to the maximumvalue32V. Clearly shown in Fig. 15, under the input step theoffset of the averaged output decays to zero (andvo returnsto the desired valueVo = 15V) within 0.01 second.

VI. SUMMARY

A. Device Selection Summary

The electrical and thermal devices, including their parasiticeffects, power loss and temperature rise are summarized inTable III.

Fig. 16. The finalized circuit that includes parasitic effects.

B. Performance Summary

Now we include device parasitics (as shown in Fig. 16) toredo the simulation. The simulation results are summarizedinTable IV. Since the break-down drain-to-source voltage of theselected IRFZ48N MOSFET is 55 V, and the the maximumreverse voltage of the selected 30CPQ45 Schottky Diode is45 V, this circuit can survive under44-V input transient limit.Clearly, the results are very close the our previous design,andall design specifications are satisfied.

TABLE IVSIMULATION RESULTS OF THE PROPOSED DESIGN, INCLUDING PARASITIC

EFFECTS.

Switching frequency 200 KHzInput voltage range 22 ∼ 32 VTolerate44-V input transient limit? yesOutput power range 50 ∼ 150 VOutput voltage (static) 15 V±1.33%Maximum output voltage (transient) 17.75 V (+18.33%)Maximum output voltage ripple (p-p value) 9 mVMaximum input current ripple (p-p value) 31 mAMinimum efficiency > 94.59%