25 MIPS, 8 kB Flash, 12-Bit ADC, 20-Pin Automotive MCU · Internal Voltage Reference ... -Pipelined...

Click here to load reader

Transcript of 25 MIPS, 8 kB Flash, 12-Bit ADC, 20-Pin Automotive MCU · Internal Voltage Reference ... -Pipelined...

Copyright © 2006 by Silicon Laboratories 9.5.2006

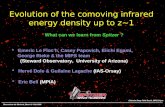

SPI Bus

Timers 0,1,2

XTAL1

XTAL2

Precision Oscillator

±0.5%

P0.0/VREFUART0 P0

Drv

Port 0,1Latch

8051

Core

256 bytesRAM

8 kB Flash

System Clock

ExternalOscillatorCircuit

CROSSBAR

+-CP0

SFR Bus PCA(3 ch.)

LIN 2.0

P0.1P0.2P0.3P0.4P0.5P0.6/C2DP0.7/XTAL1

VREF (2.5V)

VREF

TEMPSENSOR

AMUX

5V ADC200 ksps

(12-Bit)

Reference Voltage

VDD

P1.0/XTAL2P1

Drv

P1.1P1.2P1.3P1.4P1.5P1.6P1.7

VREGIN

GND

RST/C2CK

WDT

Reset

VDDMonitor

2.5 V Regulator

(GPIO)

(2.7-5.25 V)(VDD)

Debug HWC2D

VREGOUT

C8051F53025 MIPS, 8 kB Flash, 12-Bit ADC, 20-Pin Automotive MCU

Analog Peripherals12-Bit ADC, 5 V input signal; up to 16 external inputs- ±1 LSB INL; guaranteed monotonic- Programmable throughput up to 200 ksps- Data-dependent windowed interrupt generator- Programmable gain maximizes input signal spanBuilt-in Temperature Sensor (±3 °C)One ComparatorInternal Voltage ReferencePrecision VDD Monitor/Brown-out DetectorOn-Chip Debug- On-chip debug circuitry facilitates full speed, non-intrusive in-system

debug (no emulator required)- Provides breakpoints, single stepping, watch-points- Inspect/modify memory, registers, and stack- Superior performance to emulation systems using ICE-chips, target

pods, and sockets

Supply Voltage: 2.7 to 5.25 V- Typical operating current: 7 mA at 25 MHz at 5.0 V- Multiple power saving sleep and shutdown modes

Temperature Range: –40 to +125 °C

High-Speed 8051 µC Core- Pipelined instruction architecture; executes 70% of instructions in 1 or 2

system clocks- Up to 25 MIPS throughput with 25 MHz system clock- Expanded interrupt handler

Memory- 8 kB Flash; in-system programmable; flexible security features- 256 bytes data RAM

LIN 2.0- Master or slave operation using dedicated hardware (not software imple-

mentation with UART)

Digital Peripherals- Up to 16 digital I/O; all are 5 V push-pull- Programmable 16-bit counter array with three capture/compare modules- Three general-purpose 16-bit counter/timers- Dedicated watchdog timer; bidirectional reset- Real-time clock mode using timer 3 or PCA

Clock Sources- High-precision internal programmable oscillator up to 25 MHz- External oscillator: Crystal, RC, C, or Clock

Packages- 20-Pin TSSOP and 20-Pin QFN (4x4 mm)

Ordering Part Numbers- C8051F530-IT (TSSOP)- C8051F530-IM (QFN)

Copyright © 2006 by Silicon Laboratories 9.5.2006Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders

C8051F53025 MIPS, 8 kB Flash, 12-Bit ADC, 20-Pin Automotive MCU

Parameter Conditions Min Typ Max UnitsGlobal CharacteristicsSupply Voltage (VREGIN) 2.7 — 5.25 VSupply Current (CPU active) VREGIN = 2.7–5.0 V

Clock = 25 MHzClock = 1 MHzClock = 32 kHz; VDD monitor enabled

———

70.833

———

mAmAµA

Supply Current (shutdown) Oscillator not running; VDD monitor disabled

— 0.2 — µA

Clock Frequency Range dc — 25 MHzA/D ConverterResolution 12 bitsIntegral Nonlinearity — — ±1 LSBDifferential Nonlinearity Guaranteed monotonic — — ±1 LSBSignal-to-Noise Plus Distortion — 68 — dBThroughput Rate — — 200 kspsInput Voltage Range 0 — VREF VFlashEndurance 40K 150K — E/W cyclesErase Cycle Time 10 12 14 msWrite Cycle Time 40 50 60 µs

Selected Electrical Specifications(TA = –40 to +125 C°, VREGIN = 2.7 V unless otherwise specified)

Package Information

18

1

E

D

A2

AA

1e

A3

E2

Re

L

Bottom View

Side View

2

3

5

6 7 10

15

14

12

11

20 19 16

E2 2

D2

8

13

D22

4 x

e

4 x e

DETAIL 1

DETAIL 1AA

BB

CC

DD

b 4

917

MM

0.80 0.90 1.00AMIN TYP MAX

0 0.02 0.05A10 0.65 1.00A2

0.25A30.18 0.23 0.30b

4.00D2.00 2.15 2.35D2

0.435AA0.435BB

4.00EE2

0.5e

0.18CC

0.45 0.55 0.65L20N

0.09R

5ND5NE

0.18DD

2.00 2.15 2.35

c

D

A1

A

b

E1 E

e

See Detail G

1 2 3ddd C B A

A

C

20

bbb C B AM

B

L

θ1

Detail G

— — 1.20A0.05 — 0.15A10.19 — 0.30b0.09 — 0.20c6.40 6.50 6.60D

0.65 BSCe6.40 BSCE

4.30 4.40 4.50E10.45 0.60 0.75L0° — 8°?1

0.10bbb0.20ddd

Min Typ MaxMM

QFN

TSSOP

C8051F530DK Development Kit