120V-100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY · PDF filetda7293 120v - 100w dmos audio...

Transcript of 120V-100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY · PDF filetda7293 120v - 100w dmos audio...

TDA7293

120V - 100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

VERY HIGH OPERATING VOLTAGE RANGE(50V)DMOS POWER STAGEHIGH OUTPUT POWER (100W @ THD =10%, RL = 8, VS = 40V)MUTING/STAND-BY FUNCTIONSNO SWITCH ON/OFF NOISEVERY LOW DISTORTIONVERY LOW NOISESHORT CIRCUIT PROTECTIONTHERMAL SHUTDOWNCLIP DETECTORMODULARITY (MORE DEVICES CAN BEEASILY CONNECTED IN PARALLEL TODRIVE VERY LOW IMPEDANCES)

DESCRIPTIONThe TDA7293 is a monolithic integrated circuit inMultiwatt15 package, intended for use as audioclass AB amplifier in Hi-Fi field applications(Home Stereo, self powered loudspeakers, Top-

class TV). Thanks to the wide voltage range andto the high out current capability it is able to sup-ply the highest power into both 4 and 8 loads.The built in muting function with turn on delaysimplifies the remote operation avoiding switchingon-off noises.Parallel mode is made possible by connectingmore device through of pin11. High output powercan be delivered to very low impedance loads, sooptimizing the thermal dissipation of the system.

December1999

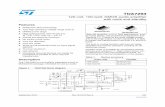

IN- 2R2

680

C2 22F

C1 470nFIN+

R1 22K

3

R3 22K

-

+

MUTE

STBY

4

VMUTE

VSTBY

10

9

SGND

MUTE

STBY

R4 22K

THERMAL SHUTDOWN

S/C PROTECTION

R5 10K

C3 10F C4 10F

1

STBY-GND

C5 22F

7 13

14

6

158

-Vs -PWVs

BOOTSTRAP

OUT

+PWVs+Vs

C9 100nF C8 1000F

-VsD97AU805A

+VsC7 100nF C6 1000F

BUFFER DRIVER

11

BOOT LOADER12

5VCLIP

CLIP DET

(*)

(*) see Application note (**) for SLAVE function

(**)

Figure 1: Typical Application and Test Circuit

Multiwatt15ORDERING NUMBER: TDA7293V

MULTIPOWER BCD TECHNOLOGY

1/13

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

VS Supply Voltage (No Signal) 60 VV1 VSTAND-BY GND Voltage Referred to -VS (pin 8) 90 V

V2 Input Voltage (inverting) Referred to -VS 90 V

V2 - V3 Maximum Differential Inputs 30 VV3 Input Voltage (non inverting) Referred to -VS 90 V

V4 Signal GND Voltage Referred to -VS 90 V

V5 Clip Detector Voltage Referred to -VS 120 V

V6 Bootstrap Voltage Referred to -VS 120 V

V9 Stand-by Voltage Referred to -VS 120 V

V10 Mute Voltage Referred to -VS 120 V

V11 Buffer Voltage Referred to -VS 120 V

V12 Bootstrap Loader Voltage Referred to -VS 100 V

IO Output Peak Current 10 A

Ptot Power Dissipation Tcase = 70C 50 WTop Operating Ambient Temperature Range 0 to 70 C

Tstg, Tj Storage and Junction Temperature 150 C

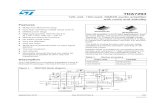

1

2

3

4

5

6

7

9

10

11

8

BUFFER DRIVER

MUTE

STAND-BY

-VS (SIGNAL)

+VS (SIGNAL)

BOOTSTRAP

CLIP AND SHORT CIRCUIT DETECTOR

SIGNAL GROUND

NON INVERTING INPUT

INVERTING INPUT

STAND-BY GND

TAB CONNECTED TO PIN 8

13

14

15

12

-VS (POWER)

OUT

+VS (POWER)

BOOTSTRAP LOADER

D97AU806

PIN CONNECTION (Top view)

QUICK REFERENCE DATA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

VS Supply Voltage Operating 12 50 VGLOOP Closed Loop Gain 26 40 dB

PtotOutput Power VS = 45V; RL = 8; THD = 10% 140 W

VS = 30V; RL = 4; THD = 10% 110 WSVR Supply Voltage Rejection 75 dB

THERMAL DATA

Symbol Description Typ Max Unit

Rth j-case Thermal Resistance Junction-case 1 1.5 C/W

TDA7293

2/13

ELECTRICAL CHARACTERISTICS (Refer to the Test Circuit VS = 40V, RL = 8, Rg = 50 ;Tamb = 25C, f = 1 kHz; unless otherwise specified).

Symbol Parameter Test Condition Min. Typ. Max. Unit

VS Supply Range 12 50 VIq Quiescent Current 30 mA

Ib Input Bias Current 0.3 1 AVOS Input Offset Voltage -10 10 mV

IOS Input Offset Current 0.2 APO RMS Continuous Output Power d = 1%:

RL = 4; VS = 29V,8080

W

d = 10%RL = 4 ; VS = 29V

100100

W

d Total Harmonic Distortion (**) PO = 5W; f = 1kHzPO = 0.1 to 50W; f = 20Hz to 15kHz

0.0050.1

%%

ISC Current Limiter Threshold 6.5 A

SR Slew Rate 15 V/sGV Open Loop Voltage Gain 80 dB

GV Closed Loop Voltage Gain (1) 30 dB

eN Total Input Noise A = curvef = 20Hz to 20kHz

12 5

VV

Ri Input Resistance 100 kSVR Supply Voltage Rejection f = 100Hz; Vripple = 0.5Vrms 75 dB

TS Thermal Protection DEVICE MUTED 150 CDEVICE SHUT DOWN 160 C

STAND-BY FUNCTION (Ref: to pin 1)

VST on Stand-by on Threshold 1.5 V

VST off Stand-by off Threshold 3.5 V

ATTst-by Stand-by Attenuation 70 90 dB

Iq st-by Quiescent Current @ Stand-by 0.5 mA

MUTE FUNCTION (Ref: to pin 1)

VMon Mute on Threshold 1.5 V

VMoff Mute off Threshold 3.5 V

ATTmute Mute AttenuatIon 60 80 dB

CLIP DETECTOR

Duty Duty Cycle ( pin 5) THD = 1% ; RL = 10K to 5V 10 %THD = 10% ;RL = 10K to 5V

40 %

ICLEAK PO = 50W 1 ASLAVE FUNCTION pin 4 (Ref: to pin 8 -VS)

VSlave SlaveThreshold 1 V

VMaster Master Threshold 3 V

Note (1): GVmin 26dB

Note: Pin 11 only for modular connection. Max external load 1M/10 pF, only for test purpose

Note (**): Tested with optimized Application Board (see fig. 2)

TDA7293

3/13

Figure 2: Typical Application P.C. Board and Component Layout (scale 1:1)

TDA7293

4/13

APPLICATION SUGGESTIONS (see Test and Application Circuits of the Fig. 1)The recommended values of the external components are those shown on the application circuit of Fig-ure 1. Different values can be used; the following table can help the designer.

COMPONENTS SUGGESTED VALUE PURPOSE LARGER THANSUGGESTEDSMALLER THAN

SUGGESTED

R1 (*) 22k INPUT RESISTANCE INCREASE INPUTIMPEDANCE

DECREASE INPUTIMPEDANCE

R2 680 CLOSED LOOP GAINSET TO 30dB (**)

DECREASE OF GAIN INCREASE OF GAIN

R3 (*) 22k INCREASE OF GAIN DECREASE OF GAIN

R4 22k ST-BY TIMECONSTANT

LARGER ST-BYON/OFF TIME

SMALLER ST-BYON/OFF TIME;

POP NOISE

R5 10k MUTE TIMECONSTANT

LARGER MUTEON/OFF TIME

SMALLER MUTEON/OFF TIME

C1 0.47F INPUT DCDECOUPLING

HIGHER LOWFREQUENCY

CUTOFF

C2 22F FEEDBACK DCDECOUPLING

HIGHER LOWFREQUENCY

CUTOFF

C3 10F MUTE TIMECONSTANT

LARGER MUTEON/OFF TIME

SMALLER MUTEON/OFF TIME

C4 10F ST-BY TIMECONSTANT

LARGER ST-BYON/OFF TIME

SMALLER ST-BYON/OFF TIME;

POP NOISE

C5 22FXN (***) BOOTSTRAPPING SIGNALDEGRADATION ATLOW FREQUENCY

C6, C8 1000F SUPPLY VOLTAGEBYPASS

C7, C9 0.1F SUPPLY VOLTAGEBYPASS

DANGER OFOSCILLATION

(*) R1 = R3 for pop optimization

(**) Closed Loop Gain has to be 26dB

(***) Multiplay this value for the number of modular part connected

MASTER

UNDEFINED

SLAVE

-VS +3V

-VS +1V

-VSD98AU821

Slave function: pin 4 (Ref to pin 8 -V S) Note:If in the application, the speakers are connectedvia long wires, it is a good rule to add betweenthe output and GND, a BoucherotCell, in order toavoid dangerous spurious oscillations when thespeakers terminal are shorted.The suggested Boucherot Resistor is 3.9/2Wand the capacitor is 1F.

TDA7293

5/13

INTRODUCTIONIn consumer electronics, an increasing demandhas arisen for very high power monolithic audioamplifiers able to match, with a low cost, the per-formance obtained from the best discrete de-signs.The task of realizing this linear integrated circuitin conventional bipolar technology is made ex-tremely difficult by the occurence of 2nd break-down phoenomenon. It limits the safe operatingarea (SOA) of the power devices, and, as a con-sequence, the maximum attainable output power,especially in presence of highly reactive loads.Moreover, full exploitation of the SOA translatesinto a substantial increase in circuit and layoutcomplexity due to the need of sophisticated pro-tection circuits.To overcome these substantial drawbacks, theuse of power MOS devices, which are immunefrom secondary breakdown is highly desirable.The device described has therefore been devel-oped in a mixed bipolar-MOS high voltage tech-nology called BCDII 100/120.

1) Output StageThe main design task in developping a power op-erational amplifier, independently of the technol-ogy used, is that of realization of the output stage.The solution shown as a principle shematic byFig3 represents the DMOS unity - gain outputbuffer of the TDA7293.This large-signal, high-power buffer must be ca-pable of handling extremely high current and volt-age levels while maintaining acceptably low har-monic distortion and good behaviour over

frequency response; moreover, an accurate con-trol of quiescent current is required.A local linearizing feedback, provided by differen-tial amplifier A, is used to fullfil the above require-ments, allowing a simple and effective quiescentcurrent setting.Proper biasing of the power output transistorsalone is however not enough to guarantee the ab-sence of crossover distortion.While a linearization of the DC transfer charac-teristic of the stage is obtained, the dynamic be-haviour of the system must be taken into account.A significant aid in keeping the distortion contrib-uted by the final stage as low as possible is pro-vided by the compensation scheme, which ex-ploits the direct connection of the Miller capacitorat the amplifiers output to introduce a local ACfeedback path enclosing the output stage itself.

2) ProtectionsIn designing a power IC, particular attention mustbe reserved to the circuits devoted to protectionof the device from short circuit or overload condi-tions.Due to the absence of the 2nd breakdown