Hardware implementation

4

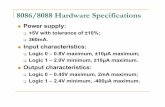

Hardware implementation RS 232 D SP D/A U serinterface 1/f α noise PC • DSP: ADSP-2181, 16 bit, fixed point, 40MH • D/A: 300kHz, 14 bit • PC: development environment: LabVIEW

description

Hardware implementation. DSP: ADSP-2181, 16 bit, fixed point, 40MHz D/A: 300kHz, 14 bit PC: development environment: LabVIEW. Solutions using fixed - point arithmetic. }. Need to optimise the coefficients of the filters to exploit the available numerical range. Limited precision - PowerPoint PPT Presentation

Transcript of Hardware implementation

Hardware implementation

RS 232 DSP D/A

User interface

1/f α

noise

PC

• DSP: ADSP-2181, 16 bit, fixed point, 40MHz• D/A: 300kHz, 14 bit• PC: development environment: LabVIEW

Solutions using fixed-point arithmetic

Whitenoise

Ab1, f1

Ab2, f3

Ab3, f3

.

.

.

+

∙ A1/Ab1

∙ A1/Ab1

∙ A1/Ab1

.

.

.

1/f α

noise

•Limited precision

•Saturation

}Need to optimise the coefficients of the filters to exploit the available numerical range

Algorithm

Interrupt

Random number

Filters

D/A conversion

Return

mcxax nn mod)(1

niininini yCxDxDy ,11, 001

i

nin yY 1,1

Features

• Flexible 1/f α noise generator

• Digital noise generation (DSP)

• Analog output (D/A conversion)

• Stand-alone or host computer controlled

• High accuracy

• Easy upgrade in speed, accuracy