Critique this PDA for L= { u u R v v R : u ∈ {0,1}* and v ∈ {0,1}+ }

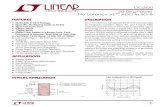

FEATURES DESCRIPTIO U - Analog Devices · 2020. 2. 1. · LTC3703-5 1 37035fa APPLICATIO S U...

Transcript of FEATURES DESCRIPTIO U - Analog Devices · 2020. 2. 1. · LTC3703-5 1 37035fa APPLICATIO S U...

-

LTC3703-5

137035fa

APPLICATIO SU

DESCRIPTIO

U

FEATURES

TYPICAL APPLICATIO

U

■ High Voltage Operation: Up to 60V■ Large 1Ω Gate Drivers (with 5V Supply)■ No Current Sense Resistor Required■ Step-Up or Step-Down DC/DC Converter■ Dual N-Channel MOSFET Synchronous Drive■ Excellent Line and Load Transient Response■ Programmable Constant Frequency: 100kHz to

600kHz■ ±1% Reference Accuracy■ Synchronizable up to 600kHz■ Selectable Pulse Skip Mode Operation■ Low Shutdown Current: 25µA Typ■ Programmable Current Limit■ Undervoltage Lockout■ Programmable Soft-Start■ 16-Pin Narrow SSOP and 28-Pin SSOP Packages

The LTC®3703-5 is a synchronous step-down switchingregulator controller that can directly step-down voltagesfrom up to 60V input, making it ideal for telecom and au-tomotive applications. The LTC3703-5 drives external logiclevel N-channel MOSFETs using a constant frequency (upto 600kHz), voltage mode architecture.

A precise internal reference provides 1% DC accuracy. Ahigh bandwidth error amplifier and patented* line feedforward compensation provide very fast line and loadtransient response. Strong 1Ω gate drivers allow theLTC3703-5 to drive multiple MOSFETs for higher currentapplications. The operating frequency is user program-mable from 100kHz to 600kHz and can also be synchro-nized to an external clock for noise-sensitive applications.Current limit is programmable with an external resistorand utilizes the voltage drop across the synchronousMOSFET to eliminate the need for a current sense resistor.For applications requiring up to 100V operation, refer tothe LTC3703 data sheet.

60V SynchronousSwitching Regulator Controller

Efficiency vs Load Current

High Efficiency High Voltage Step-Down Converter

LTC3703-5

MODE/SYNC

FSET

COMP

FB

IMAX

INV

RUN/SS

GND

VIN

BOOST

TG

SW

VCC

DRVCC

BG

BGRTN

22µF×2

1000pF

2200pF

10k

100Ω 113k1%

21.5k1% 10Ω

12k

30k

0.1µF

VIN6V TO 60V

8µH

D1MBR1100

VOUT5V5A

270µF16V

MMDL770T1

VCC5V

0.1µF

37035 TA04

10µF

1µF

+

+

+

Si7850DP

Si7850DP

22µF

470pF

LOAD CURRENT (A)0

EFFI

CIEN

CY (%

)

100

95

90

85

804

37053 TA04b

1 2 3 5

VIN = 12V

VIN = 42V

VIN = 24V

■ 48V Telecom and Base Station Power Supplies■ Networking Equipment, Servers■ Automotive and Industrial Control

PARAMETER LTC3703-5 LTC3703Maximum VIN 60V 100VMOSFET Gate Drive 4.5V to 15V 9.3V to 15VVCC UV+ 3.7V 8.7VVCC UV– 3.1V 6.2V

, LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.*U.S. Patent Numbers: 5408150, 5055767, 6677210, 5847554, 5481178, 6304066, 6580258;Others Pending.

-

LTC3703-5

237035fa

Supply VoltagesVCC, DRVCC .......................................... –0.3V to 15V(DRVCC – BGRTN), (BOOST – SW) ...... –0.3V to 15VBOOST (Continuous) ............................ –0.3V to 85VBOOST (400ms) ................................... –0.3V to 95VBGRTN ...................................................... –5V to 0V

VIN Voltage (Continuous) .......................... –0.3V to 70VVIN Voltage (400ms) ................................. –0.3V to 80VSW Voltage (Continuous) ............................ –1V to 70VSW Voltage (400ms) ................................... –1V to 80VRun/SS Voltage .......................................... –0.3V to 5V

ABSOLUTE AXI U RATI GS

W WW U

(Note 1)

ELECTRICAL CHARACTERISTICS The ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at TA = 25°C. VCC = DRVCC = VBOOST = VIN = 5V, VMODE/SYNC = VINV = VSW =BGRTN = 0V, RUN/SS = IMAX = open, RSET = 25k, unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITSVCC, DRVCC VCC, DRVCC Supply Voltage ● 4.1 15 VVIN VIN Pin Voltage ● 60 VICC VCC Supply Current VFB = 0V ● 1.7 2.5 mA

RUN/SS = 0V 25 40 µAIDRVCC DRVCC Supply Current (Note 5) 0 5 µA

RUN/SS = 0V 0 5 µAIBOOST BOOST Supply Current (Note 5) ● 360 500 µA

RUN/SS = 0V 0 5 µA

MODE/SYNC, INV Voltages ....................... –0.3V to 15VfSET, FB, IMAX, COMP Voltages ................... –0.3V to 3VDriver Outputs

TG ................................ SW – 0.3V to BOOST + 0.3VBG ........................... BGRTN – 0.3V to DRVCC + 0.3V

Peak Output Current

-

LTC3703-5

337035fa

Note 1: Absolute Maximum Ratings are those values beyond which the lifeof a device may be impaired.Note 2: The LTC3703-5 is guaranteed to meet performance specificationsfrom 0°C to 70°C. Specifications over the –40°C to 85°C operatingtemperature range are assured by design, characterization and correlationwith statistical process controls. The LTC3703I-5 is guaranteed over the full–40°C to 125°C operating junction temperature range.Note 3: TJ is calculated from the ambient temperature TA and powerdissipation PD according to the following formula:

LTC3703-5: TJ = TA + (PD • 100 °C/W) G PackageNote 4: The LTC3703-5 is tested in a feedback loop that servos VFB to the

ELECTRICAL CHARACTERISTICS The ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at TA = 25°C. VCC = DRVCC = VBOOST = VIN = 5V, VMODE/SYNC = VINV = VSW =BGRTN = 0V, RUN/SS = IMAX = open, RSET = 25k, unless otherwise specified.

reference voltage with the COMP pin forced to a voltage between 1V and 2V.Note 5: The dynamic input supply current is higher due to the powerMOSFET gate charging being delivered at the switching frequency(QG • fOSC).Note 6: Guaranteed by design. Not subject to test.Note 7: This IC includes overtemperature protection that is intended toprotect the device during momentary overload conditions. Junctiontemperature will exceed 125°C when overtemperature protection is active.Continuous operation above the specified maximum operating junctiontemperature may impair device reliability.Note 8: RDS(ON) guaranteed by correlation to wafer level measurement.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITSMain Control LoopVFB Feedback Voltage (Note 4) 0.792 0.800 0.808 V

● 0.788 0.812 V∆VFB, LINE Feedback Voltage Line Regulation 5V < VCC < 15V (Note 4) ● 0.007 0.05 %/V∆VFB, LOAD Feedback Voltage Load Regulation 1V < VCOMP < 2V (Note 4) ● 0.01 0.1 %VMODE/SYNC MODE/SYNC Threshold MODE/SYNC Rising 0.75 0.8 0.87 V∆VMODE/SYNC MODE/SYNC Hysteresis 20 mVIMODE/SYNC MODE/SYNC Current 0 ≤ VMODE/SYNC ≤ 15V 0 1 µAVINV Invert Threshold 1 1.5 2 VIINV Invert Current 0 ≤ VINV ≤ 15V 0 1 µAIVIN VIN Sense Input Current VIN = 60V 80 130 µA

RUN/SS = 0V, VIN = 10V 0 1 µAIMAX IMAX Source Current VIMAX = 0V 10.5 12 13.5 µAVOS, IMAX VIMAX Offset Voltage |VSW| – VIMAX at IRUN/SS = 0µA – 25 10 55 mVVRUN/SS Shutdown Threshold 0.7 0.9 1.2 VIRUN/SS RUN/SS Source Current RUN/SS = 0V 2.3 3.8 5.3 µA

Maximum RUN/SS Sink Current |VSW| – VIMAX > 100mV 9 17 25 µAVUV Undervoltage Lockout VCC Rising ● 3.4 3.7 4.1 V

VCC Falling ● 2.8 3.1 3.4 VHysteresis ● 0.45 0.65 0.85 V

OscillatorfOSC Oscillator Frequency RSET = 25kΩ 270 300 330 kHzfSYNC External Sync Frequency Range 100 600 kHztON, MIN Minimum On-Time 200 nsDCMAX Maximum Duty Cycle f < 200kHz 89 93 96 %DriverIBG, PEAK BG Driver Peak Source Current 0.75 1 ARBG, SINK BG Driver Pull-Down RDS, ON (Note 8) 1.2 1.8 ΩITG, PEAK TG Driver Peak Source Current 0.75 1 ARTG, SINK TG Driver Pull-Down RDS, ON (Note 8) 1.2 1.8 ΩFeedback AmplifierAVOL Op Amp DC Open Loop Gain (Note 4) 74 85 dBfU Op Amp Unity Gain Crossover Frequency (Note 6) 25 MHzIFB FB Input Current 0 ≤ VFB ≤ 3V 0 1 µAICOMP COMP Sink/Source Current ±5 ±10 mA

-

LTC3703-5

437035fa

TYPICAL PERFOR A CE CHARACTERISTICS

UW

Efficiency vs Input Voltage Efficiency vs Load Current Load Transient Response

VCC Current vs VCC Voltage VCC Current vs TemperatureVCC Shutdown Current vs VCCVoltage

VCC Shutdown Currentvs Temperature

Reference Voltagevs Temperature

Normalized Frequencyvs Temperature

TEMPERATURE (°C)–60 –40 –20 0 60 100 120 14020 40 80

TEMPERATURE (°C)–60 –40 –20 0 60 100 120 14020 40 80 –60 –40 –20 0 20 40 60 80 140100 120

TEMPERATURE (°C)

NORM

ALIZ

ED F

REQU

ENCY

37035 G09

1.20

1.15

1.10

1.05

1.00

0.95

0.90

0.85

0.80

LOAD CURRENT (A)0

EFFI

CIEN

CY (%

)

100

95

90

85

801 2 3 4

37035 G02

5

VCC VOLTAGE (V)0

3.5

3.0

2.5

2.0

1.5

1.0

0.5

07.5

37035 G04

2.5 5 10 12.5 15

V CC

CURR

ENT

(mA)

37035 G05

37035 G03

V CC

CURR

ENT

(µA)

37035 G07

35

30

25

20

15

10

5

0

REFE

RENC

E VO

LTAG

E (V

)

0.803

0.802

0.801

0.800

0.799

0.798

37035 G08

VOUT = 12Vf = 250kHzPULSE SKIP ENABLED

VIN = 42V

VIN = 24V

VOUT50mV/DIV

AC COUPLED

IOUT2A/DIV

VIN = 50VVOUT = 12V1A TO 5A LOAD STEP

50µs/DIV

VFB = 0V

VCC RISING

COMP = 1.5V

TEMPERATURE (°C)–60 –40 –20 0

V CC

CURR

ENT

(mA)

60 120 14010020 40 80

4

3

2

1

0

VFB = 0V

COMP = 1.5V

INPUT VOLTAGE (V)0

80

EFFI

CIEN

CY (%

)

85

90

95

100

10 20 30 40

37035 G01

50 60

IOUT = 1A

VOUT = 5Vf = 250kHzFORCED CONTINUOUS

IOUT = 5A

VCC VOLTAGE (V)0

0

V CC

CURR

ENT

(µA)

20

40

60

80

4 8 12 16

37035 G06

100

120

2 6 10 14

VCC = 5V

TA = 25°C (unless otherwise noted).

-

LTC3703-5

537035fa

PEAK

SOU

RCE

CURR

ENT

(A)

1.2

1.1

1.0

0.9

0.8

37035 G10

TEMPERATURE (°C)

R DS(

ON) (

Ω)

37035 G11

DRVCC/BOOST VOLTAGE (V)0 2.5 7.5 10 12.5

PEAK

SOU

RCE

CURR

ENT

(A)

3.0

2.5

2.0

1.5

1.0

0.5

05

37035 G12

15–60 –40 –20 0 20 40 60 80 100 120 140 –60 –40 –20 0 20 40 60 80 100 120 140TEMPERATURE (°C)

VCC = 5V

|SW| VOLTAGE (V)0

25

20

15

10

5

0

–5

–100.3 0.5

37035 G17

0.1 0.2 0.4 0.6 0.7

RUN/

SS S

INK

CURR

ENT

(µA)

RUN VOLTAGE (V)0.5

MAX

DUT

Y CY

CLE

(%)

100

90

80

70

60

50

40

30

20

10

0

–102.5

37035 G18

1.0 1.5 2.0 3.0

IMAX = 0.3V

TEMPERATURE (°C)

RUN/

SS C

URRE

NT (µ

A)

15735 G15

6

5

4

3

2

1

0–60 –20 20 40–40 0 60 80 100 120 140

2

1.8

1.6

1.4

1.2

1

0.8

0.6

0.4

DRVCC/BOOST VOLTAGE (V)2.5

1.1

1.2

1.3

12.5

37035 G13

1.0

0.9

5 7.5 10 15

0.8

0.7

0.6

R DS(

ON) (

Ω)

GATE CAPACITANCE (nF)0

RISE

/FAL

L TI

ME

(ns)

100

150

20

37035 G14

50

05 10 15

200

RISE TIME

FALL TIME

VCC = 5V

VCC VOLTAGE (V)0

0

RUN/

SS P

ULL-

UP C

URRE

NT (µ

A)

1

2

3

4

5

2.5 5 7.5 10

37035 G16

12.5 15

VCC = 5V VCC = 5V

TYPICAL PERFOR A CE CHARACTERISTICS

UW

Driver Peak Source Currentvs Temperature

Driver Pull-Down RDS(ON)vs Temperature

Driver Peak Source Currentvs Supply Voltage

Rise/Fall Timevs Gate Capacitance

RUN/SS Pull-Up Currentvs Temperature

RUN/SS Pull-Up Currentvs VCC Voltage

RUN/SS Sink Currentvs SW Voltage Max % DC vs RUN/SS Voltage

Driver Pull-Down RDS(ON)vs Supply Voltage

-

LTC3703-5

637035fa

TYPICAL PERFOR A CE CHARACTERISTICS

UW

IMAX Current vs Temperature % Duty Cycle vs COMP VoltageMax % DC vs Frequency andTemperature

Shutdown Threshold vsTemperature tON(MIN) vs Temperature

I MAX

SOU

RCE

CURR

ENT

(µA)

13

12

11

37035 G19

FREQUENCY (kHz)

MAX

DUT

Y CY

CLE

(%)

37035 G21

100

95

90

85

80

75

700 200 400 500100 300 600 700

TEMPERATURE (°C)

SHUT

DOW

N TH

RESH

OLD

(V)

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

37035 G22 37035 G23

t ON(

MIN

) (ns

)200

180

160

140

120

100

80

60

40

–60 –40 –20 0 20 40 60 80 100 120 140TEMPERATURE (°C)

–60 –40 –20 0 20 40 60 80 100 120 140 –60 –40 –20 0 20 40 60 80 100 120 140TEMPERATURE (°C)

25°C

–45°C

90°C

125°C

COMP (V)0.5

DUTY

CYC

LE (%

)

100

80

60

40

20

00.75 1.00 1.25 1.50

37035 G20

1.75 2.00

VIN = 10V

VIN = 50V

VIN = 25V

-

LTC3703-5

737035fa

MODE/SYNC (Pin 1/Pin 6): Pulse Skip Mode Enable/SyncPin. This multifunction pin provides Pulse Skip Mode en-able/disable control and an external clock input for synchro-nization of the internal oscillator. Pulling this pin below 0.8Vor to an external logic-level synchronization signal disablesPulse Skip Mode operation and forces continuous opera-tion. Pulling the pin above 0.8V enables Pulse Skip Modeoperation. This pin can also be connected to a feedbackresistor divider from a secondary winding on the inductorto regulate a second output voltage.

fSET (Pin 2/Pin 7): Frequency Set. A resistor connected tothis pin sets the free running frequency of the internal os-cillator. See applications section for resistor value selec-tion details.

COMP (Pin 3/Pin 8): Loop Compensation. This pin is con-nected directly to the output of the internal error amplifier.An RC network is used at the COMP pin to compensate thefeedback loop for optimal transient response.

FB (Pin 4/Pin 9): Feedback Input. Connect FB through aresistor divider network to VOUT to set the output voltage.Also connect the loop compensation network from COMPto FB.

IMAX (Pin 5/Pin 10): Current Limit Set. The IMAX pin setsthe current limit comparator threshold. If the voltage dropacross the bottom MOSFET exceeds the magnitude of thevoltage at IMAX, the controller goes into current limit. TheIMAX pin has an internal 12µA current source, allowing thecurrent threshold to be set with a single external resistorto ground. See the Current Limit Programming section formore information on choosing RIMAX.

INV (Pin 6/Pin 11): Top/Bottom Gate Invert. Pulling this pinabove 2V sets the controller to operate in step-up (boost)mode with the TG output driving the synchronous MOSFETand the BG output driving the main switch. Below 1V, thecontroller will operate in step-down (buck) mode.

RUN/SS (Pin 7/Pin 13): Run/Soft-Start. Pulling RUN/SS be-low 0.9V will shut down the LTC3703-5, turn off both of theexternal MOSFET switches and reduce the quiescent sup-ply current to 25µA. A capacitor from RUN/SS to groundwill control the turn-on time and rate of rise of the outputvoltage at power-up. An internal 4µA current source pull-up at the RUN/SS pin sets the turn-on time at approximately750ms/µF.

GND (Pin 8/Pin 14): Ground Pin.

BGRTN (Pin 9/Pin 15): Bottom Gate Return. This pin con-nects to the source of the pull-down MOSFET in the BGdriver and is normally connected to ground. Connecting anegative supply to this pin allows the synchronousMOSFET’s gate to be pulled below ground to help preventfalse turn-on during high dV/dt transitions on the SW node.See the Applications Information section for more details.

BG (Pin 10/Pin 19): Bottom Gate Drive. The BG pin drivesthe gate of the bottom N-channel synchronous switchMOSFET. This pin swings from BGRTN to DRVCC.

DRVCC (Pin 11/Pin 20): Driver Power Supply Pin. DRVCCprovides power to the BG output driver. This pin should beconnected to a voltage high enough to fully turn on theexternal MOSFETs, normally 4.5V to 15V for logic levelthreshold MOSFETs. DRVCC should be bypassed to BGRTNwith a 10µF, low ESR (X5R or better) ceramic capacitor.

VCC (Pin 12/Pin 21) : Main Supply Pin. All internal circuitsexcept the output drivers are powered from this pin. VCCshould be connected to a low noise power supply voltagebetween 4.5V and 15V and should be bypassed to GND(Pin 8) with at least a 0.1µF capacitor in close proximity tothe LTC3703-5.

SW (Pin 13/Pin 26): Switch Node Connection to Inductorand Bootstrap Capacitor. Voltage swing at this pin is froma Schottky diode (external) voltage drop below ground toVIN.

TG (Pin 14/Pin 27): Top Gate Drive. The TG pin drives thegate of the top N-channel synchronous switch MOSFET. TheTG driver draws power from the BOOST pin and returns tothe SW pin, providing true floating drive to the top MOSFET.

BOOST (Pin 15/Pin 28): Top Gate Driver Supply. The BOOSTpin supplies power to the floating TG driver. The BOOST pinshould be bypassed to SW with a low ESR (X5R or better)0.1µF ceramic capacitor. An additional fast recovery Schot-tky diode from DRVCC to BOOST will create a complete float-ing charge-pumped supply at BOOST.

VIN (Pin 16/Pin 1): Input Voltage Sense Pin. This pin is con-nected to the high voltage input of the regulator and is usedby the internal feedforward compensation circuitry to im-prove line regulation. This is not a supply pin.

UUU

PI FU CTIO S (GN16/G28)

-

LTC3703-5

837035fa

FU CTIO AL DIAGRA

UU W

5

1

UVSD OTSD

CHIPSD1V

3.2V

4µA

RUN/SS

BANDGAP

SYNCDETECT

OVERTEMP VCC UVLO

OSC

% DCLIMIT

DRIVELOGIC

+

–

+

–

+

–

+

–

EXT SYNC

FORCED CONTINUOUS

÷++–

+ – + –

+

–0.8V

MODE/SYNC

3COMP

4FB

16

15

14

13

11

10

9

6

12

VIN

VCC(

-

LTC3703-5

937035fa

OPERATIOU

(Refer to Functional Diagram)

When the load current increases, it causes a drop in thefeedback voltage relative to the reference. The COMP volt-age then rises, increasing the duty ratio until the outputfeedback voltage again matches the reference voltage. Innormal operation, the top MOSFET is turned on when theRS latch is set by the on-chip oscillator and is turned offwhen the PWM comparator trips and resets the latch. ThePWM comparator trips at the proper duty ratio by compar-ing the error amplifier output (after being “compensated”by the line feedforward multiplier) to a sawtooth waveformgenerated by the oscillator. When the top MOSFET is turnedoff, the bottom MOSFET is turned on until the next cyclebegins or, if Pulse Skip Mode operation is enabled, untilthe inductor current reverses as determined by the reversecurrent comparator. MAX and MIN comparators ensurethat the output never exceed ±5% of nominal value bymonitoring VFB and forcing the output back into regulationquickly by either keeping the top MOSFET off or forcingmaximum duty cycle. The operation of its other features—fast transient response, outstanding line regulation, stronggate drivers, short-circuit protection, and shutdown/soft-start—are described below.

Fast Transient Response

The LTC3703-5 uses a fast 25MHz op amp as an error am-plifier. This allows the compensation network to be opti-mized for better load transient response. The highbandwidth of the amplifier, along with high switching fre-quencies and low value inductors, allow very high loopcrossover frequencies. The 800mV internal reference allowsregulated output voltages as low as 800mV without exter-nal level shifting amplifiers.

Line Feedforward Compensation

The LTC3703-5 achieves outstanding line transient re-sponse using a patented feedforward correction scheme.With this circuit the duty cycle is adjusted instantaneouslyto changes in input voltage, thereby avoiding unaccept-able overshoot or undershoot. It has the added advantageof making the DC loop gain independent of input voltage.Figure 1 shows how large transient steps at the input havelittle effect on the output voltage.

20µs/DIV

VOUT50mV/DIV

AC COUPLED

VOUT = 12VILOAD = 1A25V TO 60V VIN STEP

VIN20V/DIV

IL2A/DIV

37035 F01

Figure 1. Line Transient Performance

Strong Gate Drivers

The LTC3703-5 contains very low impedance driverscapable of supplying amps of current to slew large MOSFETgates quickly. This minimizes transition losses and allowsparalleling MOSFETs for higher current applications. A60V floating high side driver drives the top side MOSFETand a low side driver drives the bottom side MOSFET (seeFigure 2). They can be powered from either a separate DCsupply or a voltage derived from the input or outputvoltage (see MOSFET Driver Supplies section). The bot-tom side driver is supplied directly from the DRVCC pin.The top MOSFET drivers are biased from floating boot-strap capacitor CB, which normally is recharged duringeach off cycle through an external diode from DRVCC whenthe top MOSFET turns off. In Pulse Skip Mode operation,where it is possible that the bottom MOSFET will be off foran extended period of time, an internal counter guaranteesthat the bottom MOSFET is turned on at least once every10 cycles for 10% of the period to refresh the bootstrapcapacitor. An undervoltage lockout keeps the LTC3703-5shut down unless this voltage is above 4.1V.

The bottom driver has an additional feature that helpsminimize the possibility of external MOSFET shoot-thru.When the top MOSFET turns on, the switch node dV/dtpulls up the bottom MOSFET’s internal gate through theMiller capacitance, even when the bottom driver is holdingthe gate terminal at ground. If the gate is pulled up highenough, shoot-thru between the top side and bottom side

-

LTC3703-5

1037035fa

OPERATIOU

MOSFETs can occur. To prevent this from occuring, thebottom driver return is brought out as a separate pin(BGRTN) so that a negative supply can be used to reducethe effect of the Miller pull-up. For example, if a –2V supplyis used on BGRTN, the switch node dV/dt could pull thegate up 2V before the VGS of the bottom MOSFET has morethan 0V across it.

cycle control set to 0%. As CSS continues to charge, theduty cycle is gradually increased, allowing the outputvoltage to rise. This soft-start scheme smoothly ramps theoutput voltage to its regulated value, with no overshoot.The RUN/SS voltage will continue ramping until it reachesan internal 4V clamp. Then the MIN feedback comparatoris enabled and the LTC3703-5 is in full operation. When theRUN/SS is low, the supply current is reduced to 25µA.

CURRENTLIMIT

NORMAL OPERATIONSTART-UP

0V

4V

3V

1.4V1V

0V

POWERDOWN MODE

MINIMUMDUTY CYCLE

OUTPUT VOLTAGEIN REGULATION

LTC3703-5ENABLE

MIN COMPARATOR ENABLED

37035 F03

RUN/SS SOFT-STARTSOUTPUT VOLTAGE ANDINDUCTOR CURRENT

SHUTDOWN

VOUT

VRUN/SS

(Refer to Functional Diagram)

BOOST

TG

SW

BG

BGRTN

DRVCC

DRVCC

LTC3703-5

M1

M2

+

+

VIN

CIN

VOUT

COUT

DB

CB

L

37035 F020V TO –5V

Figure 3. Soft-Start Operation in Start Up and Current Limit

Figure 2. Floating TG Driver Supply and Negative BG Return

Constant Frequency

The internal oscillator can be programmed with an exter-nal resistor connected from fSET to ground to run between100kHz and 600kHz, thereby optimizing component size,efficiency, and noise for the specific application. Theinternal oscillator can also be synchronized to an externalclock applied to the MODE/SYNC pin and can lock to afrequency in the 100kHz to 600kHz range. When locked toan external clock, Pulse Skip Mode operation is automati-cally disabled. Constant frequency operation brings with ita number of benefits: Inductor and capacitor values can bechosen for a precise operating frequency and the feedbackloop can be similarly tightly specified. Noise generated bythe circuit will always be at known frequencies.Subharmonic oscillation and slope compensation, com-mon headaches with constant frequency current modeswitchers, are absent in voltage mode designs like theLTC3703-5.

Shutdown/Soft-Start

The main control loop is shut down by pulling RUN/SS pinlow. Releasing RUN/SS allows an internal 4µA currentsource to charge the soft-start capacitor CSS. When CSSreaches 1V, the main control loop is enabled with the duty

Current Limit

The LTC3703-5 includes an onboard current limit circuitthat limits the maximum output current to a user-pro-grammed level. It works by sensing the voltage drop acrossthe bottom MOSFET and comparing that voltage to a user-programmed voltage at the IMAX pin. Since the bottomMOSFET looks like a low value resistor during its on-time,the voltage drop across it is proportional to the currentflowing in it. In a buck converter, the average current in theinductor is equal to the output current. This current alsoflows through the bottom MOSFET during its on-time.Thus by watching the drain-to-source voltage when thebottom MOSFET is on, the LTC3703-5 can monitor theoutput current. The LTC3703-5 senses this voltage andinverts it to allow it to compare the sensed voltage (whichbecomes more negative as peak current increases) with apositive voltage at the IMAX pin. The IMAX pin includes a12µA pull-up, enabling the user to set the voltage at IMAXwith a single resistor (RIMAX) to ground. See the CurrentLimit Programming section for RIMAX selection.

-

LTC3703-5

1137035fa

For maximum protection, the LTC3703-5 current limitconsists of a steady-state limit circuit and an instanta-neous limit circuit. The steady-state limit circuit is a gmamplifier that pulls a current from the RUN/SS pin propor-tional to the difference between the SW and IMAX voltages.This current begins to discharge the capacitor at RUN/SS,reducing the duty cycle and controlling the output voltageuntil the current regulates at the limit. Depending on thesize of the capacitor, it may take many cycles to dischargethe RUN/SS voltage enough to properly regulate theoutput current. This is where the instantaneous limitcircuit comes into play. The instantaneous limit circuit isa cycle-by-cycle comparator which monitors the bottomMOSFET’s drain voltage and keeps the top MOSFET fromturning on whenever the drain voltage is 50mV above theprogrammed max drain voltage. Thus the cycle-by-cyclecomparator will keep the inductor current under controluntil the gm amplifier gains control.

Pulse Skip Mode

The LTC3703-5 can operate in one of two modes select-able with the MODE/SYNC pin—Pulse Skip Mode orforced continuous mode. Pulse Skip Mode is selectedwhen increased efficiency at light loads is desired. In thismode, the bottom MOSFET is turned off when inductorcurrent reverses to minimize the efficiency loss due toreverse current flow. As the load is decreased (see Fig-ure 5), the duty cycle is reduced to maintain regulationuntil its minimum on-time (~200ns) is reached. When theload decreases below this point, the LTC3703-5 begins to Figure 4. Efficiency in Pulse Skip/Forced Continuous Modes

LOAD (mA)10

EFFI

CIEN

CY (%

)

100

90

80

70

60

50

40

30

20

10

0100 1000 10000

37035 F04

FORCED CONTINUOUSPULSE SKIP MODE

VIN = 42V

VIN = 12V

VOUT = 5V

VIN = 12V

VIN = 42V

skip cycles to maintain regulation. The frequency dropsbut this further improves efficiency by minimizing gatecharge losses. In forced continuous mode, the bottomMOSFET is always on when the top MOSFET is off,allowing the inductor current to reverse at low currents.This mode is less efficient due to resistive losses, but hasthe advantage of better transient response at low currents,constant frequency operation, and the ability to maintainregulation when sinking current. See Figure 4 for a com-parison of the effect on efficiency at light loads for eachmode. The MODE/SYNC threshold is 0.8V ±7.5%, allow-ing the MODE/SYNC to act as a feedback pin for regulatinga second winding. If the feedback voltage drops below0.8V, the LTC3703-5 reverts to continuous operation tomaintain regulation in the secondary supply.

Figure 5. Comparison of Inductor Current Waveforms for Pulse Skip Mode and Forced Continuous Operation

PULSE SKIP MODE FORCED CONTINUOUS

DECREASINGLOAD

CURRENT

37035 F05

OPERATIOU

(Refer to Functional Diagram)

-

LTC3703-5

1237035fa

The basic LTC3703-5 application circuit is shown on the firstpage of this data sheet. External component selection is de-termined by the input voltage and load requirements asexplained in the following sections. After the operatingfrequency is selected, RSET and L can be chosen. Theoperating frequency and the inductor are chosen for adesired amount of ripple current and also to optimize ef-ficiency and component size. Next, the power MOSFETs andD1 are selected based on voltage, load and efficiency re-quirements. CIN is selected for its ability to handle the largeRMS currents in the converter and COUT is chosen with lowenough ESR to meet the output voltage ripple and transientspecifications. Finally, the loop compensation componentsare chosen to meet the desired transient specifications.

Operating Frequency

The choice of operating frequency and inductor value is atrade off between efficiency and component size. Lowfrequency operation improves efficiency by reducingMOSFET switching losses and gate charge losses. How-ever, lower frequency operation requires more induc-tance for a given amount of ripple current, resulting in alarger inductor size and higher cost. If the ripple currentis allowed to increase, larger output capacitors may berequired to maintain the same output ripple. For convert-ers with high step-down VIN to VOUT ratios, anotherconsideration is the minimum on-time of the LTC3703-5(see the Minimum On-time Considerations section). Afinal consideration for operating frequency is that in

APPLICATIO S I FOR ATIO

WU UU

noise-sensitive communications systems, it is often de-sirable to keep the switching noise out of a sensitivefrequency band.

The LTC3703-5 uses a constant frequency architecturethat can be programmed over a 100kHz to 600kHz rangewith a single resistor from the fSET pin to ground, as shownin the circuit on the first page of this data sheet. Thenominal voltage on the fSET pin is 1.2V, and the current thatflows from this pin is used to charge and discharge aninternal oscillator capacitor. The value of RSET for a givenoperating frequency can be chosen from Figure 6 or fromthe following equation:

R kf kHzSET

( )( ) –

Ω = 710025

Buck or Boost Mode Operation

The LTC3703-5 has the capability of operating both as astep-down (buck) and step-up (boost) controller. In boostmode, output voltages as high as 60V can be tightlyregulated. With the INV pin grounded, the LTC3703-5operates in buck mode with TG driving the main (top side)switch and BG driving the synchronous (bottom side)switch. If the INV pin is pulled above 2V, the LTC3703-5operates in boost mode with BG driving the main (bottomside) switch and TG driving the synchronous (top side)switch. Internal circuit operation is very similar regardless

of the operating mode with the following exceptions: Inboost mode, Pulse Skip Mode operation is always dis-abled regardless of the level of the MODE/SYNC pin andthe line feedforward compensation is also disabled. Theovercurrent circuitry continues to monitor the load currentby looking at the drain voltage of the main (bottom side)MOSFET. In boost mode, however, the peak MOSFETcurrent does not equal the load current but insteadID = ILOAD/(1 – D). This factor needs to be taken intoaccount when programming the IMAX voltage.

FREQUENCY (kHz)

R SET

(kΩ

)

1000

37035 F06

10

1

100

200 10008006004000

Figure 6. Timing Resistor (RSET) Value

OPERATIOU

(Refer to Functional Diagram)

-

LTC3703-5

1337035fa

The oscillator can also be synchronized to an externalclock applied to the MODE/SYNC pin with a frequency inthe range of 100kHz to 600kHz (refer to the MODE/SYNCPin section for more details). In this synchronized mode,Pulse Skip Mode operation is disabled. The clock highlevel must exceed 2V for at least 25ns. As shown inFigure 7, the top MOSFET turn-on will follow the risingedge of the external clock by a constant delay equal to one-tenth of the cycle period.

ripple current occurs at the highest VIN. To guarantee thatripple current does not exceed a specified maximum, theinductor in buck mode should be chosen according to:

LV

f IV

VOUT

L MAX

OUT

IN MAX≥

∆⎛

⎝⎜⎞

⎠⎟( ) ( )–1

The inductor also has an affect on low current operationwhen Pulse Skip Mode operation is enabled. The fre-quency begins to decrease when the output current dropsbelow the average inductor current at which the LTC3703-5is operating at its tON(MIN) in discontinuous mode (seeFigure 5). Lower inductance increases the peak inductorcurrent that occurs in each minimum on-time pulse andthus increases the output current at which the frequencystarts decreasing.

Power MOSFET Selection

The LTC3703-5 requires at least two external N-channelpower MOSFETs, one for the top (main) switch and one ormore for the bottom (synchronous) switch. The number,type and “on” resistance of all MOSFETs selected take intoaccount the voltage step-down ratio as well as the actualposition (main or synchronous) in which the MOSFET willbe used. A much smaller and much lower input capaci-tance MOSFET should be used for the top MOSFET inapplications that have an output voltage that is less than1/3 of the input voltage. In applications where VIN >> VOUT,the top MOSFETs’ “on” resistance is normally less impor-tant for overall efficiency than its input capacitance atoperating frequencies above 300kHz. MOSFET manufac-turers have designed special purpose devices that providereasonably low “on” resistance with significantly reducedinput capacitance for the main switch application in switch-ing regulators.

Selection criteria for the power MOSFETs include the “on”resistance RDS(ON), input capacitance, breakdown voltageand maximum output current.

The most important parameter in high voltage applica-tions is breakdown voltage BVDSS. Both the top andbottom MOSFETs will see full input voltage plus anyadditional ringing on the switch node across its drain-to-source during its off-time and must be chosen with the

37035 F07

2V TO 10VMODE/SYNC

TG

IL

tMIN = 25ns

0.8T

0.1T

D = 40%

T T = 1/fO

APPLICATIO S I FOR ATIO

WU UU

Figure 7. MODE/SYNC Clock Input and SwitchingWaveforms for Synchronous Operation

Inductor

The inductor in a typical LTC3703-5 circuit is chosen fora specific ripple current and saturation current. Given aninput voltage range and an output voltage, the inductorvalue and operating frequency directly determine theripple current. The inductor ripple current in the buckmode is:

∆ = ⎛⎝⎜

⎞⎠⎟

IVf L

VVL

OUT OUT

IN( )( )–1

Lower ripple current reduces core losses in the inductor,ESR losses in the output capacitors and output voltageripple. Thus highest efficiency operation is obtained at lowfrequency with small ripple current. To achieve this, how-ever, requires a large inductor.

A reasonable starting point is to choose a ripple currentbetween 20% and 40% of IO(MAX). Note that the largest

-

LTC3703-5

1437035fa

appropriate breakdown specification. Since most MOSFETsin the 30V to 60V range have logic level thresholds(VGS(MIN) ≥ 4.5V), the LTC3703-5 is designed to be usedwith a 4.5V to 15V gate drive supply (DRVCC pin).

For maximum efficiency, on-resistance RDS(ON) and inputcapacitance should be minimized. Low RDS(ON) minimizesconduction losses and low input capacitance minimizestransition losses. MOSFET input capacitance is a combi-nation of several components but can be taken from thetypical “gate charge” curve included on most data sheets(Figure 8).

The curve is generated by forcing a constant input currentinto the gate of a common source, current source loadedstage and then plotting the gate voltage versus time. Theinitial slope is the effect of the gate-to-source and the gate-to-drain capacitance. The flat portion of the curve is theresult of the Miller multiplication effect of the drain-to-gatecapacitance as the drain drops the voltage across thecurrent source load. The upper sloping line is due to thedrain-to-gate accumulation capacitance and the gate-to-source capacitance. The Miller charge (the increase incoulombs on the horizontal axis from a to b while the curveis flat) is specified for a given VDS drain voltage, but can beadjusted for different VDS voltages by multiplying by theratio of the application VDS to the curve specified VDSvalues. A way to estimate the CMILLER term is to take thechange in gate charge from points a and b on a manufac-turers data sheet and divide by the stated VDS voltagespecified. CMILLER is the most important selection criteriafor determining the transition loss term in the top MOSFETbut is not directly specified on MOSFET data sheets. CRSSand COS are specified sometimes but definitions of theseparameters are not included.

When the controller is operating in continuous mode theduty cycles for the top and bottom MOSFETs are given by:

APPLICATIO S I FOR ATIO

WU UU

MainSwitchDutyCycleVV

SynchronousSwitchDutyCycleV V

V

OUT

IN

IN OUT

IN

=

= –

The power dissipation for the main and synchronousMOSFETs at maximum output current are given by:

PVV

I R

VI

R C

V V Vf

PV V

VI R

MAINOUT

INMAX DR ON

INMAX

DR MILLER

CC TH IL TH IL

SYNCIN OUT

INMAX DS N

= ( ) + +

+⎡

⎣⎢⎢

⎤

⎦⎥⎥

= +

2

2

20

1

21 1

1

( )

( )( ) •

–( )

–( ) ( )

( )

( ) ( )

( )

δ

δ

where δ is the temperature dependency of RDS(ON), RDR isthe effective top driver resistance (approximately 2Ω atVGS = VMILLER), VIN is the drain potential and the changein drain potential in the particular application. VTH(IL) is thedata sheet specified typical gate threshold voltage speci-fied in the power MOSFET data sheet at the specified draincurrent. CMILLER is the calculated capacitance using thegate charge curve from the MOSFET data sheet and thetechnique described above.

Both MOSFETs have I2R losses while the topside N-channelequation includes an additional term for transition losses,which peak at the highest input voltage. For VIN < 25V, thehigh current efficiency generally improves with largerMOSFETs, while for VIN > 25V, the transition lossesrapidly increase to the point that the use of a higherRDS(ON) device with lower CMILLER actually provides higherefficiency. The synchronous MOSFET losses are greatestat high input voltage when the top switch duty factor is lowor during a short circuit when the synchronous switch ison close to 100% of the period.

The term (1 + δ) is generally given for a MOSFET in theform of a normalized RDS(ON) vs temperature curve, andtypically varies from 0.005/°C to 0.01/°C depending onthe particular MOSFET used.

Figure 8. Gate Charge Characteristic

+–

VDS

VIN

VGS

MILLER EFFECT

QIN

a b

CMILLER = (QB – QA)/VDS

VGS V

+

–37035 F08

-

LTC3703-5

1537035fa

Multiple MOSFETs can be used in parallel to lower RDS(ON)and meet the current and thermal requirements if desired.The LTC3703-5 contains large low impedance driverscapable of driving large gate capacitances without signifi-cantly slowing transition times. In fact, when drivingMOSFETs with very low gate charge, it is sometimeshelpful to slow down the drivers by adding small gateresistors (10Ω or less) to reduce noise and EMI caused bythe fast transitions.

Schottky Diode Selection

The Schottky diode D1 shown in the circuit on the firstpage of this data sheet conducts during the dead timebetween the conduction of the power MOSFETs. Thisprevents the body diode of the bottom MOSFET fromturning on and storing charge during the dead time andrequiring a reverse recovery period that could cost asmuch as 1% to 2% in efficiency. A 1A Schottky diode isgenerally a good size for 3A to 5A regulators. Largerdiodes result in additional losses due to their largerjunction capacitance. The diode can be omitted if theefficiency loss can be tolerated.

Input Capacitor Selection

In continuous mode, the drain current of the top MOSFETis approximately a square wave of duty cycle VOUT/VINwhich must be supplied by the input capacitor. To preventlarge input transients, a low ESR input capacitor sized forthe maximum RMS current is given by:

I IVV

VVCIN RMS O MAX

OUT

IN

IN

OUT( ) ( )

/

–≅ ⎛⎝⎜

⎞⎠⎟

11 2

This formula has a maximum at VIN = 2VOUT, where IRMS= IO(MAX)/2. This simple worst-case condition is commonlyused for design because even significant deviations do notoffer much relief. Note that the ripple current ratings fromcapacitor manufacturers are often based on only 2000 hoursof life. This makes it advisable to further derate the capaci-tor or to choose a capacitor rated at a higher temperaturethan required. Several capacitors may also be placed inparallel to meet size or height requirements in the design.

Because tantalum and OS-CON capacitors are not avail-able in voltages above 30V, ceramics or aluminum

electrolytics must be used for regulators with input sup-plies above 30V. Ceramic capacitors have the advantage ofvery low ESR and can handle high RMS current, butceramics with high voltage ratings (>50V) are not availablewith more than a few microfarads of capacitance. Further-more, ceramics have high voltage coefficients which meansthat the capacitance values decrease even more when usedat the rated voltage. X5R and X7R type ceramics are rec-ommended for their lower voltage and temperature coef-ficients. Another consideration when using ceramics istheir high Q which, if not properly damped, may result inexcessive voltage stress on the power MOSFETs. Alumi-num electrolytics have much higher bulk capacitance, butthey have higher ESR and lower RMS current ratings.

A good approach is to use a combination of aluminumelectrolytics for bulk capacitance and ceramics for lowESR and RMS current. If the RMS current cannot behandled by the aluminum capacitors alone, when usedtogether, the percentage of RMS current that will besupplied by the aluminum capacitor is reduced toapproximately:

%( )

• %,IfCR

RMS ALUMESR

≈+

1

1 8100

2

where RESR is the ESR of the aluminum capacitor and C isthe overall capacitance of the ceramic capacitors. Using analuminum electrolytic with a ceramic also helps damp thehigh Q of the ceramic, minimizing ringing.

Output Capacitor Selection

The selection of COUT is primarily determined by the ESRrequired to minimize voltage ripple. The output ripple(∆VOUT) is approximately equal to:

∆ ≤ ∆ +⎛⎝⎜

⎞⎠⎟

V I ESRfCOUT L OUT

18

Since ∆IL increases with input voltage, the output ripple ishighest at maximum input voltage. ESR also has a signifi-cant effect on the load transient response. Fast loadtransitions at the output will appear as voltage across theESR of COUT until the feedback loop in the LTC3703-5 canchange the inductor current to match the new load current

APPLICATIO S I FOR ATIO

WU UU

-

LTC3703-5

1637035fa

value. Typically, once the ESR requirement is satisfied thecapacitance is adequate for filtering and has the requiredRMS current rating.

Manufacturers such as Nichicon, Nippon Chemi-Con andSanyo should be considered for high performancethroughhole capacitors. The OS-CON (organic semicon-ductor dielectric) capacitor available from Sanyo has thelowest product of ESR and size of any aluminum electro-lytic at a somewhat higher price. An additional ceramiccapacitor in parallel with OS-CON capacitors is recom-mended to reduce the effect of their lead inductance.

In surface mount applications, multiple capacitors placedin parallel may be required to meet the ESR, RMS currenthandling and load step requirements. Dry tantalum, spe-cial polymer and aluminum electrolytic capacitors areavailable in surface mount packages. Special polymercapacitors offer very low ESR but have lower capacitancedensity than other types. Tantalum capacitors have thehighest capacitance density but it is important to only usetypes that have been surge tested for use in switchingpower supplies. Several excellent surge-tested choicesare the AVX TPS and TPSV or the KEMET T510 series.Aluminum electrolytic capacitors have significantly higherESR, but can be used in cost-driven applications providingthat consideration is given to ripple current ratings andlong term reliability. Other capacitor types includePanasonic SP and Sanyo POSCAPs.

Output Voltage

The LTC3703-5 output voltage is set by a resistor divideraccording to the following formula:

V VRROUT

= +⎛⎝⎜

⎞⎠⎟

0 8 112

.

The external resistor divider is connected to the output asshown in the Functional Diagram, allowing remote voltagesensing. The resultant feedback signal is compared withthe internal precision 800mV voltage reference by theerror amplifier. The internal reference has a guaranteedtolerance of ±1%. Tolerance of the feedback resistors willadd additional error to the output voltage. 0.1% to 1%resistors are recommended.

MOSFET Driver Supplies (DRVCC and BOOST)

The LTC3703-5 drivers are supplied from the DRVCC andBOOST pins (see Figure 2), which have an absolutemaximum voltage of 15V. If the main supply voltage, VIN,is higher than 15V a separate supply with a voltagebetween 5V and 15V must be used to power the drivers. Ifa separate supply is not available, one can easily begenerated from the main supply using one of the circuitsshown in Figure 9. If the output voltage is between 5V and15V, the output can be used to directly power the driversas shown in Figure 9a. If the output is below 5V, Figure 9bshows an easy way to boost the supply voltage to asufficient level. This boost circuit uses the LT1613 in aThinSOTTM package and a chip inductor for minimal extraarea (

-

LTC3703-5

1737035fa

Figure 9a. VCC Generated from 5V < VOUT < 15V

APPLICATIO S I FOR ATIO

WU UU

VCC

DRVCC

VIN

TG

SW

BG

BGRTN

LTC3703-5

VOUT5V TO 15V

+COUT

37035 F09a

+CIN

+1µF

VIN

L1

D15.1V

R1

Q1

VCC

DRVCC

VIN

TG

SW

BG

BGRTN

LTC3703-5

VOUT

-

LTC3703-5

1837035fa

node dV/dt can be many volts/ns, which will pull up on thegate of the bottom MOSFET through its Miller capacitance.If this Miller current, times the internal gate resistance ofthe MOSFET plus the driver resistance, exceeds the thresh-old of the FET, shoot-through will occur. By using a nega-tive supply on BGRTN, the BG can be pulled below groundwhen turning the bottom MOSFET off. This provides a fewextra volts of margin before the gate reaches the turn-onthreshold of the MOSFET. Be aware that the maximumvoltage difference between DRVCC and BGRTN is 15V. If,for example, VBGRTN = –2V, the maximum voltage onDRVCC pin is now 13V instead of 15V.

Current Limit Programming

Programming current limit on the LTC3703-5 is straightforward. The IMAX pin sets the current limit by setting themaximum allowable voltage drop across the bottomMOSFET. The voltage across the MOSFET is set by its on-resistance and the current flowing in the inductor, whichis the same as the output current. The LTC3703-5 currentlimit circuit inverts the negative voltage across the MOSFETbefore comparing it to the voltage at IMAX, allowing thecurrent limit to be set with a positive voltage.

To set the current limit, calculate the expected voltagedrop across the bottom MOSFET at the maximum desiredcurrent and maximum junction temperature:

VPROG = (ILIMIT)(RDS(ON))(1 + δ)

where δ is explained in the MOSFET Selection section.VPROG is then programmed at the IMAX pin using theinternal 12µA pull-up and an external resistor:

RIMAX = VPROG/12µA

The current limit value should be checked to ensure thatILIMIT(MIN) > IOUT(MAX). The minimum value of current limitgenerally occurs with the largest VIN at the highest ambi-ent temperature, conditions that cause the largest powerloss in the converter. Note that it is important to check forself-consistency between the assumed MOSFET junctiontemperature and the resulting value of ILIMIT which heatsthe MOSFET switches.

Caution should be used when setting the current limitbased upon the RDS(ON) of the MOSFETs. The maximumcurrent limit is determined by the minimum MOSFET on-

resistance. Data sheets typically specify nominal andmaximum values for RDS(ON), but not a minimum. Areasonable assumption is that the minimum RDS(ON) liesthe same amount below the typical value as the maximumlies above it. Consult the MOSFET manufacturer for furtherguidelines.

For best results, use a VPROG voltage between 100mV and500mV. Values outside of this range may give less accu-rate current limit. The current limit can also be disabled byfloating the IMAX pin.

FEEDBACK LOOP/COMPENSATION

Feedback Loop Types

In a typical LTC3703-5 circuit, the feedback loop consistsof the modulator, the external inductor, the output capaci-tor and the feedback amplifier with its compensationnetwork. All of these components affect loop behavior andmust be accounted for in the loop compensation. Themodulator consists of the internal PWM generator, theoutput MOSFET drivers and the external MOSFETs them-selves. From a feedback loop point of view, it looks like alinear voltage transfer function from COMP to SW and hasa gain roughly equal to the input voltage. It has fairlybenign AC behavior at typical loop compensation frequen-cies with significant phase shift appearing at half theswitching frequency.

The external inductor/output capacitor combination makesa more significant contribution to loop behavior. Thesecomponents cause a second order LC roll off at the output,with the attendant 180° phase shift. This rolloff is what filtersthe PWM waveform, resulting in the desired DC outputvoltage, but the phase shift complicates the loop compen-sation if the gain is still higher than unity at the pole fre-quency. Eventually (usually well above the LC polefrequency), the reactance of the output capacitor will ap-proach its ESR and the rolloff due to the capacitor will stop,leaving 6dB/octave and 90° of phase shift (Figure 10).

So far, the AC response of the loop is pretty well out of theuser’s control. The modulator is a fundamental piece of theLTC3703-5 design and the external L and C are usuallychosen based on the regulation and load current require-ments without considering the AC loop response. The

APPLICATIO S I FOR ATIO

WU UU

-

LTC3703-5

1937035fa

for an extended frequency range. LTC3703-5 circuitsusing conventional switching grade electrolytic outputcapacitors can often get acceptable phase margin withType 2 compensation.

“Type 3” loops (Figure 13) use two poles and two zeros toobtain a 180° phase boost in the middle of the frequencyband. A properly designed Type 3 circuit can maintainacceptable loop stability even when low output capacitorESR causes the LC section to approach 180° phase shiftwell above the initial LC roll-off. As with a Type 2 circuit,the loop should cross through 0dB in the middle of thephase bump to maximize phase margin. Many LTC3703-5circuits using low ESR tantalum or OS-CON output capaci-tors need Type 3 compensation to obtain acceptable phasemargin with a high bandwidth feedback loop.

feedback amplifier, on the other hand, gives us a handlewith which to adjust the AC response. The goal is to have180° phase shift at DC (so the loop regulates) and some-thing less than 360° phase shift at the point that the loopgain falls to 0dB. The simplest strategy is to set up thefeedback amplifier as an inverting integrator, with the 0dBfrequency lower than the LC pole (Figure 11). This “Type1” configuration is stable but transient response is lessthan exceptional if the LC pole is at a low frequency.

APPLICATIO S I FOR ATIO

WU UU

GAIN

(dB)

37035 F10

AV

0

PHASE

–6dB/OCT

–12dB/OCT

GAIN

PHASE (DEG)

FREQ

–90

–180

–270

–360

Figure 10. Transfer Function of Buck Modulator

GAIN

(dB)

37035 F11

0

PHASE

–6dB/OCT

GAIN

PHASE (DEG)

FREQ

–90

–180

–270

–360

RB

R1FB

C1IN

OUT

+

–

VREF

Figure 11. Type 1 Schematic and Transfer Function

GAIN

(dB)

37035 F12

0

PHASE

–6dB/OCT

–6dB/OCTGAIN

PHASE (DEG)

FREQ

–90

–180

–270

–360

RB

VREF

R1

R2

FB

C2

IN

OUT

+

–

C1

Figure 12. Type 2 Schematic and Transfer Function

GAIN

(dB)

37035 F13

0

PHASE

–6dB/OCT

+6dB/OCT –6dB/OCTGAIN

PHASE (DEG)

FREQ

–90

–180

–270

–360

RB

VREF

R1

R2

FB

C2IN

OUT

+

–

C1C3

R3

Figure 13. Type 3 Schematic and Transfer Function

Figure 12 shows an improved “Type 2” circuit that uses anadditional pole-zero pair to temporarily remove 90° ofphase shift. This allows the loop to remain stable with 90°more phase shift in the LC section, provided the loopreaches 0dB gain near the center of the phase “bump.”Type 2 loops work well in systems where the ESR zero inthe LC roll-off happens close to the LC pole, limiting thetotal phase shift due to the LC. The additional phasecompensation in the feedback amplifier allows the 0dBpoint to be at or above the LC pole frequency, improvingloop bandwidth substantially over a simple Type 1 loop. Ithas limited ability to compensate for LC combinationswhere low capacitor ESR keeps the phase shift near 180°

Feedback Component Selection

Selecting the R and C values for a typical Type 2 or Type 3loop is a nontrivial task. The applications shown in thisdata sheet show typical values, optimized for the powercomponents shown. They should give acceptable perfor-mance with similar power components, but can be way off

-

LTC3703-5

2037035fa

if even one major power component is changed signifi-cantly. Applications that require optimized transient re-sponse will require recalculation of the compensationvalues specifically for the circuit in question. The underly-ing mathematics are complex, but the component valuescan be calculated in a straightforward manner if we knowthe gain and phase of the modulator at the crossoverfrequency.

Modulator gain and phase can be measured directly froma breadboard or can be simulated if the appropriateparasitic values are known. Measurement will give moreaccurate results, but simulation can often get close enoughto give a working system. To measure the modulator gainand phase directly, wire up a breadboard with an LTC3703-5and the actual MOSFETs, inductor and input and outputcapacitors that the final design will use. This breadboardshould use appropriate construction techniques for highspeed analog circuitry: bypass capacitors located close tothe LTC3703-5, no long wires connecting components,appropriately sized ground returns, etc. Wire the feedbackamplifier as a simple Type 1 loop, with a 10k resistor fromVOUT to FB and a 0.1µF feedback capacitor from COMP toFB. Choose the bias resistor (RB) as required to set thedesired output voltage. Disconnect RB from ground andconnect it to a signal generator or to the source output ofa network analyzer (Figure 14) to inject a test signal intothe loop. Measure the gain and phase from the COMP pinto the output node at the positive terminal of the outputcapacitor. Make sure the analyzer’s input is AC coupled sothat the DC voltages present at both the COMP and VOUT

APPLICATIO S I FOR ATIO

WU UU

nodes don’t corrupt the measurements or damage theanalyzer.

If breadboard measurement is not practical, a SPICEsimulation can be used to generate approximate gain/phase curves. Plug the expected capacitor, inductor andMOSFET values into the following SPICE deck and gener-ate an AC plot of V(VOUT )/V(COMP) in dB and phase ofVOUT in degrees. Refer to your SPICE manual for details ofhow to generate this plot.

*3703-5 modulator gain/phase*2003 Linear Technology*this file written to run with PSpice 8.0*may require modifications for otherSPICE simulators

*MOSFETsrfet mod sw 0.02 ;MOSFET rdson

*inductorlext sw out1 10u ;inductor valuerl out1 out 0.015 ;inductor series R

*output capcout out out2 540u ;capacitor valueresr out2 0 0.01 ;capacitor ESR

*3703-5 internalsemod mod 0 value = {43*v(comp)}

;3703-5multipliervstim comp 0 0 ac 1 ;ac stimulus.ac dec 100 1k 1meg.probe.end

With the gain/phase plot in hand, a loop crossover fre-quency can be chosen. Usually the curves look somethinglike Figure 10. Choose the crossover frequency in therising or flat parts of the phase curve, beyond the externalLC poles. Frequencies between 10kHz and 50kHz usuallywork well. Note the gain (GAIN, in dB) and phase (PHASE,in degrees) at this point. The desired feedback amplifiergain will be –GAIN to make the loop gain at 0dB at thisfrequency. Now calculate the needed phase boost, assum-ing 60° as a target phase margin:

BOOST = – (PHASE + 30°)

If the required BOOST is less than 60°, a Type 2 loop canbe used successfully, saving two external components.

VIN

TG

SW

BG

INV

MODE/SYNC

COMP

FB

RUN/SS

LTC3703-5

VCC

CIN

5V VIN

M1VOUTTO ANALYZER

VCOMPTO

ANALYZER

ACSOURCE

FROMANALYZER

LEXT

M2

10µF

DRVCC

fSET

0.1µF

RB

BOOST

GND BGRTN

+ +

10k

NCCOUT

37035 F14

+

Figure 14. Modulator Gain/Phase Measurement Set-Up

-

LTC3703-5

2137035fa

BOOST values greater than 60° usually require Type 3loops for satisfactory performance.

Finally, choose a convenient resistor value for R1 (10k isusually a good value). Now calculate the remaining values:

(K is a constant used in the calculations)

f = chosen crossover frequency

G = 10(GAIN/20) (this converts GAIN in dB to G inabsolute gain)

TYPE 2 Loop:

TYPE 3 Loop:

APPLICATIO S I FOR ATIO

WU UU

Boost Converter Design

The following sections discuss the use of the LTC3703-5as a step-up (boost) converter. In boost mode, theLTC3703-5 can step-up output voltages as high as 60V.These sections discuss only the design steps specific to aboost converter. For the design steps common to both abuck and a boost, see the applicable section in the buckmode section. An example of a boost converter circuit isshown in the Typical Applications section. To operate theLTC3703-5 in boost mode, the INV pin should be tied tothe VCC voltage (or a voltage above 2V). Note that in boostmode, pulse-skip operation and the line feedforward com-pensation are disabled.For a boost converter, the duty cycle of the main switch is:

DV V

VOUT IN

OUT= –

For high VOUT to VIN ratios, the maximum VOUT is limitedby the LTC3703-5’s maximum duty cycle which is typically93%. The maximum output voltage is therefore:

VV

DVOUT MAX

IN MIN

MAXIN MIN( )

( )( )–

= ≅1

14

Boost Converter: Inductor SelectionIn a boost converter, the average inductor current equalsthe average input current. Thus, the maximum averageinductor current can be calculated from:

II

DI

VVL MAX

O MAX

MAXO MAX

O

IN MIN( )

( )( )

( )•=

−=

1

As with a buck converter, choose the ripple current to be20% to 40% of IL(MAX). The ripple current amplitude thendetermines the inductor value as follows:

L

V

I fDIN MIN

LMAX= ∆

( )

••

The minimum required saturation current for the inductoris:

IL(SAT) > IL(MAX) + ∆IL/2

KBOOST

Cf G K R

C C K

RKf C

RV R

V VB

REF

OUT REF

= + °⎛

⎝⎜⎞

⎠⎟

=

= −( )=

=−

tan

• • • •

• •( )

245

21

2 11 2 1

22 1

1

2π

π

KBOOST

Cf G R

C C K

RKf C

RR

K

Cf K R

RV R

V VB

REF

OUT REF

= + °⎛

⎝⎜⎞

⎠⎟

=

= −( )=

=−

=

=−

tan

• • •

• •

•( )

24

45

21

2 11 2 1

22 1

311

31

2 31

π

π

π

-

LTC3703-5

2237035fa

Boost Converter: Power MOSFET SelectionFor information about choosing power MOSFETs for aboost converter, see the Power MOSFET Selection sec-tion for the buck converter, since MOSFET selection issimilar. However, note that the power dissipation equa-tions for the MOSFETs at maximum output current in aboost converter are:

P DID

R

VID

R C

V V Vf

PD

I R

MAIN MAXMAX

MAXDS ON

OUTMAX

MAXDR MILLER

CC TH IL TH IL

SYNCMAX

MAX DS ON

= ⎛⎝⎜

⎞⎠⎟

+( ) +

⎛⎝⎜

⎞⎠⎟

( )( )

+⎡

⎣⎢⎢

⎤

⎦⎥⎥

( )

= ⎛⎝⎜

⎞⎠⎟

( ) +( )

11

12 1

1 1

11

1

2

2

2

–

–•

–

––

( )

( ) ( )

( )

δ

δ

Boost Converter: Output Capacitor Selection

In boost mode, the output capacitor requirements aremore demanding due to the fact that the current waveformis pulsed instead of continuous as in a buck converter. Thechoice of component(s) is driven by the acceptable ripplevoltage which is affected by the ESR, ESL and bulkcapacitance as shown in Figure 15. The total output ripplevoltage is:

∆ = +

⎛

⎝⎜⎞

⎠⎟V I

f CESRD

OUT O MAXOUT MAX

( )• –

11

where the first term is due to the bulk capacitance andsecond term due to the ESR.

The choice of output capacitor is driven also by the RMSripple current requirement. The RMS ripple current is:

I I

V V

VRMS COUT O MAX

O IN MIN

IN MIN( ) ( )

( )

( )•

–≈

At lower output voltages (less than 30V), it may bepossible to satisfy both the output ripple voltage and RMSripple current requirements with one or more capacitors of

APPLICATIO S I FOR ATIO

WU UU

Figure 15. Output Voltage RippleWaveform for a Boost Converter

RINGING DUE TOTOTAL INDUCTANCE(BOARD + CAP)∆VESR

∆VCOUT

VOUT(AC)

a single capacitor type. However, at output voltages above30V where capacitors with both low ESR and high bulkcapacitance are hard to find, the best approach is to use acombination of aluminum and ceramic capacitors (seediscussion in Input Capacitor section for the buck con-verter). With this combination, the ripple voltage can beimproved significantly. The low ESR ceremic capacitorwill minimize the ESR step, while the electrolytic willsupply the required bulk capacitance.

Boost Converter: Input Capacitor Selection

The input capacitor of a boost converter is less critical thanthe output capacitor, due to the fact that the inductor is inseries with the input and the input current waveform iscontinuous. The input voltage source impedance deter-mines the size of the input capacitor, which is typically inthe range of 10µF to 100µF. A low ESR capacitor isrecommended though not as critical as for the outputcapacitor.

The RMS input capacitor ripple current for a boost con-verter is:

I

V

L fDRMS CIN

IN MINMAX( )

( ). ••

•= 0 3

Please note that the input capacitor can see a very highsurge current when a battery is suddenly connected to theinput of the converter and solid tantalum capacitors canfail catastrophically under these conditions. Be sure tospecify surge-tested capacitors!

Boost Converter: Current Limit Programming

The LTC3703-5 provides current limiting in boost mode bymonitoring the VDS of the main switch during its on-timeand comparing it to the voltage at IMAX. To set the currentlimit, calculate the expected voltage drop across theMOSFET at the maximum desired inductor current and

-

LTC3703-5

2337035fa

maximum junction temperature. The maximum inductorcurrent is a function of both duty cycle and maximum loadcurrent, so the limit must be set for the maximum expectedduty cycle (minimum VIN) in order to ensure that thecurrent limit does not kick in at loads < IO(MAX):

VI

DR

VV

I R

PROGO MAX

MAXDS ON

OUT

IN MINO MAX DS ON

= +

=⎛

⎝⎜⎞

⎠⎟+

( )( )

( )( ) ( )

–( )

• ( )

11

1

δ

δ

Once VPROG is determined, RIMAX is chosen as follows:

RIMAX = VPROG/12µA

Note that in a boost mode architecture, it is only possibleto provide protection for “soft” shorts where VOUT > VIN.For hard shorts, the inductor current is limited only by theinput supply capability. Refer to Current Limit Program-ming for buck mode for further considerations for currentlimit programming.

Boost Converter: Feedback Loop/Compensation

Compensating a voltage mode boost converter is unfortu-nately more difficult than for a buck converter. This is dueto an additional right-half plane (RHP) zero that is presentin the boost converter but not in a buck. The additional phaselag resulting from the RHP zero is difficult if not impossibleto compensate even with a Type 3 loop, so the best approachis usually to roll off the loop gain at a lower frequency thanwhat could be achievable in buck converter.

A typical gain/phase plot of a voltage-mode boost con-verter is shown in Figure 16. The modulator gain andphase can be measured as described for a buck converteror can be estimated as follows:

GAIN (COMP-to-VOUT DC gain) = 20Log(VOUT2/VIN)

Dominant Pole: fP =

VV LC

IN

OUT•

1

2πSince significant phase shift begins at frequencies abovethe dominant LC pole, choose a crossover frequency nogreater than about half this pole frequency. The gain of thecompensation network should equal –GAIN at this fre-

quency so that the overall loop gain is 0dB here. Thecompensation component to achieve this, using a Type 1amplifier (see Figure 11), is:

G = 10–GAIN/20

C1 = 1/(2π • f • G • R1)

Run/Soft-Start Function

The RUN/SS pin is a multipurpose pin that provide a soft-start function and a means to shut down the LTC3703-5.Soft-start reduces the input supply’s surge current bygradually increasing the duty cycle and can also be usedfor power supply sequencing.

Pulling RUN/SS below 1V puts the LTC3703-5 into a lowquiescent current shutdown (IQ ≅ 25µA). This pin can bedriven directly from logic as shown in Figure 17. Releasing

APPLICATIO S I FOR ATIO

WU UU

Figure 16. Transfer Function of Boost Modulator

GAIN(dB)

PHASE(DEG)

37035 F16

AV

0 0

–90

–180

PHASE

GAIN

–12dB/OCT

Figure 17. LTC3703-5 Startup Operation

2ms/DIV

VOUT5V/DIV

VIN = 50VILOAD = 2ACSS = 0.01µF

RUN/SS2V/DIV

IL2A/DIV

37035 F17

-

LTC3703-5

2437035fa

the main output voltage and the turns ratio of the extrawinding to the primary winding as follows:

VSEC ≈ (N + 1)VOUTSince the secondary winding only draws current when thesynchronous switch is on, load regulation at the auxiliaryoutput will be relatively good as long as the main output isrunning in continuous mode. As the load on the primaryoutput drops and the LTC3703-5 switches to Pulse SkipMode operation, the auxiliary output may not be able tomaintain regulation, especially if the load on the auxiliaryoutput remains heavy. To avoid this, the auxiliary outputvoltage can be divided down with a conventional feedbackresistor string with the divided auxiliary output voltage fedback to the MODE/SYNC pin. The MODE/SYNC thresholdis trimmed to 800mV with 20mV of hysteresis, allowingprecise control of the auxiliary voltage and is set asfollows:

V VRRSEC MIN( )

.≈ +⎛⎝⎜

⎞⎠⎟

0 8 112

where R1 and R2 are shown in Figure 9c.

If the LTC3703-5 is operating in Pulse Skip Mode and theauxiliary output voltage drops below VSEC(MIN), the MODE/SYNC pin will trip and the LTC3703-5 will resume continu-ous operation regardless of the load on the main output.Thus, the MODE/SYNC pin removes the requirement thatpower must be drawn from the inductor primary in orderto extract power from the auxiliary winding. With the loopin continuous mode (MODE/SYNC < 0.8V), the auxiliaryoutputs may nominally be loaded without regard to theprimary output load.

The following table summarizes the possible states avail-able on the MODE/SYNC pin:Table 1.MODE/SYNC Pin ConditionDC Voltage: 0V to 0.75V Forced Continuous

Current Reversal EnabledDC Voltage: ≥ 0.87V Pulse Skip Mode Operation

No Current ReversalFeedback Resistors Regulating a Secondary WindingExt. Clock: 0V to ≥ 2V Forced Continuous

No Current Reversal

the RUN/SS pin allows an internal 4µA current source tocharge up the soft-start capacitor CSS. When the voltageon RUN/SS reaches 1V, the LTC3703-5 begins operatingat its minimum on-time. As the RUN/SS voltage increasesfrom 1V to 3V, the duty cycle is allowed to increase from0% to 100%. The duty cycle control minimizes inputsupply inrush current and elimates output voltage over-shoot at start-up and ensures current limit protection evenwith a hard short. The RUN/SS voltage is internally clampedat 4V.

If RUN/SS starts at 0V, the delay before starting isapproximately:

tVA

C s F CDELAY START SS SS, ( . / )= µ= µ1

40 25

plus an additional delay, before the output will reach itsregulated value, of:

tV V

AC s F CDELAY REG SS SS,

–( . / )≥

µ= µ3 1

40 5

The start delay can be reduced by using diode D1 inFigure 18.

Figure 18. RUN/SS Pin Interfacing

APPLICATIO S I FOR ATIO

WU UU

3.3VOR 5V RUN/SS

D1

CSS

37035 F18

RUN/SS

CSS

MODE/SYNC Pin (Operating Mode and SecondaryWinding Control)

The MODE/SYNC pin is a dual function pin that can be usedfor enabling or disabling Pulse Skip Mode operation andalso as an external clock input for synchronizing the inter-nal oscillator (see next section). Pulse Skip Mode is enabledwhen the MODE/SYNC pin is above 0.8V and is disabled,i.e. forced continuous, when the pin is below 0.8V.

In addition to providing a logic input to force continuousoperation and external synchronization, the MODE/SYNCpin provides a means to regulate a flyback winding outputas shown in Figure 9c. The auxiliary output is taken froma second winding on the core of the inductor, convertingit to a transformer. The auxiliary output voltage is set by

-

LTC3703-5

2537035fa

MODE/SYNC Pin (External Synchronization)

The internal LTC3703-5 oscillator can be synchronized toan external oscillator by applying and clocking the MODE/SYNC pin with a signal above 2VP-P. The internal oscillatorlocks to the external clock after the second clock transi-tion is received. When external synchronization is de-tected, LTC3703-5 will operate in forced continuousmode. If an external clock transition is not detected forthree successive periods, the internal oscillator will revertto the frequency programmed by the RSET resistor. Theinternal oscillator can synchronize to frequencies be-tween 100kHz and 600kHz, independent of the frequencyprogrammed by the RSET resistor. However, it is recom-mended that an RSET resistor be chosen such that thefrequency programmed by the RSET resistor is close to theexpected frequency of the external clock. In this way, thebest converter operation (ripple, component stress, etc)is achieved if the external clock signal is lost.

Minimum On-Time Considerations (Buck Mode)

Minimum on-time tON(MIN) is the smallest amount of timethat the LTC3703-5 is capable of turning the top MOSFETon and off again. It is determined by internal timing delaysand the amount of gate charge required to turn on the topMOSFET. Low duty cycle applications may approach thisminimum on-time limit and care should be taken to ensurethat:

tVV f

tONOUT

INON MIN= >

•( )

where tON(MIN) is typically 200ns.

If the duty cycle falls below what can be accommodated bythe minimum on-time, the LTC3703-5 will begin to skipcycles. The output will be regulated, but the ripple currentand ripple voltage will increase. If lower frequency opera-tion is acceptable, the on-time can be increased abovetON(MIN) for the same step-down ratio.

Pin Clearance/Creepage Considerations

The LTC3703-5 is available in two packages (GN16 andG28) both with identical functionality. The GN16 packagegives the smallest size solution, however the 0.013”(minimum) space between pins may not provide sufficient

APPLICATIO S I FOR ATIO

WU UU

PC board trace clearance between high and low voltagepins in higher voltage applications. Where clearance is anissue, the G28 package should be used. The G28 packagehas 4 unconnected pins between the all adjacent highvoltage and low voltage pins, providing 5(0.0106”) =0.053” clearance which will be sufficient for most applica-tions up to 60V. For more information, refer to the printedcircuit board design standards described in IPC-2221(www.ipc.org).

Efficiency Considerations

The efficiency of a switching regulator is equal to theoutput power divided by the input power (x100%). Per-cent efficiency can be expressed as:

%Efficiency = 100% – (L1 + L2 + L3 + ...)

where L1, L2, etc. are the individual losses as a percentageof input power. It is often useful to analyze the individuallosses to determine what is limiting the efficiency andwhat change would produce the most improvement. Al-though all dissipative elements in the circuit producelosses, four main sources usually account for most of thelosses in LTC3703-5 circuits: 1) LTC3703-5 VCC current,2) MOSFET gate current, 3) I2R losses and 4) TopsideMOSFET transition losses.

1. VCC Supply current. The VCC current is the DC supplycurrent given in the Electrical Characteristics table whichpowers the internal control circuitry of the LTC3703-5.Total supply current is typically about 2.5mA and usuallyresults in a small (

-

LTC3703-5

2637035fa

MOSFET and the synchronous MOSFET. If the twoMOSFETs have approximately the same RDS(ON), then theresistance of one MOSFET can simply be summed with theDCR resistance of L to obtain I2R losses. For example, ifeach RDS(ON) = 25mΩ and RL = 25mΩ, then total resis-tance is 50mΩ. This results in losses ranging from 1% to5% as the output current increases from 1A to 5A for a 5Voutput.

4. Transition losses apply only to the topside MOSFET inbuck mode and they become significant when operating athigher input voltages (typically 20V or greater). Transitionlosses can be estimated from the second term of the PMAINequation found in the Power MOSFET Selection section.

The transition losses can become very significant at thehigh end of the LTC3703-5 operating voltage range. Toimprove efficiency, one may consider lowering the fre-quency and/or using MOSFETs with lower CRSS at theexpense of higher RDS(ON).

Other losses including CIN and COUT ESR dissipativelosses, Schottky conduction losses during dead-time, andinductor core losses generally account for less than 2%total additional loss.

Transient Response

Due to the high gain error amplifier and line feedforwardcompensation of the LTC3703-5, the output accuracy dueto DC variations in input voltage and output load currentwill be almost negligible. For the few cycles following aload transient, however, the output deviation may belarger while the feedback loop is responding. Consider atypical 48V input to 5V output application circuit,subjected to a 1A to 5A load transient. Initially, the loop isin regulation and the DC current in the output capacitor iszero. Suddenly, an extra 4A (= 5A-1A) flows out of theoutput capacitor while the inductor is still supplying only1A. This sudden change will generate a (4A) • (RESR)voltage step at the output; with a typical 0.015Ω outputcapacitor ESR, this is a 60mV step at the output.