VG VC - EECS Instructional Support Group Home Pageee243/sp10/EE143/lectures/Lec_23.pdf · p-Si V VG...

Transcript of VG VC - EECS Instructional Support Group Home Pageee243/sp10/EE143/lectures/Lec_23.pdf · p-Si V VG...

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

1

( ) SioxFBBG VVVVV ++=−

net bias across MOS

MO

p-Si

VVG

C

inversionelectrons

depletionregion

VB

n+n+

Effect of Substrate Bias VB and Channel Bias VC

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

2

( )

( )s

da

OX

daFBBG

BCpSi

XqNC

XqNVVV

VVV

ε

φ

max2

max

21

2

++=−

−+=

M O SiEi

Efs

q(VC-VB)

Efn

pqφ

pqφ

s

daSi

XqNV

εmax

2

21

=

At the onset of strong inversion, where VG is defined as the threshold voltage

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

3

At threshold: VG – VB = VFB+Vox+VSi But VSi = 2|Φp| + (VC - VB ) => xdmax is different from no-bias case

B

SiSid qN

Vx

ε2=max

VT -VB = VFB + 2εsqNB(2|φF| + VC-VB)

Cox + 2|φF| + VC - VB

VoxVSi

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

4

Flat Band Voltage with Oxide charges

VFB is the Gate voltage required to create no charge in the Si

dxx

xxCC

QV

oxx

ox

ox

oxox

fSMFB ∫−−Φ−Φ≡

0

)(1 ρ

x = 0 x = xox

M O S

ρox (x)Qf

ρox (x) due to alkaline contaminants or trapped charge

Qf due to broken bonds at Si-SiO2 interface

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

5

VT Tailoring with Ion Implantation

Nsub

Shallow implanted dopant profile at Si-SiO2interface (approximated asa delta function)

• Acceptor implant gives positive shift (+ ∆VT)• Donor implant gives negative shift - ∆VT

Algebraic sign of VT shift is independent of n or p substrate !

OX

iT C

QV =∆

Qi = q • implant dose in Si

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

6

p-Si

implanted acceptors

Na

SiO2

Doping Profile After Implantation

SiO2

xdmax

Q

Qd

d

Qn

p-Si

(due to implanted acceptors)

Charge Distribution for V G > VT

* Valid if thickness of implanted dopants << xdmax

The VT shift can be viewed as the extra gate voltage needed todeplete the implanted dopants ~ Qi/Cox

The delta-function approximation of implanted profile

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

7

Summary : Parameters Affecting VT

6

7

n+

Na

VB

5

1

2

4

3

Dopant implant near Si/SiO2 interface

fOX Q&ρ Mφ

xox

VCQn n+

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

8

+ Qf or Qox

B threshold implant

As or P threshold implant

Xox increases

Xox increases

ΦM increases

ΦM decreases

|VCB| increases

|VCB| increases

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

9

Summary of MOS Threshold Voltage (NMOS, p-substrate)

• Threshold voltage of MOS capacitor:

• Threshold voltage of MOS transistor:

Note 1: At the onset of strong inversion, inversion charge is negligible and is often ignored in the VT expressionNote 2: VT of a MOSFET is taken as the VT value at source ( i.e., VC =VS)Note 3 : Qi = (q • implant dose ) is the charge due to the ionized donorsor acceptors implanted at the Si surface. Qi is negative for acceptors and is positive for donors

VT = VFB + 2εsqNB(2|φF|)

Cox + 2|φF| -

QiCox

VT = VFB + 2εsqNB(2|φF| + |VC-VB|)

Cox + 2|φF| + VC -

QiCox

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

10

Summary of MOS Threshold Voltage (PMOS, n-substrate)

• Threshold voltage of MOS capacitor:

• Threshold voltage of MOS transistor:

* Yes, + sign for VC term but VC (<0) is a negative bias for PMOS because theinversion holes have to be negatively biased with respect to the n-substrateto create a reverse biased pn junction.

VT = VFB - 2εsqNB(2|φF|)

Cox - 2|φF| -

QiCox

VT = VFB - 2εsqNB(2|φF| + |VC-VB|)

Cox - 2|φF| + VC -

QiCox

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

11

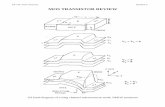

Negligible electron concentration underneath Gate region; Source-Drain is electrically open

High electron concentration underneath Gate region; Source-Drain is electrically connected

VG < Vthreshold VG > Vthreshold

Metal -Oxide-Semiconductor Transistor [ n-channel]

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

12

MOSFET I-V Analysis

n+ n+

VS VG

W

VB=0

VD

ID

L

Qn

N-MOSFET

•In general, inversion charge Qn (∝ [VG-VT]) decreases from Source towardDrain because channel potential VC increases.

VT increases

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

13

Let VT defined to be threshold voltage at Source

( )

−−=

−=

+

2V

VVC

)average(VVC)average(Q2

VV~)average(V

DSTGOX

TGOXn

DSTT [ This is an approximation ]

ID = Wt • (-q n vdrift)= W• Qn • vdrift

Inversion layer thickness Inversion layer concentration

Approximate Analysis

Note: ID is constant for all positionsalong channel

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

14

LV

EvWith DSnndrift

µ≈µ−=

DSDS

TGOXD V2

VVVC

LW

I

−−µ=

VDS

ID

Linear with VDS

Quadratic with VDS

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

15

VD saturation

n+ n+

VS=0

VD

Qn=0 at the drain

Lateral E-field → ∞Electrons moves

saturation velocity

VDsat is defined to be the value of VDwith Qn=0 at drain.

From Qn = Cox (VG -VT -VD), we get VDsat =VG-VT

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

16

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

17

VD

ID

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

18

DSDS

TGOXn

D VV

VVCLW

I

−−=

2µ

MOSFET I-V Characteristics Summary

For VD < VDsat

( )2

2 TGOXn

DsatD VVCLW

II −==µ

For VD > VDsat

Note: VDsat = VG - VT

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

19

E x

SiO2inversionlayer

Mobility of inversion charge carriers

*Carrier will experience additional scattering at theSi/SiO2 interface

*Channel mobility is lower than bulk mobility

* µ(effective) is extracted from MOSFET I-V characteristics* Typically ~0.5 of µ(bulk)

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

20

Parameter Extraction from MOSFET I-V

(A) VT VD

ID

D

S

( )

.

0

221

2

'

'

modesaturationinisMOSFEToffpinchatisDrain

VV

VqNC

VV

drainatV

VVVFor

TG

DpasOX

pDFB

T

TGD

⇒−⇒

<−⇒

++

++=

>=

φε

φ

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

21

( )2TDDsatD VV

LW

kII −==∴

VDVT

DI

LkW

slope=

VG

µnCOX

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

22

Alternative way to extract VT

•Measure ID versus VG for a fixed small VDS (say <100mV)

The intercept of ID versus VG plot on VG-axis is VT.

( ) DSTGOXn

DSDS

TGOXn

D

VVVCLW

V2

VVVC

LW

I

−µ

≈

−−

µ=

VT

VG

ID

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

23

VD

ID

VB(varies)

VD

VB =0 VB1 VB2

VT0 VT1 VT2

DI

( ) ( )

OX

as

pSBp

SBTSBT

CqN

V

VwithVVwithV

ε

φφγ

2

22

00

=

−+

=−≠≡

(B) Body Coefficient γ

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

24

ID

VD

VG2

VG1

(C)

VD

( ) DTGOXnD

D

DD

TGOXnD

VsmallforVVL

WC

VI

VV

VVCL

WI

−=∂∂

−−=

µ

µ2

ID

VG slope

LW

COXnµ

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

25

(D) Transconductance gm

(a) For VDS<VDsat

(b) For VDS > VDsat

DVfixedG

Dm V

Ig

∂∂

≡

DSOXnG

D

DSDS

TGOXn

D

VL

WC

VI

VV

VVCLW

I

⋅=∂∂

∴

−−=

µ

µ2

( )

( )TGOXn

G

D

TGOXn

DsatD

VVCLW

VI

VVCLW

II

−⋅=∂∂

−==

µ

µ 2

2

ID

VDS

VG1+∆VG

VG1

VDsat

[gm varies with VDS]

[gmsat varies with VG]

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

26

ID

VD

VDsat

real

ideal

n+ n+

Qn

( ) ( )1

2

)(01.01.0~

12

−

+−=

volttoTypically

VVVk

I DSTGDsat

λ

λ

(E) Channel Modulation Parameter λ

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

27

Short Channel Effect on VT

VT

idealanalysis

Ldepletionchargecontrolledby gate.

n+ n+

VG

pdepletion layer

L

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

28

n+ n+

VS=0 VD=0

Wo

x

WoXj+Wo

Xj

Xj

Xj

L’

L

( )[ ]

−+−=

−−+−=

−=

12

12

2

2'22

j

oj

jooj

XW

XL

XWWXL

xLL Note: Wo is xdmax

Sameelectric potentialbecause of heavily doped n+

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

29

fXW

LX

WWLL

Nq

j

oj

ideal

actual

oa

≡

−+−=

=∴

⋅⋅+

⋅⋅=

12

11

21

Area of gate charge distribution

“Yau Model” for short-channel effect.

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

30

•Implantation at low energy•Small Dt.•Minimize channeling and transient enhance diffusion

To make f 1

Xj

Wo •Increase Na

L large

S/D S/D

L small

S/DS/D

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

31

VT

L

Large VDS

VDS ~ 0

Effect of VDS on VT Lowering

Large VDS ⇒ Larger S/D depletion charge at the drain side ⇒ Smaller depletion region charge contributed by gate⇒ VT starts to decrease at larger L

n+ n+

VG

depletion layer

Depletion charge contributedby gate

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

32

parasiticchargewhich has to be createdby gate bias

∴VT is larger than ideal analysis.

Fox Fox

W

Ideal Depletion charge

W

Narrow Width Effect (related to W)

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

33

VT

W

VT

L

Narrow Width Effect

Narrow Channel Effect

Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

34

Small Geometry Effects Summary

W

L

Actual gate control charge

Idealgate controlcharge