UNIT 3: FIELD EFFECT TRANSISTORS FIELD … YEAR/EDC/Unit 3.pdf2.Has amplification factor β 2.Has...

Transcript of UNIT 3: FIELD EFFECT TRANSISTORS FIELD … YEAR/EDC/Unit 3.pdf2.Has amplification factor β 2.Has...

UNIT – 3: FIELD EFFECT TRANSISTORS

FIELD EFFECT TRANSISTOR:

The field effect transistor is a semiconductor device, which depends for its operation on the

control of current by an electric field. There are two of field effect transistors:

1. JFET (Junction Field Effect Transistor)

2. MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

The FET has several advantages over conventional transistor.

1. In a conventional transistor, the operation depends upon the flow of majority and

minority carriers. That is why it is called bipolar transistor. In FET the operation

depends upon the flow of majority carriers only. It is called unipolar device.

2. The input to conventional transistor amplifier involves a forward biased PN

junction with its inherently low dynamic impedance. The input to FET involves a

reverse biased PN junction hence the high input impedance of the order of M-

ohm.

3. It is less noisy than a bipolar transistor.

4. It exhibits no offset voltage at zero drain current.

5. It has thermal stability.

6. It is relatively immune to radiation.

The main disadvantage is its relatively small gain bandwidth product in comparison with

conventional transistor.

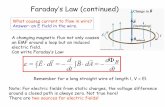

OPERATION OF FET:

Consider a sample bar of N-type semiconductor. This is called N-channel and it is electrically

equivalent to a resistance as shown in fig. 15.

Fig. 15

Ohmic contacts are then added on each side of the channel to bring the external

connection. Thus if a voltage is applied across the bar, the current flows through the channel.

The terminal from where the majority carriers (electrons) enter the channel is called

source designated by S. The terminal through which majority carriers leaves the channel is called

drain and designated by D. For an N-channel device, electrons are the majority carriers. Hence

the circuit behaves like a dc voltage VDS applied across a resistance RDS. The resulting current is

the drain current ID. If VDS increases, ID increases proportionally.

Now on both sides of the n-type bar heavily doped regions of p-type impurity have been

formed by any method for creating pn junction. These impurity regions are called gates (gate1

and gate2) as shown in fig. 16.

Both the gates are internally connected and they are grounded yielding zero gate source

voltage (VGS =0). The word gate is used because the potential applied between gate and source

controls the channel width and hence the current.

As with all PN junctions, a depletion region is formed on the two sides of the reverse

biased PN junction. The current carriers have diffused across the junction, leaving only

uncovered positive ions on the n side and negative ions on the p side. The depletion region width

increases with the magnitude of reverse bias. The conductivity of this channel is normally zero

because of the unavailability of current carriers.

Fig.16

The potential at any point along the channel depends on the distance of that point from

the drain, points close to the drain are at a higher positive potential, relative to ground, then

points close to the source. Both depletion regions are therefore subject to greater reverse voltage

near the drain. Therefore the depletion region width increases as we move towards drain. The

flow of electrons from source to drain is now restricted to the narrow channel between the no

conducting depletion regions. The width of this channel determines the resistance between drain

and source.

Consider now the behavior of drain current ID vs drain source voltage VDS. The gate

source voltage is zero therefore VGS= 0. Suppose that VDS is gradually linearly increased linearly

from 0V. ID also increases.

Since the channel behaves as a semiconductor resistance, therefore it follows ohm's law.

The region is called ohmic region, with increasing current, the ohmic voltage drop between the

source and the channel region reverse biased the junction, the conducting portion of the channel

begins to constrict and ID begins to level off until a specific value of VDS is reached, called the

pinch of voltage VP.

At this point further increase in VDS do not produce corresponding increase in ID.

Instead, as VDS increases, both depletion regions extend further into the channel, resulting in a no

more cross section, and hence a higher channel resistance. Thus even though, there is more

voltage, the resistance is also greater and the current remains relatively constant. This is called

pinch off or saturation region. The current in this region is maximum current that FET can

produce and designated by IDSS. (Drain to source current with gate shorted).

Fig. 17

As with all pn junctions, when the reverse voltage exceeds a certain level, avalanche breakdown

of pn junction occurs and ID rises very rapidly as shown in fig. 17.

Consider now an N-channel JFET with a reverse gate source voltage as shown in fig. 18.

Fig. 18

Fig. 19

The additional reverse bias, pinch off will occur for smaller values of | VDS |, and the maximum

drain current will be smaller. A family of curves for different values of VGS(negative) is shown

in fig. 19.

Suppose that VGS= 0 and that due of VDS at a specific point along the channel is +5V with

respect to ground. Therefore reverse voltage across either p-n junction is now 5V. If VGS is

decreased from 0 to –1V the net reverse bias near the point is 5 - (-1) = 6V. Thus for any fixed

value of VDS, the channel width decreases as VGS is made more negative.

Thus ID value changes correspondingly. When the gate voltage is negative enough, the

depletion layers touch each other and the conducting channel pinches off (disappears). In this

case the drain current is cut off. The gate voltage that produces cut off is symbolized VGS(off) . It

is same as pinch off voltage.

Since the gate source junction is a reverse biased silicon diode, only a very small reverse

current flows through it. Ideally gate current is zero. As a result, all the free electrons from the

source go to the drain i.e. ID = IS. Because the gate draws almost negligible reverse current the

input resistance is very high 10's or 100's of M ohm. Therefore where high input impedance is

required, JFET is preferred over BJT. The disadvantage is less control over output current i.e.

FET takes larger changes in input voltage to produce changes in output current. For this reason,

JFET has less voltage gain than a bipolar amplifier.

Tran conductance Curves:

The trans conductance curve of a JFET is a graph of output current (ID) vs input voltage (VGS) as

shown in fig. 20. By reading the value of ID and VGS for a particular value of VDS, the trans

conductance curve can be plotted. The trans conductance curve is a part of parabola. It has an

equation of

Fig. 20

(

)

Data sheet provides only IDSS and VGS(off) value. Using these values the trans conductance curve

can be plotted.

The trans-conductance is denoted gm.

Definition of gm using transfer characteristics

Fig.21. Transfer characteristics of FET

Symbol representation

Comparison between BJT & FET

BJT FET

1.BJT controls large output(Ic) by means of a

relatively small base current. It is a current

controlled device.

1.FET controls drain current by means of

small gate voltage. It is a voltage controlled

device

2.Has amplification factor β 2.Has trans-conductance gm.

3.Has high voltage gain 3.Does not have as high as BJT

4.Less input impedance 4.Very high input impedance

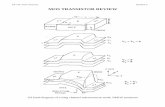

MOSFET

MOSFETs are of two types;

Enhancement type

Depletion type

Operation of Enhancement MOSFET

Fig.22. Fig.23.

Operation with No Gate Voltage

With no bias applied to the gate, two back-to-back diodes exist in series between drain

and source. The two back-to-back diodes prevent current conduction from drain to source when

a voltage vDS is applied. The resistance is of the order of 10 to 12 ohms

Creating a Channel for Current Flow

If S and D are grounded and a positive voltage is applied to G, the holes are repelled

from the channel region downwards, leaving behind a carrier-depletion region.

Further increasing VG attracts minority carrier (electrons) from the substrate into the

channel region. When sufficient amount of electrons accumulate near the surface of the

substrate under the gate, an n region is created-called as the inversion layer.

Applying a Small vDS

When a small potential is applied across the Gate and source, it pushes away the holes

towards the substrate and attract electrons from the Drain and Source into the channel region.

When sufficient electrons are formulated beneath the Gate area, current flows between the

Drain and the Source. (Basically the holes are pushed away in N channel – NMOS type to be

replaced by the electrons from both the Source and the Drain creating a channel of N majority

causing current to flow from Drain to Source.

Applying a small vDS (~ 0.1 or 0.2 V) causes a current iD to flow through the induced

n channel from D to S. The magnitude of iD depends on the density of electrons in the channel,

which in turn depends on vGS. For vGS = Vt (threshold voltage), the channel is just induced

and the conducted current is still negligibly small.

As vGS > Vt, depth of the channel increases, iD will be proportional to (vGS – Vt),

known as excess gate voltage or effective voltage.

Increasing vGS above Vt enhances the channel, hence it is called enhancement type

MOSFET. Note that iG=0.

Fig.24. Fig.25.

Operation as vDS is Increased

vDS appears as a voltage drop across the channel. Voltage across the oxide decreases

from vGS at S to vGS-Vt at D. The channel depth will be tapered, and become more tapered as

vDS isvGS-vDS = Vt, the channel will be pinched off. Increasing vDS beyond this value has no

effect on the channel shape and iD saturates (remains constant) at this value. The MOSFET

enters the saturation region of operation.

vDSsat=vgs-Vt

Fig.26. The drain current iD versus the drain-to-source voltage vDS for an

enhancement-type NMOS transistor operated with vGS > Vt.

The symbol for Enhancement n channel MOSFET is as shown in Fig.27

Fig.27.

There are two types of E-MOSFETs

nMOS or n-channel MOSFETs

pMOS or p-channel MOSFETs

Advantages of FET over BJT are:

a) No minority carriers

b) High input impedance

c) It is a voltage controlled device

d) Better thermal stability

v DSsat v GS V tv DSsat v GS V tv DSsat v GS V t

v DSsat v GS V t

The various symbol representation

Fig.28

DEPLETION TYPE MOSFET-D MOSFET

The depletion type MOSFET has similar structure to that the enhancement type

MOSFET but with one important difference:

The depletion MOSFET has a physically implanted channel. Thus an n-channel

depletion-type MOSFET has an n-type silicone region connecting the source and drain (both +n)

at the top of the type substrate. Thus if a voltage vDS is applied between the drain and source, a

current iD flows for vGS = 0 i.e there is no need to induce the channel.

The channel depth and hence its conductivity is controlled by vGS. Applying a positive

vGS enhances the channel by attracting more electrons. The reverse when applying negative

volt. The negative voltage is said to deplete the channel (depletion mode).

The symbol for n channel D- MOSFET is as shown in Fig.29

Fig.29

Basic Operation and Characteristics

The gate-to-source voltage is set to zero volts by the direct connection from one terminal

to the other, and a voltage VDS is applied across the drain-to-source terminals as shown in Fig.

30. The result is an attraction for the positive potential at the drain by the free electrons of the n-

channel and a current similar to that established through the channel of the JFET. In fact, the

resulting current with VGS 0 V continues to be labeled IDSS, as shown in Fig. 31

Fig. 30. n-Channel depletion-type MOSFET with VGS= 0 V and an applied voltage VDD

.

As VGS has been set at a negative voltage such as -1 V. The negative potential at the

gate will tend to pressure electrons toward the p-type substrate (like charges repel) and attract

holes from the p-type substrate (opposite charges attract) as shown in Fig. 32. Depending on the

magnitude of the negative bias established by VGS, a level of recombination between electrons

and holes will occur that will reduce the number of free electrons in the n-channel available for

conduction. The more negative the bias, the higher the rate of recombination. The resulting level

of drain current is therefore reduced with increasing negative bias for VGS as shown in Fig. 31

for VGS=-1 V, -2 V, and so on, to the pinch-off level of -6 V. The resulting levels of drain

current and the plotting of the transfer curve proceeds exactly as described for the JFET.

The Drain and Transfer characteristics of n channel D- MOSFET is as shown in Fig.31.

For positive values of VGS, the positive gate will draw additional electrons (free

carriers) from the p-type substrate due to the reverse leakage current and establish new carriers

through the collisions resulting between accelerating particles. As the gate-to-source voltage

continues to increase in the positive direction, Fig. 31 reveals that the drain current will increase

at a rapid rate for the reasons listed above. Due to the rapid rise, the user must be aware of the

maximum drain current rating since it could be exceeded with a positive gate voltage.

Fig.31.

Fig.32

Ebers – Moll model :

Ebers – Moll model for p–n-p transistor involves two ideal diodes placed back to back with

saturation current IEo and – Ico and two dependent current – controlled current sources shunting the

ideal diodes.

Fig.32

Currents and Voltages used in the Ebers-Moll equations

The equations of Ic and IE from Ebers – moll model. Applying KCL to the collector node,

we get

αN IE + IC = I

IC = I – αN IE

IC = - αN IE + I ; Where I is diode current.

IC = - αN IE + I0 (e Vc / VT – 1)

I0 = - IC0 ; Where , I0 is the magnitude of reverse saturation current .

... IC = - αN IE – ICO (e VC / VT )

Ebers moll model :-

Fig.32

The Ebers-moll model for a PNP transistor

The general expression for collector current IC of a transistor for any voltage across

collector junction Vc and emitter current IE is

IC = -αN IN – ICO (e VC / VT – 1)

Here, subscript N to α indicates that we are using transistor in a normal manner. When

we interchange the role of emitter and collector we operate transistor in a inverted function. In

such case current and junction voltage relationship for transistor is given by

IE = - αI IC – IEO (e vE / VT – 1)

Here, subscript I to α indicates that we are using transistor in a inverted manner, αI is the

inverted common – base current Gain.

IEO – The emitter junction reverse saturation current.

VE – The voltage drop from p – side to N – side at the emitter junction.

Similarly applying KCL to emitter node we get

IE + αI IC = I

IE = I – αI IC

= - αI IC + I

IE = - αI IC + I0 (e VE / VT – 1)

IE = -αI IC – IE0 (e VE / VT – 1)

This model is valid for both forward & reverse static voltages applied across the

transistor junction.

In the above model, by making the base width much large than the diffusion length of

minority carriers in the base, all mining carriers will recombine in the base and none will survive

to reach the collector.

Under there conditions, transistor action ceases, and we simply have two diodes placed

back. Therefore it is impossible to construct a transistor by simply connecting two separate

diodes back to back.

FET BIASING:

The general relationship that can be applied to the DC analysis of all FET amplifiers are

For JFETS and depletion –type MOSFETS shockley‟s equation is applied to relate the input and

output quantities:

(

)

For enchancement – type MOSFET‟S the following equation is applied:

Where

– Reverse saturation current

– Pinch of voltage

FIXED BIAS CONFIGURATION

Consider the configuration shown below which includes the AC levels vi and VO and the

coupling capacitors (C1 and C2).

For DC analysis, capacitors acts like open circuit ie. At DC , f = 0, capacitance =

For AC analysis, capacitors acts like short circuits.

The resistors RG is to ensure that Vi appears at the input to the FET amplifier for AC analysis.

For dc analysis,

Replace by short circuit in the circuit.

To find

Apply KVL to gate circuit,

1

Since is fixed DC supply the voltage

is fixed in magnitude, resulting in the notation

“fixed bias configuration”.

To find

is controlled by shockley‟s equation,

(

)

SELF BIAS CONFIGURATION

This eliminates the need for two DC suppliers.

DC analysis:

For DC analysis, capacitors are replaced by „open circuits‟ and the resistors RG replaced by short

– circuit since IG = 0A.

Therefore the circuit reduce to,

To find

apply KVL to gate circuit,

1

Function of and not fixed as in fixed bias.

To find

by shockley‟s equation,

(

)

(

)

(

)

2

To find

Apply KVL to output circuit,

3

VOLTAGE – DIVIDER BIASING:

Consider the circuit shown.

DC analysis:

Remove the AC source

O.C all the capacitors.

So that the circuit reduce to

From the circuit,

1

By voltage divider sub

To find

apply KVL to gate circuit,

2

To find

Apply KVL to drain circuit,