Software Architectures, Week 3 - Microservice-based Architectures

Time-to-Digital Converter Architectures Using Two ...

Transcript of Time-to-Digital Converter Architectures Using Two ...

Time-to-Digital Converter Architectures

Using Two Oscillators

With Different Frequencies

Kosuke Machida, Yuki Ozawa, Yudai Abe

Haruo Kobayashi

Gunma University

Oct. 18, 2018

Session 6B-II

Mixed-Signal IC Designs

and ATE

1/35

2/48

Research Objective

Investigation of TDC architectures

with Verner oscillators

● Analog centric one

- Using trigger circuits

- Two oscillators with different frequencies

- No self-calibration required

● Digital centric one

- Two ring oscillators

with different frequencies

3/48

Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

4/48

Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

5/48

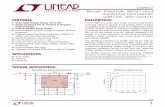

Time-to-Digital Converter

6/48

TDC Application Examples (1)

7/48

TDC Application Example (2)

8/48

Comparison of TDC Architectures

9/48

Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

10/48

Voltage can be held

Time difference cannot be held

Time difference can be held !

Truth

Myth

Myth and Truth of Time Signal

11/48

Trigger Circuit

t0 t0t0

12/48

T/H Circuit

13/48

Trigger Circuit Waveforms

14/48

Oscillate with initial phase

at input timing

Input START, STOP signal

It can hold the time difference using two trigger circuits

1step 2step 3step 4step 5step 6step 7step

Δ𝑇 Δ𝑇

One-shot Timing Measurement Using Trigger Circuit

Proposal

15/48

SAR-ADC VS. SAR-TDC

SAR ADC : Comparator DAC

SAR TDC : D-FF Delay line

SAR-ADC

SAR-TDC

Y. Ozawa, H. Kobayashi, et. al., “SAR TDC Architecture with Self-Calibration Employing Trigger Circuit,”IEEE Asian Test Symposium, Taipei (Nov. 2017).

16/48

SAR TDC Operation

Example ΔT = 4.3 τ

STEP1

100

1

17/48

SAR TDC Operation

Example ΔT = 4.3 τ

STEP2

110

0

18/48

SAR TDC Operation

Example ΔT = 4.3 τ

STEP3

101

0

19/48

SAR TDC Operation

Example ΔT = 4.3 τ

STEP4 (Stable)

100

100Digital output:4

1

20/48

Low Frequency Clock Measurement

Low frequencySTART

SAR TDC

CLK1

STOP

SAR TDC

CLK2

Short testing time for low frequency repetitive timing

High frequency

21/48

Verner Oscillation TDC

f1: known

f2: known

Start oscillation f1 at START edge

f2 at STOP edge

What about using different frequencies ?

22/48

Verner Oscillation TDC Operation

t0 = f (f1, f2, number of , …, number of , …)

f1

f2

f1≒ f2 Time

resolution

23/48

Usage of Different but Close Frequencies

f1≒ f2

Equivalent

Sampling

24/48

Design Tradeoff

f1

f2

Fine time resolution

Long Measurement timeWide input time range

Tin = 1/f1, 1/f2 Tmeas = Tin x Tin / t’

Tin

Tmeas

25/48

Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

26/48

Proposed TDC Architecture

f1: known

f2: known

# of

# of

27/48

Logic Circuit for Time Measurement

# of

# of

28/48

D1 Sampling by D2

29/48

Counter & Update

30/48

Deviation Points by Time Difference

31/48

Deviation and Time Resolution

32/48

Equivalent Time Sampling

t’=1/f2

33/48

Waveform Reconstruction

Sampled points

rearrangement

High frequency

operation

Low frequency

operation

34/48

Measurement Time Resolution

35/48

Proposed TDC Linearity

36/48

Simulation Verification of Proposed TDC

37/48

Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

38/48

Ring Oscillator with Start

Input

Output

39/48

Digital Centric TDC

Ring oscillator frequencies

f1 Counter 1 output N1 / reference time Tref

f2 Counter 2 output N2 / reference time Tref

f1

f2

≒≒

N1

N2

40/48

Outline

Research Background

Measurement Principle

Analog Centric TDC

Digital Centric TDC

Discussion & Conclusion

41/48

TDC Architecture Comparison

Excellent Good Bad

42/48

Comparison of Time and Voltage

● Dynamic range of time domain signal

can be infinite.

● Time flows in one direction.

● Ring oscillator can be often used

for time domain signal processing.

● Exact frequency division is possible,

whereas exact voltage division is difficult.

● Frequency is a stable signal.

● Jitter is a difficult problem.

● Time as well as voltage can be held.

● Time as well as voltage can be amplified.

● New TDC architectures can be inspired by

existing ADC architectures.

43/48

Conclusion

● Verner Oscillator TDC architectures

- Analog centric and digital centric ones

- Using two oscillators

with different frequencies

Can be shared among multi-channel TDCs

- No delay line

- No self-calibration required

- Design tradeoff

Measurement time

Time resolution

Input time range

44/48

Time is very important !

45/48

Appendix :N-Stage Trigger Circuit

S. Sakurai, H. Kobayashi, et. al., “Study OF Multi-Stage Oscilloscope Trigger Circuit,”IEEE ISPACS, Xiamen, (Nov. 2017)

46/48

Three-stage Trigger Circuit

Trigger input

Output

c

Track&Hold

Track&Hold

Σ

Input

to

Output

to

sinωt

Track&Hold

sin(ωt+2π/3)

+

+

+

-

-

-

sin(ωt+4π/3)

F1

F2

F3

S1

S2

S3

47/48

Analysis of Three-stage Trigger Circuit

48/48

N-Stage Trigger Circuit

Track&Hold

Track&Hold

Σ

Input

Output

sinωt

Track&Hold

sin(ωt+θ)

+

+

+sin(ωt+2θ)

F1

F2

F3

S1

S2

S3

Track&Hold

Sn

sin(ωt+nθ)

Σ

Σ

Σ

・・・

・・・

・・・

Fn ・・・

Σ+

Vo_N・・・

to

Trigger circuit is a key !Trigger circuit for TDC T/H circuit for ADC.