Small-signal Model (very preliminary) Bulk CMOS Process …class.ece.iastate.edu/ee330/lectures/EE...

Transcript of Small-signal Model (very preliminary) Bulk CMOS Process …class.ece.iastate.edu/ee330/lectures/EE...

EE 330Lecture 18

Small-signal Model (very preliminary)

Bulk CMOS Process Flow

How many models of the MOSFET do we have?

Switch-level model (2)

Square-law model (with λ and bulk additions)

α-law model (with λ and bulk additions)

BSIM model

Square-law model

BSIM model (with binning extensions)

BSIM model (with binning extensions and process corners)

Review from Last Lecture

ID

VDS

VGS1

VGS2

VGS3

Actual

Modeled with one model

Local Agreement

with Any Model

(and W/L variations or

Process Variations)

(and W/L variations or

Process Variations)

(and W/L variations or

Process Variations)

(and W/L variations or

Process Variations)

The Modeling Challenge

VDS

VBS = 0

VGS

ID

IG

IB

D 1 GS DS

G 2 GS DS

B 3 GS DS

I = f V ,V

I = f V ,V

I = f V ,V

Difficult to obtain analytical functions that

accurately fit actual devices over bias, size, and

process variations

Review from Last Lecture

Model Status

Simple dc Model

Small

Signal

Frequency

Dependent Small

Signal

Better Analytical

dc Model

Sophisticated Model

for Computer

Simulations

Simpler dc Model

Square-Law Model

Square-Law Model (with extensions for λ,γ effects)

Short-Channel α-law Model

BSIM Model

Switch-Level Models

• Ideal switches

• RSW and CGS

Review from Last Lecture

D D

S S

G G

D

BG

S

D

BG

S

VDS

VGSVBS

ID

IG IB

0

0.5

1

1.5

2

2.5

3

0 1 2 3 4 5

VDS

ID

VGS1

VGS2

VGS4

VGS3

GS4 GS3 GS2 GS1V V V V > 0

VDS

GS Tn

DS

D n OX GS Tn DS GS DS GS Tn

2

n OX GS Tn GS Tn DS GS Tn

G B

0 V V

VWI μ C V V V V V V V V

L 2

Wμ C V V V V V V V

2L

I =I =0

Tn

D D

S S

G G

D

BG

S

D

BG

S

VDS

VGS

VBS

ID

IG IB

GS Tp

DS

D p OX GS Tp DS GS Tp DS GS Tp

2

p OX GS Tp GS Tp DS GS Tp

G B

0 V V

VWI -μ C V V V V V V V V

L 2

W-μ C V V V V V V V

2L

I =I =0

n-channel …. p-channel modeling

Models essentially the

same with different signs

and model parametersRev

iew

fro

m L

ast

Lect

ure

Model Relationships

Determine RSW and CGS in the switch-level model for an n-channel MOSFET

from square-law model in the 0.5u ON CMOS process if L=1u, W=1u

(Assume μCOX=100μAV-2, COX=2.5fFu-2,VT0=1V, VDD=3.5V, VSS=0)

GS T

DS

D OX GS T DS GS DS GS T

2

OX GS T GS T DS GS T

0 V V

VWI μC V V V V V V V V

L 2

WμC V V V V V V V

2L

T

when SW is on, operation is “deep” triode

Review from Last Lecture

VGS

RSWn

CGSn

S

DG

Model Relationships

(Assume μCOX=100μAV-2, COX=2.5fFu-2,VT0=1V, VDD=3.5V, VSS=0)

DS

D OX GS T DS OX GS T DS

VW WI μC V V V μC V V V

L 2 L

14

14 3 5 1

1

K

E

GS DD

GS

DS

SQ

D V =VOX GS T

V =3.5V

V 1R =

WIμC V V ( ) .

L

CGS= COXWL = (2.5fFµ-2)(1µ2) = 2.5fF

Determine RSW and CGS for an n-channel MOSFET from square-law model

in the 0.5u ON CMOS process if L=1u, W=1u

When on operating in deep triode

VGS

RSWn

CGSn

S

DG

Review from Last Lecture

Model Relationships

( COX=2.5fFu-2,VT0=1V, VDD=3.5V, VSS=0)

GS T

DS

D OX GS T DS GS DS GS T

2

OX GS T GS T DS GS T

0 V V

VW-I μC V V V V V V V V

L 2

WμC V V V V V V V

2L

T

When SW is on, operation is “deep” triode

Determine RSW and CGS for an p-channel MOSFET from square-law model

in the 0.5u ON CMOS process if L=1u, W=1u

Observe µn\ µp≈3

VGS

RSWp

CGSp

S

DG

Review from Last Lecture

Model Relationships

DS

D p OX GS T DS p OX GS T DS

VW W-I μ C V V V μ C V V V

L 2 L

112

1 14 3 5 1

3 1GS DD

GS

DS

SQ

D V =Vp OX GS T

V =3.5V

-V 1R =

W-Iμ C V V ( ) .

L

K

E

CGS= COXWL = (2.5fFµ-2)(1µ2) = 2.5fF

Determine RSW and CGS for an p-channel MOSFET from square-law model

in the 0.5u ON CMOS process if L=1u, W=1u

( COX=2.5fFu-2,VT0=1V, VDD=3.5V, VSS=0)

Observe µn\ µp≈3

Observe the resistance of the p-channel device is approximately 3 times

larger than that of the n-channel device for same bias and dimensions !

Review from Last Lecture

VGS

RSWp

CGSp

S

DG

Modeling of the MOSFET

Drain

Gate Bulk

ID

ID IB

VDS

VBS

VGS

Goal: Obtain a mathematical relationship between the

port variables of a device.

Simple dc Model

Small

Signal

Frequency

Dependent Small

Signal

Better Analytical

dc Model

Sophisticated Model

for Computer

Simulations

Simpler dc Model

BSDSGS3B

BSDSGS2G

BSDSGS1D

V,,VVfI

V,,VVfI

V,,VVfI

Small-Signal Model

Goal with small signal model is to predict performance of circuit or device in the vicinity of an operating point

Operating point is often termed Q-point

Small-Signal Modely

x

Q-point

XQ

YQ

Analytical expressions for small signal model will be developed later

Technology Files

• Design Rules

• Process Flow (Fabrication Technology)

• Model Parameters

n-well

n-well

n-

p-

Bulk CMOS Process Description• n-well process

• Single Metal Only Depicted

• Double Poly− This type of process dominates what is used for high-volume “low-

cost” processing of integrated circuits today

− Many process variants and specialized processes are used for lower-

volume or niche applications

− Emphasis in this course will be on the electronics associated with the

design of integrated electronic circuits in processes targeting high-

volume low-cost products where competition based upon price

differentiation may be acute

− Basic electronics concepts, however, are applicable for lower-volume

or niche applicaitons

Components Shown

• n-channel MOSFET

• p-channel MOSFET

• Poly Resistor

• Doubly Poly Capacitor

A A’

B’B

C

C’

D

D’

Consider Basic Components Only

Well Contacts and Guard Rings Will be Discussed Later

A A’

B’B

A A’

B’B

A A’

B’B

n-channel MOSFET

S

D

G

S

D

BG

Metal details hidden to reduce clutter

A A’

B’B

S

D

BG

W L

A A’

B’B

n-channel MOSFET

Capacitor

p-channel MOSFET

Resistor

n-well

n-well

n-

p-

A A’

B’B

N-well Mask

A A’

B’B

N-well Mask

Detailed Description of First Photolithographic Steps Only

• Top View

• Cross-Section View

~

Blank Wafer

p-doped Substrate

ExposeDevelop

Photoresistn-well Mask

Implant

A A’

B’B

Will use positive photoresist(exposed region soluble in developer)

A-A’ Section

B-B’ Section

PhotoresistN-well MaskExposureDevelop

A-A’ Section

B-B’ Section

Implant

N-well Mask

A-A’ Section

B-B’ Sectionn-well

n-well

n-well

n-

p-

A A’

B’B

Active Mask

A A’

B’B

Active Mask

Active Mask

A-A’ Section

B-B’ Section

Field Oxide Field Oxide Field Oxide

Field Oxide

n-well

n-well

n-

p-

A A’

B’B

Poly1 Mask

A A’

B’B

Poly1 Mask

A A’

B’B

n-channel MOSFET

Capacitor

P-channel MOSFET

Resistor

Poly plays a key role in all four types of devices !

Poly 1 Mask

A-A’ Section

B-B’ Section

Gate Oxide Gate Oxide

n-well

n-well

n-

p-

A A’

B’B

Poly 2 Mask

A A’

B’B

Poly 2 Mask

Poly 2 Mask

A-A’ Section

B-B’ Section

n-well

n-well

n-

p-

A A’

B’B

P-Select

A A’

B’B

P-Select

P-Select Mask – p-diffusion

A-A’ Section

B-B’ Section

p-diffusion

Note the gate is self aligned !!

n-Select Mask – n-diffusion

A-A’ Section

B-B’ Section

n-diffusion

n-well

n-well

n-

p-

A A’

B’B

Contact Mask

A A’

B’B

Contact Mask

Contact Mask

A-A’ Section

B-B’ Section

n-well

n-well

n-

p-

A A’

B’B

Metal 1 Mask

A A’

B’B

Metal 1 Mask

Metal Mask

A-A’ Section

B-B’ Section

A A’

B’B

A A’

B’B

n-channel MOSFET

Capacitor

P-channel MOSFET

Resistor

Should now know what you can do in this process !!

Can poly be connected to active under gate?

Can poly be connected to active any place?

Can metal be placed under poly to isolate it from bulk?

Can metal connect to active?

Can metal connect to substrate when on top of field oxide?

How can metal be connected to substrate?

Can metal 2 be connected directly to active?

Could a process be created that will result in an answer of YES to most of above?

Can metal 2 be connected to metal 1?

Can metal 2 pass under metal 1?

Semiconductor and

Fabrication Technology

CAD Tools

Device Operation

and Models

Circuit Structures and

Circuit Design

How we started this course

Semiconductor and

Fabrication Technology

CAD Tools

Device Operation

and Models

Circuit Structures

and Circuit Design

Thanks for your patience !!

The basic concepts should have now come together

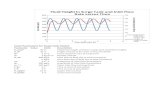

How does the inverter delay compare between a 0.5u

process and a 0.18u process?

VIN VOUT

VDD

VSS

VIN VOUT

How does the inverter delay compare between a 0.5u process and a 0.18u process?

VIN

VOUT

Assume n-channel and p-channel devices with L=Lmin, W=1.5Lmin

tHL=RpdCL

tLH=RpdCL

n

pd

n OX n DD TN

LR

C W V V

p

pu

p OX p DD TP

LR

C W V V

L OX n n p pC C W L W L

Note 0.18u process is much faster than 0.5u process

Feature 0.5 0.18 Units

Vtn 0.81 0.5 V

Vtp -0.92 -0.53 V

uCoxn 109.6 344 uA/V^2

uCoxp 39.4 72.6 uA/V^2

Cox 2.51 8.5 fF

Vdd 5 1.8 V

fosc-31 94.5 402.8 MHz

Feature 0.5 0.18 Units

CL 1.88 0.83 fF

Rpd 1452 1491 ohms

Rpu 2858 3941 ohms

THL 2.73 1.23 psec

TLH 5.38 3.26 psec

f 123 223 GHz

End of Lecture 18