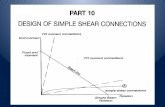

Presentación MSP430G2x53

description

Transcript of Presentación MSP430G2x53

Micocontrolador TEXAS

MSP430G2x53

FEATURES• Low Supply-Voltage Range: 1.8 V to 3.6 V • Universal Serial Communication Interface• Ultra-Low Power Consumption (USCI)– Active Mode: 230 μA at 1 MHz, 2.2 V – Enhanced UART Supporting Auto Baudrate– Standby Mode: 0.5 μA Detection (LIN)– Off Mode (RAM Retention): 0.1 μA – IrDA Encoder and Decoder• Five Power-Saving Modes – Synchronous SPI• Ultra-Fast Wake-Up From Standby Mode in – I2C™Less Than 1 μs • On-Chip Comparator for Analog Signal• 16-Bit RISC Architecture, 62.5-ns Instruction Compare Function or Slope Analog-to-DigitalCycle Time (A/D) Conversion• Basic Clock Module Configurations • 10-Bit 200-ksps Analog-to-Digital (A/D)Converter With Internal Reference, Sample-– Internal Frequencies up to 16 MHz With and-Hold, and Autoscan (See Table 1)Four Calibrated Frequency• Brownout Detector– Internal Very-Low-Power Low-Frequency(LF) Oscillator • Serial Onboard Programming,

No External Programming Voltage Needed,– 32-kHz Crystal Programmable Code Protection by Security– External Digital Clock Source Fuse• Two 16-Bit Timer_A With Three • On-Chip Emulation Logic With Spy-Bi-WireCapture/Compare Registers Interface

El MSP430 familia de ultra-bajo consumo de energía de microcontroladores de Texas Instruments se compone de varios dispositivos con diferentes conjuntos de periféricos destinados para diversas aplicaciones.

La arquitectura, junto con cinco modos de bajo consumo modos, se ha optimizado para lograr la vida extendida de la batería en aplicaciones de medición portátiles. El dispositivo cuenta con una poderosa CPU RISC de 16 bits, registros de 16 bits, y los generadores de constantes que contribuyen a la eficiencia del código máximo.El oscilador controlado digitalmente (DCO) permite despertar de los modos de bajo consumo al modo activo en menos de 1 ms.

La serie MSP430G2x13 y MSP430G2x53 de microcontroladores de señal mixta con una función de temporizadores de 16 bits, hasta 24 pines habilitados táctiles capacitivos de Entrada / Salida, un comparador analógico versátiles, y construido en la comunicacióncapacidad de uso de la interfaz de comunicación serie universal.

Además, los miembros de la familia MSP430G2x53 tienen un convertidor analógico-a-digital de 10 bits (A / D).

Device Pinout, MSP430G2x13 and MSP430G2x53, 20-Pin Devices, TSSOP, PDIP

CPU

La CPU MSP430 tiene una arquitectura RISC de 16 bits que es altamente transparentea la aplicación. Todo operaciones, salvo las instrucciones de flujo de programa, sonrealiza como operaciones de registro en relación con el siete modos dedireccionamiento para el operando de origen y cuatro modos de direccionamientopara el operando de destino.

La CPU está integrado con 16 registros que proporcionan reducción del tiempo deejecución de la instrucción. El registro a registro tiempo de ejecución de la operaciónes un ciclo de la reloj de la CPU.

Cuatro de los registros, R0 a R3, se designan como contador de programa, punterode pila, registro de estado, y constante del generador, respectivamente. El restanteregistros son registros de propósito general.

Los periféricos se conectan a la CPU a través de los bus de datos,y buses de control,y puede ser manejado con todas las instrucciones.

El conjunto de instrucciones consiste en el original 51 instrucciones con tresformatos y siete direcciones modos y las instrucciones adicionales para laampliación.

Rango de direcciones. Cada instrucción puede operar con una palabra de 16 Bit ocon bytes de datos de 8 Bit.

Registros internos CPU del MSP430

Conjunto de instruccionesEl conjunto de registros internos consta de 16 registros de 16 bit cada uno.

Figure 3-1. CPU Block Diagram

Espacio de DireccionesEl MSP430 arquitectura von Neumann-tiene un espacio de direcciones compartido con registros de funciones especiales (SFR), periféricos, memoria RAM y memoria Flash/ROM como se muestra en la Figura 1-2.Ver los datos específicos del dispositivo en las hojas de mapas de memoria específicas.El Código de acceso se realiza siempre en direcciones pares. Los datos pueden ser

acceso como bytes o palabras.

03FFh

C000h

Contador de programa (PC) (Program Counter

El contador de programa de 16 bits (PC/R0) apunta a la siguiente instrucción a ejecutar. Cada instrucción utiliza un número par de bytes (dos, cuatro, o seis), y el PC se incrementa en consecuencia. Instrucción de accesos en el de 64 KB de espacio de direcciones se realiza en los límites de palabra, y el PC está alineado para igualar direcciones. La Figura 3-2 muestra el contador de programa.

Puntero de pila (SP)El puntero de la pila (SP/R1) es utilizada por la CPU para almacenar las direcciones de retorno de llamadas a subrutinas e interrupciones. Se utiliza un incremento del puntero de pila, antes de almacenar un dato (PUSH) y postdecremento al recuperar (POP) el dato del Stack. Además, el SP puede ser utilizado por el software con todas las instrucciones y modos de direccionamiento. La figura muestra el SP. El SP se inicializa en la memoria RAM por el usuario, y está alineado a las direcciones de pares.La figura muestra el uso de la pila.

Status Register (SR)

El registro de estado (SR/R2), que se utiliza como una fuente o registro de destino, se puede utilizar en el modo de registro sólo dirigido a las instrucciones de palabras. El resto de combinaciones de modos de direccionamiento se utilizan para apoyar la constante del generador. La figura muestra los bits de SR.

Operating Modes

El MSP430 tiene un modo activo y cinco programas seleccionables modos de bajo consumo de funcionamiento. Una interrupciónevento puede activar el dispositivo de cualquiera de los modos de bajo consumo, de servicios de la solicitud, y restaurar de nuevo a lamodo de bajo consumo en la declaración del programa de interrupción.Los seis modos de funcionamiento siguientes se pueden configurar mediante el software:

• Active mode (AM)– All clocks are active

• Low-power mode 0 (LPM0)– CPU is disabled– ACLK and SMCLK remain active, MCLK is disabled

• Low-power mode 1 (LPM1)– CPU is disabled

– ACLK and SMCLK remain active, MCLK is disabled– DCO's dc generator is disabled if DCO not used in active mode

• Low-power mode 2 (LPM2)– CPU is disabled– MCLK and SMCLK are disabled– DCO's dc generator remains enabled– ACLK remains active

• Low-power mode 3 (LPM3)– CPU is disabled– MCLK and SMCLK are disabled– DCO's dc generator is disabled– ACLK remains active

• Low-power mode 4 (LPM4)– CPU is disabled– ACLK is disabled– MCLK and SMCLK are disabled– DCO's dc generator is disabled– Crystal oscillator is stopped

Fin 1º parte

Modos de Direccionamiento

Reset del sistema e inicialización El circuito de restablecimiento del sistema se muestra en la Figura 2-1 fuentes tanto un power-on reset (POR) y un clear power-up (PUC) de la señal. Diferentes eventos desencadenan estas señales de restablecimiento y diferentes condiciones iniciales disponemos en función de cuya señal se generará.

El reinicio originado por un POR sólo es generado por los tres eventos siguientes:• Encender el dispositivo• Una señal baja en el pin RST / NMI cuando está configurado en el modo de restablecimiento• Una condición de baja cuando SVS PORON = 1.Un PUC siempre se genera cuando se genera un POR, pero una porción no es generado por un PUC. lasiguientes eventos desencadenan una PUC:• Una señal POR• expiración del temporizador Watchdog cuando sólo en el modo de vigilancia• Temporizador de vigilancia de seguridad de clave violación• Una memoria flash de seguridad clave violación• Una instrucción de CPU traiga del intervalo de direcciones periférica 0h a 01FFh.

Brownout Reset (BOR)El circuito de reposición por un apagón detecta bajos voltajes de suministro, tales como cuando una tensión de alimentación se aplica, o traído del terminal de VCC. La caída de tensión restablecer circuito se restablece el dispositivo mediante la activación de una señal POR cuando se aplica o se desconecta la alimentación. Los niveles de operación se muestran en la Figura 2-2.La señal se activa cuando POR VCC cruza el nivel VCC (start). Se mantiene activo hasta que VCC cruza la V (B_IT +) Umbral y el retardo T(BOR). El retardo T (BOR) es adaptativo es más largo cuando mas lenta es la rampa de VCC. Las histéresis Vhys(B_ IT-) asegura que la tensión de alimentación debe ser inferior V (B_IT-) para generar otra señal de PORdesde el circuito de rearme baja de voltaje.

Temporizado del

brownout

Condiciones iniciales después de un reinicio del sistemaDespués de un POR, MSP430 las condiciones iniciales son:• El pin RST / NMI está configurado en el modo de restablecimiento.• los pins de E / S se conmutan al modo de entrada como se describe en el capítulo de E / S digital.• Otros módulos periféricos y los registros se inicializan como se describe en los respectivos capítulos de estemanual.• registro de estado (SR) se pone a cero.• Los poderes temporizador de vigilancia por activos en el modo de vigilancia.• Contador de Programa (PC) se carga con dirección incluida en la ubicación vector de reset (0FFFEh). Si en el reinicio el contenido de vectores se 0FFFFh el dispositivo se desactivará para el consumo de energía mínimo.

Inicialización del SoftwareDespués de un reinicio del sistema, el software de usuario debe inicializar el MSP430 de los requisitos de la aplicación:

• Inicializar el SP, típicamente a la parte superior de RAM.• Inicializar el organismo de control a los requisitos de la aplicación.• Configurar módulos periféricos a los requisitos de la aplicación.Además, las banderas de memoria temporizador perro guardián, fallo del oscilador, y el flash se pueden evaluar para determinar el origen del reajuste.

InterrupcionesLas prioridades de interrupción son fijos y definidos por la disposición de los módulos en la cadena de conexión como se muestra en la Figura 2-3. Cuanto más cerca de un módulo es a la CPU / NMIRS, mayor es la prioridad. prioridades de interrupcióndeterminar que la interrupción se toma cuando más de una interrupción pendiente simultáneamente.Hay tres tipos de interrupciones:• Restablecimiento del sistema• (No) enmascarable NMI• Maskable

Las prioridades son mas altas cuando el evento que la origina es en la CPU.

Interrupciones (No) enmascarable (NMI)Interrupciones NMI (Non)-enmascarables no se deshabilitan por bit general (GIE) la dehabilitación de interrupción, pero es habilitado por bit de habilitación interrupciónconcreta (NMIIE, ACCVIE, OFIE).

Cuando se acepta una interrupción NMI, todo bit de habilitación de NMI es reseteadoautomáticamente. La ejecución del programa comienza en la dirección almacenada en elvector de interrupción no-enmascarable, 0FFFCh.

Software: El usuario debe configurar los requerida bits de habilitación para que lainterrupción NMI sea re-habilitado.

Una interrupción NMI (no)-enmascarable puede ser generada por tres fuentes:• Un borde en el pin RST / NMI cuando se configura en modo de NMI• Se produce un fallo del oscilador• Una violación de acceso a la memoria flash

Violación de acceso de FlashLa bandera de destello ACCVIFG se establece cuando se produce una violación de acceso flash. El acceso violación flash puede ser permitido generar una interrupción NMI activando el bit ACCVIE. La bandera ACCVIFG a continuación, se puede probar la rutina de servicio de interrupción NMI para determinar si el NMI fue causado por una violación de acceso flash.

Fallo osciladorLa señal de fallo del oscilador advierte de una posible situación de error con eloscilador de cristal. El fallo del oscilador se puede activar para generar unainterrupción NMI activando el bit OFIE. La bandera OFIFG a continuación, se puedeprobar NMI por la rutina de servicio de interrupción para determinar si el MNI fuecausada por un error de oscilador.

Una señal PUC puede provocar un fallo del oscilador, ya que la PUC cambia el LFXT1al modo de LF, por lo tanto, pagar el modo de HF. La señal PUC también sedesconecta el oscilador XT2.

Interrupción en el procesamiento

Cuando se solicita una interrupción de un periférico y permitir la interrupción periférica bits y bits GIE son establecido, se pidió a la rutina de servicio de interrupción. Sólo el bit de habilitación individual debe establecerse para (no) -interrumpe enmascarables que se solicitarán .

Aceptación de interrupción

La latencia de interrupción es de 5 ciclos ( CPUx ) o 6 ciclos ( CPU) , a partir de la aceptación de una interrupción solicitud y que dura hasta el inicio de la ejecución de la primera instrucción de la rutina de interrupción de servicio. La lógica de interrupción se ejecuta la siguiente :1 . Cualquier instrucción que se ejecuta actualmente se ha completado .2 . El PC , que apunta a la siguiente instrucción , se inserta en la pila .3 . El SR se inserta en la pila .4 . La interrupción con la prioridad más alta se selecciona si múltiples interrupciones se produjeron durante la última instrucción y se espera para el servicio.5 . La solicitud de interrupción indicador se restablece automáticamente en banderas de una sola fuente . Banderas de múltiples fuentes permanecerán controlados para el servicio por el software .6 . El SR se borra . Se pone fin a cualquier modo de bajo consumo . Debido a que el bit GIE se borra , además las interrupciones están deshabilitadas .7 . El contenido del vector de interrupción se carga en el ordenador : el programa continúa con rutina de servicio de la interrupción en esa dirección .

Retorno de la interrupción

La rutina de tratamiento de interrupción termina con la instrucción:RETI (volver de una rutina de servicio de interrupción).El regreso de la interrupción dura 5 ciclos (CPU) o 3 ciclos (CPUx) para ejecutar las siguientes acciones y se ilustra en la Figura 2-7.1. El SR con todas las configuraciones anteriores aparece en la pila. Todos los ajustes anteriores del GIE, CPUOff, etc son ahora, independientemente de los ajustes utilizados durante la rutina de servicio de interrupción.2. El PC se recupera de la pila y comienza la ejecución en la instrucción siguiente en que se interrumpió.

Jerarquización y anidamiento de las interrupciones

La anidación de las Interrupción de se activa si el bit GIE se establece a 1’ dentro de unarutina de servicio de interrupción. Cuando está habilitado la anidación, cualquierinterrupción que ocurra durante una rutina de servicio de interrupción interrumpirá larutina, independiente de las prioridades de interrupción.

Vectores de interrupciónLos vectores de interrupción y la dirección de partida se encuentran en el rango de direcciones para 0FFFFh a 0FFC0h, tal como se describe en la Tabla 2-1.

Un vector es programado por el usuario con la dirección de 16 bits de la correspondiente rutina de servicio de interrupción. Ver la hoja de datos específico del dispositivo para la lista de vectores de interrupción.Se recomienda proporcionar un vector para cada rutina de interrupción que se asigna en el módulo. Una rutina de servicio de interrupción simulada puede consistir simplemente la instrucción RETI y varios vectores de interrupción pueden apuntar a la misma.El espacio de memoria de los vectores de interrupción no asignados se pueden utilizar para el código de programa regular si es necesario.Algunos bits de habilitación del módulo, interrumpen los bits de habilitación, y las banderas de interrupción se encuentran en el SRFs. Los SFR estan situado en el rango de direcciones inferior y se implementan en formato byte.

A los SFR se debe acceder con instrucciones de byte. Ver la hoja de datos específica del dispositivo para la configuración SFR.

(1) Un restablecimiento se genera si la CPU intenta obtener instrucciones desde el registro de dirección de memoria del módulo (0h a 01FFh) o desde dentro de los rangos de direcciones no utilizadas.(2) banderas de múltiples fuentes(3) (no)-maskable: el individuo poco interrumpir a habilitar puede desactivar un evento de interrupción, pero los generales de habilitación de interrupción no puede.(4) banderas de interrupción se encuentran en el módulo.(5) En el modo SPI: UCB0RXIFG. En el modo I2C: UCALIFG, UCNACKIFG, ICSTTIFG, UCSTPIFG.(6) En el modo SPI UART o: UCB0TXIFG. En el modo I2C: UCB0RXIFG, UCB0TXIFG.(7) Esta ubicación se utiliza como clave de seguridad cargador de arranque (BSLSKEY). Un 0xAA55 en este lugar desactiva la BSL completamente. Un cero (0 h)desactiva el borrado del flash si se suministra una contraseña no válida.(8) Los vectores de interrupción en direcciones 0FFDEh a 0FFC0h no se utilizan en este dispositivo y se pueden utilizar para el código de programa regular si es necesario.

Puntero de pila (SP)El puntero de la pila (SP/R1) es utilizada por la CPU para almacenar las direcciones de retorno de llamadas a subrutinas e interrumpciones. Se utiliza un incremento del puntero de pila, antes de almacenar un dato (PUSH) y postdecremento al recuperar (POP) el dato del Stack. Además, el SP puede ser utilizado por el software con todas las instrucciones y modos de direccionamiento. La figura muestra el SP. El SP se inicializa en la memoria RAM por el usuario, y está alineado a las direcciones de pares.La figura muestra el uso de la pila.

Registros de funciones especiales (SFR)La mayoría de los bits de habilitación de interrupción y de los módulos se encuentran en el espacio de dirección más baja. Los registro de bits de funciones especiales no asignados a un propósito funcional no están físicamente presentes en el dispositivo.

Se ofrece acceso a software simple con este acuerdo.Leyenda rw: Bit puede ser leído y escrito.rw-0, 1: El bit puede ser leído y escrito. Se restablece o establecida por la PUC.rw-(0,1): El bit puede ser leído y escrito. Se restablece o establecido por POR.SFR bit no está presente en el dispositivo.

Status Register (SR)

El registro de estado (SR/R2), que se utiliza como una fuente o registro de destino,

se puede utilizar en el modo de registro sólo dirigido a las instrucciones de palabras.

El resto de combinaciones de modos de direccionamiento se utilizan para apoyar la

constante del generador. La figura muestra los bits de SR.

Generador de Constante Registros CG1 y CG2Seis constantes de uso común son generadas con el generador de constante registra R2 y R3, sin que requiere una palabra de 16 bits de código de programa adicional. Las constantes se seleccionan con el registro fuente en el modos de direccionamiento (As).

Las ventajas del generador constantes son:• No se requieren instrucciones especiales.

• No se necesita código adicional para las seis constantes

• No hay código de acceso a la memoria necesaria para recuperar la constante

El ensamblador utiliza el generador de constante automáticamente si uno de los seisconstantes se utiliza como un operando fuente en modo inmediato.

Los Registros de R2 y R3, que se utiliza en el modo constante, no pueden abordarseexplícitamente, sino que actúan sólo como registros fuente.

Generador Constant - Conjunto de instrucciones AmpliadoLa instrucción RISC conjunto de la MSP430 tiene solamente 27 instrucciones. Sin embargo, el generador de constante permite que el ensamblador del MSP430 genere 24 Instrucciones emulados adicionales. Por ejemplo, las instrucciones de un solo operando:CLR dstes emulado por la instrucción de dos operando con la misma longitud:MOV R3, dstdonde # 0 se sustituye por el ensamblador y R3 se utiliza con As = 00.INC dstse sustituye por:ADD # 1, dst

Registros de Propósito General de R4 a R15Los doce registros, R4-R15, son registros de propósito general. Todos estos registros se pueden utilizar como datosregistros, indicadores de dirección, o los valores de índice y se puede acceder a byte o palabra las instrucciones como se muestraEn la Figura 3-7.