MOSTitd Transistor an CMOS Inverter

Transcript of MOSTitd Transistor an CMOS Inverter

1

MOS T i t dMOS T i t dMOS T i t dMOS T i t d

CMOSCMOS INTEGRATED CIRCUIT DESIGN TECHNIQUESINTEGRATED CIRCUIT DESIGN TECHNIQUES

University of University of IoanninaIoannina

MOS Transistor andMOS Transistor andCMOS InverterCMOS Inverter

MOS Transistor andMOS Transistor andCMOS InverterCMOS Inverter

Survey on CMOS Digital Circuits

Dept. of Computer Science and EngineeringDept. of Computer Science and Engineering

Y. Tsiatouhas

OverviewOverview

1.1. MOS transistorMOS transistor

CMOS Integrated Circuit Design TechniquesCMOS Integrated Circuit Design Techniques

2.2. Channel modulationChannel modulation

3.3. Threshold voltageThreshold voltage

4.4. Velocity saturationVelocity saturation

5.5. CMOS inverterCMOS inverter

6.6. Noise marginsNoise margins

7.7. CMOS technology scalingCMOS technology scaling

VLSI Systemsand Computer Architecture Lab

2

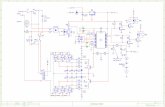

MOS TransistorMOS Transistor

MOS Transistor & CMOS Inverter 3

n+n+ n+n+

e

L

Insulator

MOSMOS‐‐FETFET ((nMOSnMOS Transistor)Transistor)

Source(S)

S

G

D

VGS=0

VDS=0

VGS=VtnVGS>Vtn

Gat

n+n+ n+n+p L

S DG

Source

GateDrain(D)

pSubstrate ‐ Bulk

W

MOS Transistor & CMOS Inverter 4

p

n+n+ n+n+

ChannelSubstrate

BulkVtn = threshold voltage

Vtn > 0 Β S

G

D

Σύμβολο

B

3

G

VGS>Vtn

nMOSnMOS Transistor Transistor –– OperationOperation (Ι)(Ι)

S

G

D

n+n+ n+n+

VDS=0

ID

0 < VDS <<

MOS Transistor & CMOS Inverter 5

p Β

nMOSnMOS Transistor Transistor –– OperationOperation ((ΙΙΙΙ))

ID

VGS = Vtn +1V

VGS = Vtn +2V

VGS = Vtn +3V

VGS = Vtn +4V

Cut‐off

MOS Transistor & CMOS Inverter 6

VDS100 (mV)

VGS Vtn

200

Linear Region

4

VGS=0VGS>Vtn

nMOSnMOS Transistor Transistor –– OperationOperation ((ΙΙΙΙΙΙ))

S

G

D

VDS =0

n+n+ n+n+

VGSVtn > VDS >>0

MOS Transistor & CMOS Inverter 7

p

Linear region: VDS VGS Vtn

Β

VGS>Vtn

nMOSnMOS Transistor Transistor –– OperationOperation (Ι(ΙVV))

S

G

D

n+n+ n+n+

VDS = VGS VtnVDS >>> VGS Vtn

VGS –Vtn

MOS Transistor & CMOS Inverter 8

p

Saturation: VDS > VGS Vtn

Pinch‐Off

Β

5

nMOSnMOS IIDD‐‐VVDSDS CharacteristicCharacteristic

IDLinear

(Resistive) Saturation RegionVtn

VGS > Vtn

RegionSaturation Region

VDS< VGSV

VDS > VGS Vtn

The channel resistance is increased and this affects the current

growth rateCurrent saturation.

An increase of VDS will almost not affect the current ID.

MOS Transistor & CMOS Inverter 9

VDSVDSsat= VGS Vtn

Linear behavior

S

G

DVGDVGSVG

C+ +

tnGCGC VVCQ

The channel charge is:

Transistor Current Estimation ITransistor Current Estimation I

p

n+n+ n+n+VS VD

CGVC

+ +

The mean potential value at the channel is :

2

VV

2

VVV DS

SDS

c

The mean gate‐channel potential difference is:

V

Long‐channel transistor, L >>

Β

MOS Transistor & CMOS Inverter 10

2

VVVVV DSGScGGS

The gate‐channel capacitance is expressed as:

WLCt

WLεεC ox

ox0oxG

εox = relative oxide permittivityε0 = vacuum permittivitytox = gate oxide thickness

ox

0oxox

t

εεC

6

Transistor Current Estimation IITransistor Current Estimation II

S

G

DVGDVGSVG

C+ +

Eμ=υ n

Under lateral electric fields, the mean velocity of the carriers at the channel is:

μ = electron mobility

p

n+n+ n+n+VS VD

CGVC

+ +

It stands:L

V=Ε DS

The drain current can be expressed as:

DSCCCC VV

VVW

CμVμQ

EμQQQ

Ι

μn = electron mobilityΕ = electric field tension

Β

MOS Transistor & CMOS Inverter 11

DStnGSoxnDSn2nD V2

VVL

CμVμL

EμLυLT

Ι

2

VVVVk

2

VVVV

L

WCμΙ

2DS

DStnGSn

2DS

DStnGSoxnD

L

WCμk oxnn

Transistor Current Estimation IIITransistor Current Estimation III

S

G

DVGDVGSVG

C+ +For VDS > VDSsat = VGS−Vtn (saturation) the channel is pinched off and the

p

n+n+ n+n+VS VD

CG+ +

Consequently, in the drain current equation the VDS is replaced by the VDSsat so that:

pdrain current does not depend on the VDS .

VC

Β

MOS Transistor & CMOS Inverter 12

2tnGSn

2tnGS

tnGStnGSnD VV2

k

2

VVVVVVkΙ

7

nMOSnMOS Transistor Current EquationsTransistor Current Equations

W

L

W

t

εμ

L

WCμk

ox

noxnn Current

gain factor

n+ n+p L

V2

DS

0 VGS – Vtn < 0 Cut‐off region

0 < V < V V

ε = εox. ε0 = oxide permittivity

MOS Transistor & CMOS Inverter 13

ID =

2

VV)VV(k DSDStnGSn

2tnGSn VV2

k

0 < VDS < VGS – Vtn

Linear region

0 < VGS – Vtn < VDS

Saturation region

nMOSnMOS IIDD‐‐VVDSDS CharacteristicCharacteristic

IDLinear Region

VDSsat= VGS ‐ Vtn

VGS = Vtn +4V

Saturation Region

VDS > VGS ‐ Vtn

V V +1V

VGS = Vtn +2V

VGS = Vtn +3V

GS tn

IG=0

ID

MOS Transistor & CMOS Inverter 14

VDS

VGS Vtn

VGS = Vtn +1V

Cut‐off Region

2DSsatnD VKi VDSVGS

IS=ID

8

nMOSnMOS IIDD‐‐VVGSGS Saturation CharacteristicSaturation Characteristic

I

SaturationV V – VID VDS VGS – Vtn

2tnGSn

D VV2

kI

MOS Transistor & CMOS Inverter 15

VGSVtn

Threshold Voltage

IIDD DependenciesDependencies

• The channel length (L)

The drain current (on current) depends on:

• The channel width (W)

• The threshold voltage (Vt)

• The gate oxide thickness (tox)

MOS Transistor & CMOS Inverter 16

• The gate oxide permittivity (ε)

• The electron/hole mobility (μ)

9

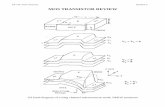

p+ p+

e

L

Insulator

pMOSpMOS TransistorTransistor

Source(S)

S

G

D

VGS= 0

VDS= 0

VGS=VtpVGS<Vtp

Gate

p+ p+n L

S DG

Source

GateDrain(D)

nSubstrate ‐ Bulk

W

VDD

MOS Transistor & CMOS Inverter 17

n

p+ p+

SubstrateBulk

Vtp = threshold voltageVtp < 0 VDD

ChannelΒ S

G

D

Σύμβολο

B

VGS<Vtp

pMOSpMOS Transistor Transistor –– OperationOperation (Ι)(Ι)

S

G

D

p+ p+

VDS= 0

ID

<<VDS < 0VDD

MOS Transistor & CMOS Inverter 18

n

VDD

Β

10

pMOSpMOS Transistor Transistor –– OperationOperation ((ΙΙΙΙ))

VGS<Vtp

S

G

D

VDS =0

p+ p+

VGSVtp < VDS <<0VDD

MOS Transistor & CMOS Inverter 19

n

Linear region: 0 > VDS > VGS Vtp

VDD

Β

VGS<Vtp

pMOSpMOS Transistor Transistor –– OperationOperation (Ι(ΙIIII))

S

G

D

p+ p+

VDS = VGS VtpVDS <<< VGS VtpVDD

MOS Transistor & CMOS Inverter 20

n

Saturation: VDS < VGS – Vtp < 0

Pinch‐OffVDD

Β

11

pMOSpMOS Transistor Current EquationsTransistor Current Equations

W

Currentgain factorL

W

t

εμ

L

WCμk

ox

poxpp

ε ε ε oxide permittivityp+ p+

nn L

V2

DS

0 VGS – Vtp > 0 Cut‐off region

0 > V > V V

It stands that: μp < μn !

ε = εox. ε0 = oxide permittivity

MOS Transistor & CMOS Inverter 21

ID =

2

VV)VV(k DSDStpGSp

2tpGSp

VV2

k

0 > VDS > VGS – Vtp

Linear region

0 > VGS – Vtp > VDS

Saturation region

pMOSpMOS IIDD‐‐VVDSDS CharacteristicCharacteristic

VDS

Cut‐off Region

2V V

Linear(Resistive) Region

Saturation Region

2DSsatnD VKI VGS Vtp

VGS = Vtp –1V

VGS = Vtp – 2V

VGS = Vtp – 3V

MOS Transistor & CMOS Inverter 22

IDVDSsat= VGS ‐ Vtp

VDS < VGS ‐ Vtp

VGS = Vtp – 4V

Vtp<0

12

Linear and Saturation RegionsLinear and Saturation Regions

VDVoltage VDVoltage

VDD

VS+Vtn

VG

Vtn

Linear

Saturation

VS

VS–|Vtp|

VG

Vtp

Linear

Saturation

VDD

Gnd

MOS Transistor & CMOS Inverter 23

nMOS pMOS

VS

Gnd

TransconductanceTransconductance

Linear RegionLinear RegionThe channel resistance (transistor ourputresistance) is given by:

1dI

IDLinear Region

S t ti R i

VGS4

)VV(k

1R)VV(k

dV

dI

tGSCtGS

0VDS

D

DS

The transconductance (gm) represents therelation between ID and VGS and it is defined asfollows:

DS

.σταθVGS

Dm Vk

dV

dIg

DS

VDS

Saturation Region

VGS0

VGS1

VGS2

VGS3

Cut‐off Region

MOS Transistor & CMOS Inverter 24

SaturationSaturation

The MOS transistor operates like a current source since the current ID is almostindependent of the voltage VDS. The transconductance is provided by:

)VV(kg tGSm

DS

13

Additional MOS Transistor DependenciesAdditional MOS Transistor Dependencies

The equations and curves presented earlier are approximations of theMOS t i t ti A d t il d l i t id thMOS transistor operation. A more detailed analysis must consider thefollowing phenomena:

• the channel‐length modulation (διαμόρφωση μήκους καναλιού )

• the body effect (φαινόμενο σώματος ) and other Vt dependencies

• the velocity saturation (κορεσμός ταχύτητας )

MOS Transistor & CMOS Inverter 25

y ( ρ μ ς χ η ς )

Channel Length ModulationChannel Length Modulation

sourcechannel

drain

L ΔLID

LinearSaturation

Saturation:

source drainVDS(κορ)

VDS

VDS

VGS

Cut‐off

–VA=–1/λ

Early Voltage

ΙD(κορ)

MOS Transistor & CMOS Inverter 26

Increasing the VDS by ΔVDS above VDS(κορ) [VDS=VDS(κορ)+ΔVDS] the channel length L isdecreased by ΔL. Since ΙD is conversely proportional of the channel length, ΙD isincreased. Consequently, in saturation stands that:

)Vλ1(VV2

kI DS

2tGSD

A /

14

The Body EffectThe Body Effect

The threshold voltage is the minimum gate‐to‐source voltage in a transistor inorder to establish an effective current ID. In general the threshold voltagedepends on:

• the gate materialg• the gate insulator (oxide) material• the oxide thickness• the channel doping concentration and• the voltage difference between the source and the bulk (VSB)

For a given gate material the threshold voltage is provided by the followingequation :

FSBF0tt φ2Vφ)2(γVV Nεq2ε

tγ Si

oxwhereBody Effect Coefficient

MOS Transistor & CMOS Inverter 27

FSBF0tt

where Vt0 is the threshold voltage for VSB=0, F is the Fermi potential ( ‐0.3V).tox is the oxide thickness, εox is the relative dielectric constant of the oxide, q isthe electron charge, εSi the relative dielectric constant of the silicon and Ν is thechannel doping concentration. The sign +/‐ refers to an nMOS / pMOS transistorrespectively.

εox

The Body EffectThe Body Effect

n+ n+ p+ n+ n+

M2

M

VSB2 > 0

The increment of VSB results inthe increment of the channeldepletion region whichchanges the transistorgeometry so that the substrate

n np

p n n

0.65

0.7

0.75

0.8

0.85

0.9

VT (

V)

Vt

MOS Transistor & CMOS Inverter 28

M1

VSB1 = 0

geometry so that the substrateturns to act as a second gateand thus the threshold voltageis increased.

Vt2 > Vt1

-2.5 -2 -1.5 -1 -0.5 00.4

0.45

0.5

0.55

0.6

VBS

(V)

V

VBS

15

Threshold Voltage DependenciesThreshold Voltage Dependencies

Vt of a long‐channel transistorVt for low VDS

Vt Vt

MOS Transistor & CMOS Inverter 29

Threshold voltage as a function of the channel length for low VDS

Drain‐induced barrier lowering (DIBL) for low L

VDSL

Mobility Degradation (Mobility Degradation (μμ))

Under the presence of high vertical electric fields (VGS/tox) the carriersff h id i f f h h bili ( ) iscatter off the oxide interface more often so that the mobility (μ) is

degraded (μeff < μ) !Thus, for a certain VGS a lower current ID is present.

MOS Transistor & CMOS Inverter 30

16

Velocity SaturationVelocity Saturation

All I‐V equations above apply under the assumption that the carriers’ velocity υ ina transistor is proportional to the electric field E, which means that the carriersmobility μ is stable. However, the velocity υp/n is saturated when the electric fieldreaches a critical level Ec, due to the scattering of the carriers in the channel.

m/s

υsat=105

stable

c, g

In short channel transistors (L<<) and under the velocity saturation influence, thecurrent is saturated earlier and at a lower value than the expected, according tothe following equation:

1V2DS

Linear region current

MOS Transistor & CMOS Inverter 31

Εc V/μm

stable velocity

stablemobility(slope=μ)

υn

Ε

)LE/V(1

1

2

VV)VV(kI

cDS

DSDStnGSnD

Velocity saturation impact

electric field

velocity

υn=μnΕ

Velocity Saturation Impact (I)Velocity Saturation Impact (I)

long‐channel transistor

ID VGS = VDDVDSAT < VGS – Vt

ΙDSAT(vs) < IDSATΙDSAT)

short‐channel transistor

VDSVDSAT VGS – Vt

pen

den

ce

‐4

1.5

2

2.5x 10

VGS= 2.5 V

VGS= 2.0 V

(A)

ID short‐channel transistor

ΙDSAT(vs)

The W/L ratio and the VGS of the two transistors are the same in both cases

MOS Transistor & CMOS Inverter 32

Linear Dep

(V)0 0.5 1 1.5 2 2.50

0.5

1VGS= 1.5 V

VGS= 1.0 V

VDS

LEV cDSAT

17

Velocity Saturation Impact Velocity Saturation Impact (Ι(ΙII))

5

6x 10

-4

2

2.5x 10

-4

linear

0

1

2

3

4

0

0.5

1

1.5

I D(A)

I D(A) quadratic

dependence

quadratic dependence

linear dependence

MOS Transistor & CMOS Inverter 33

0 0.5 1 1.5 2 2.50

0 0.5 1 1.5 2 2.50

Long‐channel transistor Short‐channel transistor

VGS (V)VGS (V)

Impact of velocity saturation on short‐channel transistors: Increasing the VDS voltage the drain current IDreaches the saturation earlier than the expected level (VGSVt) and ID has a linear dependence on the VGS

voltage.

Velocity Saturation Impact (III)Velocity Saturation Impact (III)The W/L ratio of the two transistors is the same in both cases.

‐4

2.5x 10

VGS= 2.5 V

m V

GS

5

6x 10

‐4

VGS= 2.5 V

Τρίοδος om V

GS

0

0.5

1

1.5

2

VGS= 2.0 V

VGS= 1.5 V

VGS= 1.0 V

I D(A)

Linear dep

enden

ce from

1

2

3

4

5

VGS= 2.0 V

VGS= 1.5 V

VGS= 1.0 V

ΤρίοδοςΚόρος

VDS = VGS – Vt

I D(A)

Quadratic dep

enden

ce fro

MOS Transistor & CMOS Inverter 34

0 0.5 1 1.5 2 2.50

VDS (V)

0 0.5 1 1.5 2 2.50

VDS (V)

Long‐channel transistor Short‐channel transistor

2tnGSD VV2

kI αtnGSD VV

2

kI

1 < α < 2

saturation

18

Weak Inversion CurrentWeak Inversion Current

10-2

Linearregion

)Vλ1(e1eII DSq/kT

V

q/nkT

VV

Soff

DStGS

10-10

10-8

10-6

10-4

Exponential

Quadraticregion

I D(A)

IS and n are empirical parameters, with n1

Slope factor:

)10ln(q

kTnS

Ioff

MOS Transistor & CMOS Inverter 35

0 0.5 1 1.5 2 2.510

-12

10

Vt

region

VGS (V)

expresses the reduction rate (that is therequired reduction of VGS in order toreduce ID by 10).

For n=1.5 the slop factor is : S=90mV/decade

Additional PhenomenaAdditional Phenomena•Mobility Variation

The mobility (μ) of the carriers (electrons/holes) is decreased by increasing the doping concentrationand/or the temperature.

• Fowler‐Nordheim and Direct Tunnelling

For thin gate oxides in modern nanotechnologies a current is present through this insulator ThisFor thin gate oxides in modern nanotechnologies a current is present through this insulator. Thiscurrent is due to quantum‐mechanics tunneling phenomena and is proportional to the gate surfacearea.

• Hot Electrons

As the channel length (L) decreases the drain electric field increases so that the electrons gain enoughenergy (hot electrons) as they move in the channel to deflect towards the gate under the influence ofthe gate potential.

• Substrate Breakdown

For short channels (L) and high drain voltages the depletion area of the drain expands towards the

MOS Transistor & CMOS Inverter 36

For short channels (L) and high drain voltages, the depletion area of the drain expands towards thesource so that a drain‐to‐source current is established which is independent of the gate voltage. Thisphenomenon does not result in a permanent transistor failure.

• Gate Oxide Dielectric BreakdownFor high gate‐to‐source voltages the gate oxide may breakdown. This will lead to a permanenttransistor failure.

19

CMOS InverterCMOS Inverter

MOS Transistor & CMOS Inverter 37

InputInput‐‐Output Characteristic Curve Output Characteristic Curve (I)(I)

Vout IDn = IDp

Input‐Output (Static) Characteristic Curve [Vout=f(Vin)]

VDD

A B

C

VDD

VDD / 2

Vin Vout

MOS Transistor & CMOS Inverter 38

Vin

DE

VDD+VtpVtn VDD / 2 VDD0Gnd

in out

20

At the C region bothtransistors are in saturationand behave as current

InputInput‐‐Output Characteristic Curve Output Characteristic Curve (II)(II)

A BVDD

VDD+Vtpand behave as currentsources.

There is an input voltage levelfor which it stands Vin=Voutand it is called transitionthreshold (κατώφλιμετάβασης) VΜ of the logicgate.

Vout C

DE

DD

VDD / 2

pMOSpMOS ‐‐ LinearLinear

nMOSnMOS ‐‐ LinearLinear

pMOSpMOS ‐‐ SaturationSaturation

nMOSnMOS ‐‐ SaturationSaturation

pMOS

pMOS––Cut

Cut‐‐off

off

nMOS

nMOS––Cut

Cut‐‐off

off

Vin‐Vtn

Vin‐Vtp

MOS Transistor & CMOS Inverter 39

At this voltage the wholesystem is not stable.

(In the figure, the transitionthreshold is equal to VDD/2given that kp=kn ).

Vin

VDD+VtpVtn VDD / 2 VDD0

Vtp<0

Vout

A BVDD

pMOSpMOS ‐‐ SaturationSaturation

VDD+Vtp At the C region both transistorsare in saturation. In addition,both transistor currents are equaland for Vin=VM it stands:

The Transition ThresholdThe Transition Threshold

C

DE

VDD+VtpVtn VΜ VDD

VΜ

0

pMOSpMOS ‐‐ SaturationSaturation

nMOSnMOS ‐‐ saturationsaturation

in M

2tpDDM

p2tnM

n )VVV(2

k)VV(

2

k

2tnM

2tpDDM

p

n

)VV(

)VVV(

k

k

Wεμ /

MOS Transistor & CMOS Inverter 40

Vin

2tnM

2tpDDM

n

p

p

n

)VV(

)VVV(

μ

μ

W

W

In case that a specific transition threshold VM

is required, then the appropriate transistorwidth ratio is given by the next equation:

Ln = Lp

L

W

t

εμk

ox

n/pn/p

21

kknn//kkpp Effect on the InputEffect on the Input‐‐Output Curve Output Curve

Vout1

)VVV(k2

tpDDMn

L

W

t

εμk

n/pn/p

VDD

VDD / 2

1k

kn

1.0k

k

p

n

10k

k

p

n

Vtn Vtp

1)VV(k

2

VV

2tnM

p

p

n

DDM

MOS Transistor & CMOS Inverter 41

Ltox/p

VinVDD+VtpVtn VDD / 2 VDD0

kpkp

Noise MarginsNoise Margins

VDDOutput

VOHmin

VIHmin

VILmax

InputLogic 1

Tolerance

OutputLogic 1

Tolerance

InputSwing

OutputSwingNoise

Margins

NMH

NMH=VOHmin – VIHmin

NML=VILmax – VOLmax

MOS Transistor & CMOS Inverter 42

Gnd

ILmax

VOLmaxInputLogic 0

Tolerance

OutputLogic 0

Tolerance

NML

22

VDD

1dV

dV

in

out

Noise Margins (II)Noise Margins (II)

Vout VM

VOL

VOH

gdV

dV

in

out

g

)VV(VV OLOHILIH

MOS Transistor & CMOS Inverter 43

Vin

VIHVIL VM VDD0

Noise Margins (III)Noise Margins (III)

ILin VV

2/12tpinpnDDtpDDin

2tpintpin

in

out 1VVk/kVV2/VV2VVVVdV

dV

Vout

VDD

VM

VOH1

dV

dV

in

out 1k/k

tntpDD

IL

pn

8

V5V3V3V

0VILLOL

VNM

MOS Transistor & CMOS Inverter 44

Vin

VIHVIL VM VDD0

VOLD

23

Noise Margins (IV)Noise Margins (IV)

ttDD V3V5V5

Vout

VDD

VM

VOH1

dV

dV

in

out

1k/k

tntpDD

IH

pn

8

V3V5V5V

B

VVIHDDHDDOH

VVNM

MOS Transistor & CMOS Inverter 45

Vin

VIHVIL VM VDD0

VOL

1k/k

tntpDD

H

pn

8

V3V5V3NM

Noise Margins (V)Noise Margins (V)

NMHs

NM

Noise M

argins

Vtn = |Vtp|

Considering that:

MOS Transistor & CMOS Inverter 46

1 2 3 4 5 6 7 8

NML

kn / kp

24

The The CMOSCMOS InverterInverter

VDDVin

n+ n+

p‐substratep+p+ p+n+

n‐well

Gnd

DD in

Vout

MOS Transistor & CMOS Inverter 47

LatchLatch‐‐UpUp

VDDVin

n+ n+

pp+p+ p+n+

n

Gnd

DD

npn

in

Vout

MOS Transistor & CMOS Inverter 48

npn

pnp

25

CMOS Technology ScalingCMOS Technology Scaling

MOS Transistor & CMOS Inverter 49

Process VariationsProcess Variations

Transistor manufacturing is characterized by process variations either at the wafer levelor the die level. Process variations are random and uncorrelated and lead to variationsof transistor parameters and geometric characteristics like the W/L ratio, the oxidehi k h d i i h diff i d h h l id h hi hthickness, the doping concentration, the diffusion depth, the metal widths e.t.c. whichresult to variations on the transistor transconductance, threshold voltage, parasiticcapacitance and resistance …

Consequently, process variations affect the expected circuit performance (speed, powerconsumption, reliability). Aiming to alleviate the situation, the fabs provide “fast” and“slow” models as well as statistical models of the devices for corner and Monte‐Carloanalysis respectively.

MOS Transistor & CMOS Inverter 50

26

Process VariationsProcess Variations

MOS Transistor & CMOS Inverter 51

MOS MOS Transistor Size ScalingTransistor Size Scaling

tox/αVDD/α

p+ p+

n L/α

W/α

Χ/ααN

Electric Field: 1

Parameter ScalingFactor

Power‐Speed Product: 1/α3

Parameter ScalingFactor

MOS Transistor & CMOS Inverter 52

Electric Field:Depletion Layer:Parasitic Capacitance:Gate Delay:DC Power Dissipation:Dynamic Power Dissipation:

11/α1/α1/α1/α2

1/α2

Power‐Speed Product:Gate Area:Power Density:Current Density:Transconductance:

1/α1/α2

1α1

27

YieldYield

chipsofnumbertotall

wafer_on_chips_good_of#Y

c ps_o_u be_tota

DAeY

2DA

DA

e1Y

Seed Model:

Murphy Model:

A >> & Y<30%

A << & Y>30%

MOS Transistor & CMOS Inverter 53

where: Α = die areaD = defect density (defects/cm2)

BibliographyBibliography

• “Digital Integrated Circuits,” J. Rabaey, A. Chandrakasan and B. Nikolic, Prentice Hall,2003.

• “CMOS VLSI Design: A Circuits and Systems Perspective,” N. Weste and D. HarrisAddison Wesley, 2010.

MOS Transistor & CMOS Inverter 54