Modeling All-MOS Log-Domain A/D Converterspserra/cnm/2004 - Modeling All-MOS Log... · Input...

Transcript of Modeling All-MOS Log-Domain A/D Converterspserra/cnm/2004 - Modeling All-MOS Log... · Input...

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 1/22

Modeling All-MOS Log-DomainΣ∆ A/D Converters

X.Redondo1, J.Pallarès2 and F.Serra-Graells1

1Institut de Microelectrònica de Barcelona (CNM - CSIC)2Barcelona International R&D Core (Epson Europe Electronics GmbH - CNM)

25th November 2004

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 2/22

1 Introduction

2 Low-Voltage All-MOS Circuits

3 Modeling Circuit Non-Idealities

4 Design Example

5 Conclusions

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 3/22

1 Introduction

2 Low-Voltage All-MOS Circuits

3 Modeling Circuit Non-Idealities

4 Design Example

5 Conclusions

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 4/22

Σ∆ Modulator Architecture

bout

Idac

I1 IL

s1

¿1

+

M

1s1

¿k

+ 1s1

¿L

+ 1

Iin Ik

DAC

Quantizer

Ihigh

Ilow

N=1

H

Quantizer

DAC

AntialiasingFilter

yin boutysource

§¢ Modulator

Analog Digital

Limiter Decimator

ylim

dIk

dt=

1

τk(Ik−1 − Idac)

CMOS Log Domain

✔ Very low-voltage

✔ Low-power

✔ MOS-only

Simulation Issues

✖ High-accuracy

✖ Continuous-time

✖ Oversampling

✖ Pseudo-periodic

. . . need for high-level (but device-based) analytical modeling!

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 5/22

1 Introduction

2 Low-Voltage All-MOS Circuits

3 Modeling Circuit Non-Idealities

4 Design Example

5 Conclusions

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 6/22

CMOS Log-Domain Processing

bout

Vdac

V1 VL

s1

G1

+Iin

Ihigh

Ilow

Vin

C1

1F

Vk

s1

Gk

+

Ck

1s1

GL

+

CL

1

F

F

bout

Idac

I1 IL

s1

¿1

+

M

1s1

¿k

+ 1s1

¿L

+ 1

Iin Ik

DAC

Quantizer

Ihigh

Ilow

N=1

Weak inversion and forward saturation:

ID = ISeVGB−VT O

nUt e−VSBUt

IS = 2nβ(

WL

)U2

t IC = ID

IS

Input Compressor

IinK 1

Iref

K

VinVref

Iref

I = F (V ) = IrefeV−Vref

nUt I > 0

Class-A operation: |Iin| < Iref

Vin = Vref + nUt ln

(Iin

Iref+ 1

)

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 7/22

Differential Integrator

dIk

dt=

1

τk(Ik−1 − Idac)

dVk

dt=

nUt

τke

Vk−1−VknUt − nUt

τke

Vdac−VknUt

dQk

dt︸︷︷︸Ck

dVkdt

= Itunk︸ ︷︷ ︸nUtCk

τk

e−VknUt

(e

Vk−1nUt − e

VdacnUt

)

Vk

Vdac Ck

Itunk

Icapk

Vk-1

Quantizer and Built-in DAC

Vref

DQ

bout

bclkbclkbclk

VL

bout =

{1 VL > Vref

0 VL ≤ Vref

bout

Vk

Vref Ck

Itunk

Icapk

Vk-1

1 KlowKhigh

Vdac = Vref + nUt ln(

Ihighbout+Ilow b̄out

Iref

)X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 8/22

1 Introduction

2 Low-Voltage All-MOS Circuits

3 Modeling Circuit Non-Idealities

4 Design Example

5 Conclusions

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 9/22

Thermal Noise

I PSD in Class-A:

di2Dn

df= 4KT

gms

2≡ 2qID

I Input compressor:

dv2inn

df' 4q

(nUt)2

Iref

I Integrator+DAC:

di2capkn

df' 2q(2+Klow+boutKhigh)Itunk

Klow =Ilow

Itunk

Khigh =Ihigh − Ilow

Itunk

≡Ifull

Itunk

I Block contributions:

SNR ∝ +3dB/oct(Iref )

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 10/22

Moderate Inversion

I Degradation of the ex:

ID = IS ln2(1 + e

VGB−VT O2nUt e−

VSB2Ut

)I Input compressor:

Vin = Vref+nUt ln

e

rIin+Iref

IS − 1

e

rIrefIS − 1

2

I Integrator+DAC:

Icapk = IS ln2

[1 + e

Vk−1−Vk2nUt

(e

qItunk

IS − 1

)]−IS ln2

[1 + e

Vdac−Vk2nUt

(e

qItunk

IS − 1

)]

I Inversion coefficient dependence:

SDR ⇐ IC =ID

IS

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 11/22

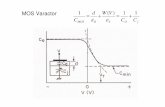

MOS Capacitors

I Non-linear capacitors:

dQk

dt=

(Ck +

dCk

dVkVk

)dVk

dt

I NMOS capacitance:

Ck ' Coxk

(1− Ut

Vk − VTO

)I Integrator ODE:

dVk

dt=

Itunk

Coxk

e−VknUt

1 + VT OUt

(Vk−VT O)2

(e

Vk−1nUt − e

VdacnUt

)

I Strong inversion asymptote:

( - )/Vk V UtTO

-20 -15 -10 -5 0 5 10 15 200

0.2

0.4

0.6

0.8

1

CC

koxk

/

weakinversion

moderateinversion

stronginversion

Vk

Ck

EKV

SDR ⇐ Vref − VTO

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 12/22

MOS Capacitors

I Non-linear capacitors:

dQk

dt=

(Ck +

dCk

dVkVk

)dVk

dt

I NMOS capacitance:

Ck ' Coxk

(1− Ut

Vk − VTO

)I Integrator ODE:

dVk

dt=

Itunk

Coxk

e−VknUt

1 + VT OUt

(Vk−VT O)2

(e

Vk−1nUt − e

VdacnUt

)

I OP dependence (VTON'0.5V):

SDR ⇐ Vref − VTO

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 13/22

DAC Waveform Asymmetry

1 0 1 0 1 1 0 0

Ihigh

Ilow

Ihigh

Ilow

Irtz

Ioff

Ioff -Iamp

Ioff +Iamp

✖ WA signaldependencies

⇓In-bandnoiseinjection!

✔ Return-to-zero (Irtz)techniques

Equivalent model: input offset (Ioff ) + full-scale reduction (Iamp)

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 14/22

Block Models (e.g. Simulink)

Vnoise

Vin

n*Ut

Class-A

1/Is

Iref

F (u)-1

Iin

Technology mismatching

Voffsetbout

S/H

(sgn(u-Vref)+1)/2

QuantizerVcap

Input compressor Quantizer

Inoise for bout=1 bout=0

VinpVinnVcap

Icap

transconductance

1s

integration

MOS cap

bout

Vinn

Vinp

Qcap

Cmos(Vcap)

VcapVcap

Vdac

n*Ut

n*Ut

Switch1

1/Is

1/Is

Ioff

Iamp

bout

F (u)-1

F (u)-1

Integrator DAC (common to optimize simulation speed)

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 15/22

1 Introduction

2 Low-Voltage All-MOS Circuits

3 Modeling Circuit Non-Idealities

4 Design Example

5 Conclusions

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 16/22

ArchitectureA 4th-order 64× 1bit single-loop Σ∆ modulator:

SpecificationsInput full-scale 6µApp

Bandwidth 100Hz-8KHzSampling frequency 1.024MHz

RTZ period 10%-50% programmableBiasing Iref=7µA and Vref=0.7VTuning Itunk={7,1,1,1}µA and Coxk={210,30,12,12}×5pFSupply VDD=1.2V and PD'160µW

Technology 0.35µm CMOS digital VTON+|VTOP |'1.2V

Vcap bout

quantizerVinp

Vinn

bout

Vcap

integrator4Vinp

Vinn

bout

Vcap

integrator3Vinp

Vinn

bout

Vcap

integrator2Vinp

Vin

bout

Vcap

integrator1

Iin Vin

compressor

bout

boutVdac

DAC RTZ

Ain, fin

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 17/22

Design Process

fast high-level model⇓

optimal circuit parameters

Functional vs Electrical

SPICE validation

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 18/22

Performance Estimations

Simulation:

electrical18 weeks

↓functional

1 hour

÷3000!DR=74dB(12b) and SNDRmax=62dB at -4dBµArms

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 19/22

Final Design

100 m¹

Total area: 650µm×1130µm=0.73mm2 . . . to be integrated soon!

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 20/22

Final Design

100 m¹Reference Quantizer+S/H

NMOS capacitor arraySwitching

Biasing Translinear loops

Dummies

DACs

Total area: 650µm×1130µm=0.73mm2 . . . to be integrated soon!

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 21/22

1 Introduction

2 Low-Voltage All-MOS Circuits

3 Modeling Circuit Non-Idealities

4 Design Example

5 Conclusions

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

DCIS’04 Modeling All-MOS Log Σ∆ ADCs Intro Circuits Modeling Example Conclusions 22/22

Main Results

I Accurate high-level modeling of log-domain CMOS Σ∆ ADCs.

I Analytical circuit study + advanced MOSFET models.

I Simulation speed improved by more than 1000 times.

I Independent evaluation of each non-ideality or block effect.

I ADC complete performance estimations can be iterated.

I Example for a 4th-order 64× 1bit single-loop Σ∆ modulator.

X.Redondo, J.Pallarès and F.Serra-Graells IMB-BIRD

![b,d) 1 arXiv:1007.2378v1 [hep-ph] 14 Jul 2010 · 2018. 10. 29. · arXiv:1007.2378v1 [hep-ph] 14 Jul 2010 Ref. SISSA 36/2010/EP Ref. TUM-HEP 763/10 Ref. IPPP/10/42, DCTP/10/84 TeVScaleSee-Saw](https://static.fdocument.org/doc/165x107/60ac6dec85c9d80e5a0c5430/bd-1-arxiv10072378v1-hep-ph-14-jul-2010-2018-10-29-arxiv10072378v1.jpg)

![LIAISON QuantiFERON-TB Gold Plus ( [REF] 311010) 1 ...](https://static.fdocument.org/doc/165x107/61b26a9e529835162559e41c/liaison-quantiferon-tb-gold-plus-ref-311010-1-.jpg)