Microcontroladores de arquitectura X51

-

Upload

adrian-castaneda -

Category

Education

-

view

552 -

download

3

description

Transcript of Microcontroladores de arquitectura X51

Arquitectura de la Familia x51

Dr. Adrián Castañeda Galván 1

Aplicación de los μCLa aplicaciones de los microcontroladores, caen en una de dos categorías: Sistemas de Control de Lazo Abierto o Sistemas de Control de Lazo Cerrado; aunque también pueden encontrarse en aplicaciones de manipulación de estructura de datos, por ejemplo, en sistemas de robótica, o en sistemas de comunicación.

Dr. Adrián Castañeda Galván 2

Dr. Adrián Castañeda Galván 3

Características del μC x52 Capacidad de proceso de palabra de 8 bits Procesador Booleano. Circuito de reloj incorporado. Frecuencia hasta 24 MHz. 4 Puertos de 8 bits, 32 Líneas de entrada y salida. 8KB de ROM 4KB para el x51 256 Bytes de RAM 384 contando el SFR. Capacidad de expandirse como μP con 64KB de ROM y RAM. 1 UART FULL DUPLEX. 3 Timers de 16 bits. 2 para el x51 2 Interrupciones Externas. 6 Fuentes de interrupciones con niveles de prioridad. 255 Instrucciones Diferentes. Alta Inmunidad al ruido eléctrico.

Dr. Adrián Castañeda Galván 4

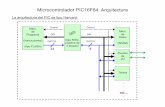

Organización de la máquina

Dr. Adrián Castañeda Galván 5

CONTROLDE

INTERRUPCION

8K

ROMTIMER0, 1

TIMER 2

CPU

OSCBUS DE

CONTROL

PUERTO

SERIAL

256 BYTES

RAM

4 PUERTOS

DE I / O

P0 P1 P2 P3P0/P1DIRECCIONES/DATOS

TXD RXD

Int. externas

Cont.

ext

Dr. Adrián Castañeda Galván 6

Dr. Adrián Castañeda Galván 7

Descripción de los pines Los puertos P0 a P3 son bidireccionales y tienen funciones alternas que se muestra en la figura. El P0 necesita resistencias de PULL UP dado que es de colector abierto.

RST: una entrada alta durante 2 ciclos de reloj detiene la máquina.

ALE: Address Latch Enable. Un pulso positivo de salida permite fijar el byte bajo de la dirección durante el acceso a una memoria externa. En operación normal, ALE es emitido en un rango constante de 1/6 de la frecuencia del oscilador, y puede ser usada para cronometrar.

Dr. Adrián Castañeda Galván 8

Descripción de los pines PSEN: Program Store Enable. habilitador de lectura para memoria de programas externos. (OEROM)

RD: read para leer de la memoria de datos externa.(OERAM)

WR: write para escribir en la memoria de datos externa.(WRRAM)

EA:External Access Enable. EA debe mantenerse externamente en posición baja para habilitar el mecanismo que elige el código de las localizaciones de la memoria de programas externos, 0000H y 0FFFH. Si EA se mantiene en posición alta, el dispositivo ejecuta los programas que se encuentran en la memoria interna ROM, a menos que el contador del programa contenga una dirección mayor a 0FFFH.

Dr. Adrián Castañeda Galván 9

Descripción de los pines

Dr. Adrián Castañeda Galván 10

Estructura del reloj

Dr. Adrián Castañeda Galván 11

Ciclo máquina Un ciclo máquina para esta familia de microcontroladores, consiste en una secuencia de 6 estados nombrados S1 a S6. Cada estado esta formado por dos periodos de la señal de reloj denominadas fases (F1 y F2).

Teniendo en cuenta que cada ciclo tienen 12 periodos, si el oscilador es de 12 MHz, la duración del ciclo máquina es de 1μs.

La secuencia de búsqueda/ejecución son las mismas, sea la memoria de programas interna o externa.

Dr. Adrián Castañeda Galván 12

Dr. Adrián Castañeda Galván 13

Organización de la memoria ROM

Dr. Adrián Castañeda Galván 14

Vector de interrupciones

Dr. Adrián Castañeda Galván 15

Interrupción DirecciónRESET 0000H

IE0 0003HTF0 000BHIE1 0013HTF1 001BH

RX Y TX 0023HTF2 Y EXF2 002BH

Organización de la memoria RAM

Dr. Adrián Castañeda Galván 16

La memoria de datos se divide en 2

•Ram Interna

•Ram Externa

La Ram Externa se accesapor la instrucción MOVX.

La Ram Interna se divide en 3 según su modo de direccionamiento

Directo e Indirecto

Solo DirectoSolo Indirecto

Memoria de Datos. SFR

Dr. Adrián Castañeda Galván 1780

P1

87TCON TMOD TL0 TL1 TH0 TH1

SCON SBUFP2IEP3IP

PSW

ACC

B

889098A0A8B0B8C0C8D0D8E0E8F0F8 FF

F7EFE7DFD7CFC7BFB7

9F978F

AFA7

P0 SP DPL DPH PCON

T2CON RCAP2L RCAP2H TL2 TH2

Memoria de Datos. Área de Direccionamiento Directo e Indirecto bancos de registros( 00H –1FH )

Bit a Bit ( 20H –2FH ) son 128 bits

Scratch PAD ( 30H – 7FH ). Block de notas de rápido acceso

Dr. Adrián Castañeda Galván 18

7FH

2FH

1FH

17H

0FH

07H

20H

18H

10H

08H

0

11

10

01

00

{{{{ Valor de reset

del Stack Pointer 07

4 bancos de 8

registros

R0- R7

Espacio direccionableBit a bit

Área de Scratch PAD30H

Dr. Adrián Castañeda Galván 19

MODOS DE DIRECCIONAMIENTO a) DIRECCIONAMIENTO INMEDIATO b) DIRECCIONAMIENTO DIRECTO c) DIRECCIONAMIENTO INDIRECTO e) DIRECCIONAMIENTO POR REGISTRO d) DIRECCIONAMIENTO INDEXADO f) DIRECCIONAMIENTO POR BIT

Dr. Adrián Castañeda Galván 20

Dr. Adrián Castañeda Galván 21

Dr. Adrián Castañeda Galván 22

Dr. Adrián Castañeda Galván 23

DIRECCIONAMIENTO INDEXADO

Dr. Adrián Castañeda Galván 24

Este direccionamiento solo es posible en la memoria de programas y sólo permite la lectura. Es utilizado para la lectura de tablas. Un registro de 16 bits como el DPTR o el contador de programa PC apunta a la base y el acumulador es el OFFSET

MOVC A, @A+DPTRMOVC A, @A+PC

Dr. Adrián Castañeda Galván 25

Dr. Adrián Castañeda Galván 26

De los Mcsx51

Dr. Adrián Castañeda Galván27

Registro Program Status Word

Dr. Adrián Castañeda Galván 28

Selección del Banco de Registros en PSW

Rs1 Rs0 Banco Dirección

0 0 0 00H-07H

0 1 1 08H-0FH

1 0 2 10H-17H

1 1 3 18H-1FH

Dr. Adrián Castañeda Galván 29

Registro Power Control

Dr. Adrián Castañeda Galván 30

Interrupciones

Dr. Adrián Castañeda Galván 31

TCON Registro de control de temporizadores, contadores e interrupciones

Dr. Adrián Castañeda Galván 32

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

B BIT FUNCIONTF1 TCON.7 Bandera de Desborde del T1 TR1 TCON.6 Arranque del T1TF0 TCON.5 Bandera de Desborde del T0TR0 TCON.4 Arranque del T0IE1 TCON.3 Bandera de petición de interrupción 1IT1 TCON.2 Control de interrupción 1=Flanco

Negativo 0=Nivel bajoIE0 TCON.1 Bandera de petición de interrupción 0IT0 TCON.0 Control de interrupción 1=Flanco

Negativo 0=Nivel bajo

Interrupción externa

Dr. Adrián Castañeda Galván 33

Pin 3.2 y 3.3

Por flanco

Por nivel

ts=tiempo de servicio de subrutina

ts ts

ts ts ts ts ts

TCON Registro de control de temporizadores, contadores e interrupciones

Dr. Adrián Castañeda Galván 34

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

B BIT FUNCIONTF1 TCON.7 Bandera de Desborde del T1 TR1 TCON.6 Arranque del T1TF0 TCON.5 Bandera de Desborde del T0TR0 TCON.4 Arranque del T0IE1 TCON.3 Bandera de petición de interrupción 1IT1 TCON.2 Control de interrupción 1=Flanco

Negativo 0=Nivel bajoIE0 TCON.1 Bandera de petición de interrupción 1IT0 TCON.0 Control de interrupción 1=Flanco

Negativo 0=Nivel bajo

TMOD Registro de control de modo de Timers y Contadores

Si Gate=1 y TR=1 el C/T funciona sí la línea de INT está en alto (control por hardware).

Si Gate=0 el C/T funciona solo si TR=1 (C.S). C/T Selecciona el Contador o Temporizador.

M1 M0 Modos de Operación. 0 0 Modo 0 Timer de 13 bits 0 1 Modo 1 Timer de 16bits 1 0 Modo 2 Recargable de 8 bits 1 1 Modo 3 TL0 como contador

o temporizador TH0 solo como temporizador

Dr. Adrián Castañeda Galván 35

GATE C/T M1 M0 GATE C/T M1 M0

TIMER1 TIMER 0

Timer1 en MODO 0. Contador de 13 bits. MODO 1 16 bits

Dr. Adrián Castañeda Galván 36

Timer1 en MODO 2. 8 Bits Auto recarga

Dr. Adrián Castañeda Galván 37

Timers en MODO 3

Dr. Adrián Castañeda Galván 38

Registro SCON para comunicación serie.(MSB) (LSB)

SM0 SM1 SM2 REN TB8 RB8 TI RISímbolo Nombre y SignificadoSM0 – SM1 Determinan el modo de operación del puerto serie

SM2 En modos 2 y 3, si SM2=1, RI no se activa si RB8 no es cero.En modo 1, si SM2=1, RI no se activa si no se recibe el bit

stop.En modo 0 debe estar en 0.

REN Cuando = “1” permite la recepción.

TB8 Es el noveno bit a transmitir (bit de paridad en Modo 2 y 3)

RB8 En modos 2 y 3 es el noveno bit que se recibeEn modo 1, si SM2=0 es el bit de stopEn modo 0 no se utiliza

TI Bandera de Interrupción de Transmisión. Debe borrarse por programa

RI Bandera de Interrupción de Recepción. Debe borrarse por programa

Dr. Adrián Castañeda Galván 39

Modos de operación del puerto serieMODO 0: Los datos entran y salen por el pin RXD. El pin TXD presenta los impulsos de desplazamiento del reloj. El tamaño de palabra es de 8 bits siendo el primero en salir o llegar el LSB. La frecuencia es 1/12 la frecuencia del reloj.MODO 1: es la comunicación estándar 1 bit de start 8 de datos y 1 de stop. Los 10 bits son transmitidos por TXD y recibidos por RXD. La velocidad de trasmisión es ajustada por el usuario.

MODO 2: Se transmiten (TxD) o se reciben (RxD) 11 bits, un bit de inicio (strat=0) 8 bits de datos (primero D0), el 9 bit es TB8 en la transmisión y RB8 en la recepción un bit de paro (Stop=1). En recepción el bit de paro (STOP) se va a RB8 si SM2=0 de SCON, el baud rate es fijo al 1/32 o 1/64 de la frecuencia de reloj.MODO 3: Se transmiten (TxD) o se reciben (RxD) 11 bits, semejante al modo 2 excepto que la velocidad de transmisión (baud rate) es variable.

Dr. Adrián Castañeda Galván 40

Generación del Baud Rate

Dr. Adrián Castañeda Galván 41

En modo 1 y 3 :Baud rate =

K x Frecuencia de reloj

32 x 12 x [256 - TH1]

donde K = 1 si SMOD = 0K = 2 si SMOD = 1

En modo 2 :1 / 64 si SMOD = 0

1 / 32 si SMOD = 1

Baud Rates Comunmente usados

Dr. Adrián Castañeda Galván 42

Resumen de losRegistros de control

Interrupción externa Registros

IE (EA, EXx) IP (PXx) TCON ( ITx, IEx)

Puertos P3.2 y P3.3

Timer/Counter Registros

IE (EA,ETx) IP (PTx) TCON ( TRx,TFx) TMOD (Gate, C/T, M1, M0)

P3.4 y P3.5 Serial

Registros PCON (SMOD) SCON (TI, RI, SMx, REN)

Timer 1 en modo 2 TH1 valor dependiente de Baud Rate

Dr. Adrián Castañeda Galván 43

Sintaxis del ensamblador

Dr. Adrián Castañeda Galván 44

Tipos de instrucciones Instrucciones booleanas Instrucciones aritméticas Instrucciones lógicas Instrucciones de transferencia de datos Instrucciones de salto.

Dr. Adrián Castañeda Galván 45

Sintaxis del Ensamblador

Dr. Adrián Castañeda Galván 46

< etiqueta :> <mnemónico> <operandos> <;comentarios>

Salto: CJNE A,#5H,Regreso ;este es un comentario

Como MicroprocesadorComo Microcontrolador

Dr. Adrián Castañeda Galván 47

Configuración como μP. Memoria de programa Rom Externa.

Dr. Adrián Castañeda Galván 48

PSEN - Program Store EnableALE - Address Latch Enable

Lectura de memoria de programa externa

Dr. Adrián Castañeda Galván 49

ALE

PSEN

P0

P2A8 - A15 A8 - A15

A0-A7 DATOS A0-A7

Configuración para lectura de datos externa.

Dr. Adrián Castañeda Galván 50

Lectura de memoria de datos externa

Dr. Adrián Castañeda Galván 51

PSEN

RD

P0

P2

A0-A7

P2.0 - P2.7 o A8 - A15 A8 - A15

A0 - A7Datos

Escritura en memoria de datos externa

Dr. Adrián Castañeda Galván 52

ALE

PSEN

WR

P0

P2P2.0 - P2.7 o A8 - A15 A8 - A15

A0-A7DATOS A0-A7

Configuración como μP

Dr. Adrián Castañeda Galván 53

Dr. Adrián Castañeda Galván 54