Lec_23 Effect of Substrate Bias VB and Channel Bias VC

-

Upload

maxxtorr723 -

Category

Documents

-

view

336 -

download

2

Transcript of Lec_23 Effect of Substrate Bias VB and Channel Bias VC

1Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

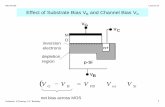

( ) SioxFBBG VVVVV ++=−

net bias across MOS

MO

p-Si

VVG

C

inversionelectrons

depletionregion

VB

n+n+

Effect of Substrate Bias VB and Channel Bias VC

2Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

( )

( )s

da

OX

daFBBG

BCpSi

XqNCXqNVVV

VVV

ε

φ

max2

max

21

2

++=−

−+=

M O SiEi

Efs

q(VC-VB)

Efn

pqφ

pqφ

s

daSi

XqNVε

max2

21

=

At the onset of strong inversion, where VG is defined as the threshold voltage

3Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

At threshold: VG – VB = VFB+Vox+VSi But VSi = 2|Φp| + (VC - VB ) => xdmax is different from no-bias case

B

SiSid qN

Vx ε2=max

VT -VB = VFB + 2εsqNB(2|φF| + VC-VB)

Cox + 2|φF| + VC - VB

VoxVSi

4Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Flat Band Voltage with Oxide charges

VFB is the Gate voltage required to create no charge in the Si

dxx

xxCC

QV

oxx

ox

ox

oxox

fSMFB ∫−−Φ−Φ≡

0

)(1 ρ

x = 0 x = xox

M O S

ρox (x)Qf

ρox (x) due to alkaline contaminants or trapped charge

Qf due to broken bonds at Si-SiO2 interface

5Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

VT Tailoring with Ion Implantation

Nsub

Shallow implanted dopant profile at Si-SiO2interface (approximated asa delta function)

• Acceptor implant gives positive shift (+ ∆VT)• Donor implant gives negative shift - ∆VT

Algebraic sign of VT shift is independent of n or p substrate !

OX

iT C

QV =∆

Qi = q • implant dose in Si

6Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

p-Si

implanted acceptors

NaSiO2

Doping Profile After Implantation

SiO2

xdmax

Q

Qd

d

Qn

p-Si

(due to implanted acceptors)

Charge Distribution for V G > VT

* Valid if thickness of implanted dopants << xdmax

The VT shift can be viewed as the extra gate voltage needed todeplete the implanted dopants ~ Qi/Cox

The delta-function approximation of implanted profile

7Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Summary : Parameters Affecting VT

6

7

n+

Na

VB

5

1

2

4

3

Dopant implant near Si/SiO2 interface

fOX Q&ρ Mφ

xox

VCQn n+

8Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

+ Qf or Qox

B threshold implant

As or P threshold implant

Xox increases

Xox increases

ΦM increases

ΦM decreases

|VCB| increases

|VCB| increases

9Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Summary of MOS Threshold Voltage (NMOS, p-substrate)

• Threshold voltage of MOS capacitor:

• Threshold voltage of MOS transistor:

Note 1: At the onset of strong inversion, inversion charge is negligible and is often ignored in the VT expressionNote 2: VT of a MOSFET is taken as the VT value at source ( i.e., VC =VS)Note 3 : Qi = (q • implant dose ) is the charge due to the ionized donorsor acceptors implanted at the Si surface. Qi is negative for acceptors and is positive for donors

VT = VFB + 2εsqNB(2|φF|)

Cox + 2|φF| -

QiCox

VT = VFB + 2εsqNB(2|φF| + VC-VB)

Cox + 2|φF| + VC -

QiCox

10Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Summary of MOS Threshold Voltage (PMOS, n-substrate)

• Threshold voltage of MOS capacitor:

• Threshold voltage of MOS transistor:

* Yes, + sign for VC term but VC (<0) is a negative bias for PMOS because theinversion holes have to be negatively biased with respect to the n-substrateto create a reverse biased pn junction.

VT = VFB - 2εsqNB(2|φF|)

Cox - 2|φF| -

QiCox

VT = VFB - 2εsqNB(2|φF| + VC-VB)

Cox - 2|φF| + VC -

QiCox

11Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Negligible electron concentration underneath Gate region; Source-Drain is electrically open

High electron concentration underneath Gate region; Source-Drain is electrically connected

VG < Vthreshold VG > Vthreshold

Metal -Oxide-Semiconductor Transistor [ n-channel]

12Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

MOSFET I-V Analysis

n+ n+

VS VG

W

VB=0

VD

ID

L

Qn

N-MOSFET

•In general, inversion charge Qn (∝ [VG-VT]) decreases from Source towardDrain because channel potential VC increases.

VT increases

13Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Let VT defined to be threshold voltage at Source

( )

−−=

−=

+

2VVVC

)average(VVC)average(Q2

VV~)average(V

DSTGOX

TGOXn

DSTT [ This is an approximation ]

ID = Wt • (-q n vdrift)= W• Qn • vdrift

Inversion layer thickness Inversion layer concentration

Approximate Analysis

Note: ID is constant for all positionsalong channel

14Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

LVEvWith DSn

ndriftµ

≈µ−=

DSDS

TGOXD V2

VVVCLWI

−−µ=

VDS

ID

Linear with VDS

Quadratic with VDS

15Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

VD saturation

n+ n+

VS=0

VD

Qn=0 at the drain

Lateral E-field →∞Electrons moves

saturation velocity

VDsat is defined to be the value of VDwith Qn=0 at drain.

From Qn = Cox (VG -VT -VD), we get VDsat =VG-VT

16Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

17Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

VD

ID

18Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

DSDS

TGOXn

D VVVVCLWI

−−=

2µ

MOSFET I-V Characteristics Summary

For VD < VDsat

( )22 TGOXn

DsatD VVCLWII −==

µ

For VD > VDsat

Note: VDsat = VG - VT

19Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Ex

SiO2inversionlayer

Mobility of inversion charge carriers

*Carrier will experience additional scattering at theSi/SiO2 interface

*Channel mobility is lower than bulk mobility

* µ(effective) is extracted from MOSFET I-V characteristics* Typically ~0.5 of µ(bulk)

20Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Parameter Extraction from MOSFET I-V

(A) VT VD

ID

D

S

( )

.

0

221

2

'

'

modesaturationinisMOSFEToffpinchatisDrain

VV

VqNC

VV

drainatV

VVVFor

TG

DpasOX

pDFB

T

TGD

⇒−⇒

<−⇒

++

++=

>=

φε

φ

21Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

( )2TDDsatD VVLWkII −==∴

VDVT

DI

LkWslope=

VG

µnCOX

22Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Alternative way to extract VT

•Measure ID versus VG for a fixed small VDS (say <100mV)

The intercept of ID versus VG plot on VG-axis is VT.

( ) DSTGOXn

DSDS

TGOXn

D

VVVCLW

V2

VVVCLWI

−µ

≈

−−

µ=

VTVG

ID

23Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

VD

ID

VB(varies)

VD

VB =0 VB1 VB2

VT0 VT1 VT2

DI

( ) ( )

OX

as

pSBp

SBTSBT

CqN

V

VwithVVwithV

ε

φφγ

2

22

00

=

−+

=−≠≡

(B) Body Coefficient γ

24Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

ID

VD

VG2

VG1

(C)

VD

( ) DTGOXnD

D

DD

TGOXnD

VsmallforVVL

WCVI

VVVVCL

WI

−=∂∂

−−=

µ

µ2

ID

VG slope

LWCOXnµ

25Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

(D) Transconductance gm

(a) For VDS<VDsat

(b) For VDS > VDsat

DVfixedG

Dm V

Ig∂∂

≡

DSOXnG

D

DSDS

TGOXn

D

VL

WCVI

VVVVCLWI

⋅=∂∂

∴

−−=

µ

µ2

( )

( )TGOXn

G

D

TGOXn

DsatD

VVCLW

VI

VVCLWII

−⋅=∂∂

−==

µ

µ 2

2

ID

VDS

VG1+∆VG

VG1

VDsat

[gm varies with VDS]

[gmsat varies with VG]

26Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

ID

VDVDsat

real

ideal

n+ n+

Qn

( ) ( )1

2

)(01.01.0~

12

−

+−=

volttoTypically

VVVkI DSTGDsat

λ

λ

(E) Channel Modulation Parameter λ

27Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Short Channel Effect on VT

VT

idealanalysis

Ldepletionchargecontrolledby gate.

n+ n+

VG

pdepletion layer

L

28Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

n+ n+

VS=0 VD=0

Wo

x

WoXj+Wo

Xj

Xj

Xj

L’

L

( )[ ]

−+−=

−−+−=

−=

1212

2

2'22

j

oj

jooj

XWXL

XWWXL

xLL Note: Wo is xdmax

Sameelectric potentialbecause of heavily doped n+

29Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

fXW

LX

WWLLNq

j

oj

ideal

actual

oa

≡

−+−=

=∴

⋅⋅+

⋅⋅=

1211

21

Area of gate charge distribution

“Yau Model” for short-channel effect.

30Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

•Implantation at low energy•Small Dt.•Minimize channeling and transient enhance diffusion

To make f 1

Xj

Wo •Increase Na

L large

S/D S/D

L small

S/DS/D

31Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

VT

L

Large VDS

VDS ~ 0

Effect of VDS on VT Lowering

Large VDS ⇒ Larger S/D depletion charge at the drain side ⇒ Smaller depletion region charge contributed by gate⇒ VT starts to decrease at larger L

n+ n+

VG

depletion layer

Depletion charge contributedby gate

32Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

parasiticchargewhich has to be createdby gate bias

∴VT is larger than ideal analysis.

Fox Fox

W

Ideal Depletion charge

W

Narrow Width Effect (related to W)

33Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

VT

W

VT

L

Narrow Width Effect

Narrow Channel Effect

34Professor N Cheung, U.C. Berkeley

Lecture 23EE143 S06

Small Geometry Effects Summary

W

L

Actual gate control charge

Idealgate controlcharge

![10-cohort studies 11 [ ])promesi.med.auth.gr/mathimata/6_meletes_seiron.pdf · Συστηµατικά σφάλµατα (bias) στις µελέτες κοόρτης Σφάλα επιλογής](https://static.fdocument.org/doc/165x107/5e388110c2fc40648204f356/10-cohort-studies-11-f-f-bias-f.jpg)