DRV13x Audio-Balanced Line Drivers · 2020. 12. 31. · V IN Gnd A2 +V O 10k! 50! 50! All resistors...

Transcript of DRV13x Audio-Balanced Line Drivers · 2020. 12. 31. · V IN Gnd A2 +V O 10k! 50! 50! All resistors...

-

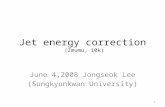

VIN

Gnd

+VOA2

10kΩ

50Ω

50Ω

All resistors 30kΩ unless otherwise indicated.

V+

+Sense

–Sense

–VO

V–

A3

A1

10kΩ

Product

Folder

Sample &Buy

Technical

Documents

Tools &

Software

Support &Community

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

DRV13x Audio-Balanced Line Drivers1 Features 3 Description

The DRV134 and DRV135 are differential output1• Balanced Output

amplifiers that convert a single-ended input to a• Low Distortion: 0.0005% at f = 1 kHz balanced output pair. These balanced audio drivers• Wide Output Swing: 17Vrms into 600 Ω consist of high performance op amps with on-chip

precision resistors. They are fully specified for high• High Capacitive Load Driveperformance audio applications and have excellent ac• High Slew Rate: 15 V/µs specifications, including low distortion (0.0005% at 1

• Wide Supply Range: ±4.5 V to ±18 V kHz) and high slew rate (15 V/µs).• Low Quiescent Current: ±5.2 mA The on-chip resistors are laser-trimmed for accurate• 8-Pin DIP, SO-8, and SOL-16 Packages gain and optimum output common-mode rejection.

Wide output voltage swing and high output drive• Companion to Audio Differential Line Receivers:capability allow use in a wide variety of demandingINA134 and INA137applications. They easily drive the large capacitive• Improved Replacement for SSM2142 loads associated with long audio cables. Used incombination with the INA134 or INA137 differential2 Applications receivers, they offer a complete solution fortransmitting analog audio signals without degradation.• Audio Differential Line Drivers

• Audio Mix Consoles The DRV134 is available in 8-pin DIP and SOL-16surface-mount packages. The DRV135 comes in a• Distribution Amplifiersspace-saving SO-8 surface-mount package. Both are• Graphic and Parametric Equalizers specified for operation over the extended industrial

• Dynamic Range Processors temperature range, –40°C to +85°C and operate from–55°C to +125°C.• Digital Effects Processors

• Telecom SystemsDevice Information(1)• Hi-Fi Equipment

PART NUMBER PACKAGE BODY SIZE (NOM)• Industrial Instrumentation

DRV134 SOIC (16) 10.30 mm × 7.50 mmDRV135 SOIC (8) 4.90 mm × 3.91 mm

(1) For all available packages, see the orderable addendum atthe end of the datasheet.

4 Simplified Schematic

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,intellectual property matters and other important disclaimers. PRODUCTION DATA.

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Table of Contents8.4 Device Functional Modes........................................ 131 Features .................................................................. 1

9 Application and Implementation ........................ 152 Applications ........................................................... 19.1 Application Information............................................ 153 Description ............................................................. 19.2 Typical Application ................................................. 154 Simplified Schematic............................................. 1

10 Power Supply Recommendations ..................... 175 Revision History..................................................... 211 Layout................................................................... 176 Pin Configuration and Functions ......................... 3

11.1 Layout Guidelines ................................................. 177 Specifications......................................................... 411.2 Layout Examples................................................... 187.1 Absolute Maximum Ratings ...................................... 411.3 Thermal Performance ........................................... 197.2 Handling Ratings....................................................... 4

12 Device and Documentation Support ................. 197.3 Recommended Operating Conditions ...................... 412.1 Documentation Support ........................................ 197.4 Electrical Characteristics........................................... 512.2 Related Links ........................................................ 197.5 Typical Characteristics .............................................. 612.3 Trademarks ........................................................... 198 Detailed Description ............................................ 1112.4 Electrostatic Discharge Caution............................ 198.1 Overview ................................................................. 1112.5 Glossary ................................................................ 198.2 Functional Block Diagram ....................................... 11

13 Mechanical, Packaging, and Orderable8.3 Feature Description................................................. 11Information ........................................................... 20

5 Revision History

Changes from Revision A (April 2007) to Revision B Page

• Added Handling Rating table, Feature Description section, Device Functional Modes, Application andImplementation section, Power Supply Recommendations section, Layout section, Device and DocumentationSupport section, and Mechanical, Packaging, and Orderable Information section ............................................................... 1

2 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

Top View 8-Pin DIP/SO-8 Top View SOL-16

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

NC

NC

+VO

+Sense

V+

V–

NC

NC

NC

NC

–VO

–Sense

Gnd

VIN

NC

NC

1

2

3

4

8

7

6

5

+VO

+Sense

V+

V–

–VO

–Sense

Gnd

VIN

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

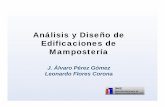

6 Pin Configuration and Functions

NOTE: NC - No internal connection

Pin FunctionsPIN

I/O DESCRIPTIONNAME DIP-8 and SO-8 SOL-16Gnd 3 5 – Ground+Sense 7 13 I Sensing, non-inverting input–Sense 2 4 I Sensing, inverting inputV+ 6 12 – Positive supplyV– 5 11 – Negative supplyVIN 4 6 I Input–Vo 1 3 O Inverted, balanced differential output+Vo 8 14 O Balanced differential outputNC – 1,2,7,8,9,10,15,16 – These pins should be left unconnected

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

7 Specifications

7.1 Absolute Maximum Ratingsover operating free-air temperature range (unless otherwise noted) (1)

MIN MAX UNITSupply voltage, V+ to V– 40 VInput voltage range V– V+Output short-circuit (to ground) ContinuousOperating temperature –55 125 °CJunction temperature 150 °C

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratingsonly, which do not imply functional operation of the device at these or any other conditions beyond those indicated under RecommendedOperating Conditions . Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

7.2 Handling RatingsMIN MAX UNIT

Tstg Storage temperature range –55 125 °CHuman body model (HBM), per ANSI/ESDA/JEDEC JS-001, all –2000 2000pins (1)

V(ESD) Electrostatic discharge VCharged device model (CDM), per JEDEC specification –500 500JESD22-C101, all pins (2)

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditionsover operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNITTspe Specification temperature range –40 85 °CTA Operation temperature range –55 125 °CV+ Positive supply 4.5 18 18 VV– Negative supply –4.5 –18 –18 V

4 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

7.4 Electrical CharacteristicsAt TA = +25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITAUDIO PERFORMANCETHD+N Total Harmonic Distortion + Noise 0.001%f = 20Hz to 20kHz, VO = 10Vrms

0.0005%f = 1kHz, VO = 10Vrms20 kHz BWRTO (1) Noise Floor –98 dBuTHD+N < 1%RTO (1) Headroom 27 dBu

INPUTZIN Input Impedance (2) 10 kΩIIN Input Current VIN = ±7.07 V –1000 ±700 1000 µAGAIN

DifferentialInitial 5.8 6 dB[(+VO) – (–VO)]/VIN

VIN = ±10VError –2% ±0.1% 2%Error vs Temperature ±10 ppm/°CSingle-Ended VIN = ±5VInitial 5.8 6 dBError –2% ±0.7% 2%Error vs Temperature ±10 ppm/°CNonlinearity 0.0003 % of FS

OUTPUTOCMR Common-Mode Rejection, f = 1kHz See Figure 25 46 68 dBSBR Signal Balance Ratio, f = 1kHz See Figure 26 35 54 dB

Output Offset VoltageVOCM(3) Offset Voltage, Common-Mode VIN = 0 –250 ±50 250 mV

Offset Voltage, Common-Mode vs ±150 µV/°CTemperature

VOD(4) Offset Voltage, Differential VIN = 0 –10 ±1 10 mVOffset Voltage, Differential vs Temperature ±5 µV/°C

PSRR Offset Voltage, Differential vs Power Supply VS = ±4.5V to ±18V 80 110 dBPositive (V+) – 3 (V+) – 2.5

Output Voltage Swing, No Load (5) VNegative (V–) + 2 (V–) + 1.5

Impedance 50 ΩCL Load Capacitance, Stable Operation CL Tied to Ground (each output) 1 µFISC Short-Circuit Current ±85 mAFREQUENCY RESPONSE

Small-Signal Bandwidth 1.5 MHzSR Slew Rate 15 V/µs

Settling Time: 0.01% VOUT = 10V Step 2.5 µsOverload Recovery Output Overdriven 10% 3 µs

POWER SUPPLYVS Rated Voltage ±18 V

Voltage Range ±4.5 ±18 VIQ Quiescent Current IO = 0 –5.5 ±5.2 5.5 mA

(1) dBu = 20log (Vrms /0.7746); RTO = Referred-to-Output.(2) Resistors are ratio matched but have ±20% absolute value.(3) VOCM = [(+VO) + (–VO)] / 2.(4) VOD = (+VO) – (–VO).(5) Ensures linear operation. Includes common-mode offset.

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

Frequency (Hz)

TH

D+

N(%

)

20 100 1k 10k 20k

0.1

0.01

0.001

0.0001

–VO or +VO Grounded

A: R1 = 600Ω (250 ft cable)

B: R1 = ∞ (no cable)

Single-Ended Mode

VO = 10Vrms

DRV134 Output

B

A

Frequency (Hz)

TH

D+

N (

%)

20 100 1k 10k 20k

0.01

0.001

0.0001

Differential Mode

VO = 10Vrms

See Figure 3 for Test Circuit

A: R1 = R2 = RL = ∞ (no load)

B: R1 = R2 = ∞ RL = 600Ω

INA137 Output

A (no cable)

B (500ft cable)

Frequency (Hz)

TH

D+

N(%

)

20 100 1k 10k 20k

C

0.01

0.001

0.0001

See Figure 3 for Test Circuit

A: R1 = R2 = RL = (no load)∞

B: R1 = R2 = 600Ω, RL = ∞

C: R1 = R2 = , R∞ L = 600Ω

Differential Mode

VO = 10Vrms

No Cable

DRV134 Output

A

B

Frequency (Hz)

TH

D+

N (

%)

20 100 1k 10k 20k

0.01

0.001

0.0001

C

See Figure 3 for Test Circuit

A: R1 = R2 = RL = (no load)∞

B: R1 = R2 = 600Ω, RL = ∞

C: R1 = R2 = , R∞ L = 600Ω

Differential Mode

VO = 10Vrms

500 ft cable

DRV134 Output

B

A

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Electrical Characteristics (continued)At TA = +25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITTEMPERATURE RANGE

Specification Range –40 85 °COperation Range –55 125 °CStorage Range –55 125 °C

θJA Thermal Resistance 8-Pin DIP 100 °C/WSO-8 Surface mount 150 °C/WSOL-16 Surface 80 °C/Wmount

7.5 Typical CharacteristicsAt TA = 25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

Figure 1. Total Harmonic Distortion + Noise vs Frequency Figure 2. Total Harmonic Distortion + Noise vs Frequency

Figure 3. Total Harmonic Distortion + Noise Figure 4. System Total Harmonic Distortion + Noisevs Frequency vs Frequency

6 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

Frequency (Hz)

Vo

lta

ge N

ois

e (

nV

/√H

z)

1 10 100 1k 10k 100k 1M

10k

1k

100

10

Frequency (Hz)

Vo

lta

ge

No

ise

(µ

Vrm

s)

1 10 100 1k 10k 100k

100

10

1

0.1

Frequency (Hz)

Am

plit

ud

e (

% o

f F

un

da

me

nta

l)

20 100 1k 20k10k

0.01

0.001

0.0001

0.00001

Differential Mode

2nd Harmonic

3rd Harmonic

No Cable, RL = ∞

500 ft Cable,

RL = 600Ω

Frequency (Hz)

Vo

lta

ge

Ga

in (

dB

)

1k 10k 100k 10M1M

10

5

0

–5

–10

Output Amplitude (dBu)

TH

D+

N(%

)

5 10 15 20 3025

1

0.1

0.01

0.001

0.0001

No Cable

RL = ∞

500 ft Cable

RL = 600Ω

Single-Ended

Mode

f = 1kHz

DRV134 Output

Differential

Mode

500 ft Cable

RL = 600Ω

Output Amplitude (dBu)

DIM

(%

)

5 10 15 20 3025

1

0.1

0.01

0.001

0.0001

Differential Mode

No Cable

RL = ∞

500 ft Cable

RL = 600Ω

BW = 30kHz

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

Typical Characteristics (continued)At TA = 25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

Figure 5. Headroom – Total Harmonic Distortion + Noise Figure 6. Dim Intermodulation Distortionvs Output Amplitude vs Output Amplitude

Figure 7. Harmonic Distortion Products vs Frequency Figure 8. Gain vs Frequency

Figure 9. Output Voltage Noise Spectral Density Figure 10. Output Voltage Noisevs Frequency vs Noise Bandwidth

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

Supply Voltage (V)

Qu

iesce

nt

Cu

rre

nt

(mA

)

±4 ±18±16±14±12±10±8±6

±5.6

±5.4

±5.2

±5

±4.8

±4.6

T = –55°C

T = +25°C

T = +125°C

Temperature (°C)

Short

-Circuit C

urr

ent (m

A)

–75 –50 –25 0 25 50 75 125100

±120

±100

±80

±60

±40

±20

+ISC

–ISC

Output Current (mA)

Outp

ut V

oltage S

win

g (

V)

0 ±20 ±40 ±60 ±80 ±100

18

16

14

12

10

8

–8

–10

–12

–14

–16

–18

–55°C

+25°C

+125°C

+125°C+25°C –55°C

Supply Voltage (V)

Diffe

ren

tia

l O

utp

ut

Vo

lta

ge

(V

rms)

±4 ±6 ±8 ±10 ±12 ±14 ±16 ±18

20

16

12

8

4

0

THD+N ≤ 0.1%

Frequency (Hz)

Po

we

r S

up

ply

Re

jectio

n(d

B)

10 100 1k 1M100k10k

120

100

80

60

40

20

0

+PSRR

–PSRR

VS = ±4.5V to ±18V

Frequency (Hz)

Ou

tpu

t V

olta

ge

Sw

ing

(V

rms)

10k 20k 100k80k50k

20

16

12

8

4

0

0.1% Distortion

0.01% Distortion

RL = 600Ω

Diff Mode

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Typical Characteristics (continued)At TA = 25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

Figure 11. Power Supply Rejection vs Frequency Figure 12. Maximum Output Voltage Swing vs Frequency

Figure 13. Output Voltage Swing vs Supply Voltage Figure 14. Output Voltage Swing vs Output Current

Figure 15. Quiescent Current vs Supply Voltage Figure 16. Short-Circuit Current vs Temperature

8 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

2µs/div

5V

/div

2µs/div

5V

/div

2µs/div

50m

V/d

iv

2µs/div

50m

V/d

ivP

erc

en

t of

Un

its (

%)

Common-Mode Offset Voltage (mV)

–2

50

–2

25

–2

00

–1

75

–1

50

–1

25

–1

00

–7

5

–5

0

–2

5 0

25

50

75

10

0

12

5

15

0

17

5

20

0

22

5

25

0

35

30

25

20

15

10

5

0

Typical productiondistribution of packagedunits. All package typesincluded.

Pe

rce

nt

of

Un

its (

%)

Differential Offset Voltage (mV)

–1

0

–9

–8

–7

–6

–5

–4

–3

–2

–1 0 1 2 3 4 5 6 7 8 9

10

45

40

35

30

25

20

15

10

5

0

Typical productiondistribution of packagedunits. All package typesincluded.

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

Typical Characteristics (continued)At TA = 25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

Figure 17. Differential Offset Voltage Figure 18. Common-Mode Offset VoltageProduction Distribution Production Distribution

CL = 100 pF CL = 1000 pF

Figure 19. Small-Signal Step Response Figure 20. Small-Signal Step Response

CL = 100 pF CL = 1000 pF

Figure 21. Large-Signal Step Response Figure 22. Large-Signal Step Response

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

Load Capacitance (pF)

Overs

hoot (%

)

10 1k100 10k

40

30

20

10

0

100mV Step

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Typical Characteristics (continued)At TA = 25°C, VS = ±18 V, RL = 600 Ω differential connected between +VO and –VO, unless otherwise noted.

Figure 23. Small-Signal Step Overshoot vs Load Capacitance

10 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

VIN

Gnd

+VOA2

10kΩ

50Ω

50Ω

All resistors 30kΩ unless otherwise indicated.

+Sense

–Sense

–VO

G = +6dB

V+

(12)6

A3

A1

10kΩ

1µF

V–

DRV134

DRV135

5 (11)

1µF

4

(6)

3

(5)

8

(14)

7

(13)

2

(4)

1

(3)

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

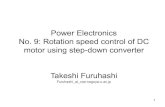

8 Detailed Description

8.1 OverviewThe DRV134 and DRV135 consist of an input inverter driving a cross- coupled differential output stage with 50 Ωseries output resistors. Characterized by low differential-mode output impedance (50 Ω) and high common-modeoutput impedance (1.6 kΩ), the DRV134 and DRV135 are ideal for audio applications.

Excellent internal design and layout techniques provide low signal distortion, high output level (27 dBu), and alow noise floor (–98 dBu). Laser trimming of thin film resistors assures excellent output common-mode rejection(OCMR) and signal balance ratio (SBR). In addition, low dc voltage offset reduces errors and minimizes loadcurrents.

The Functional Block Diagram section shows a detailed block diagram of the DRV134 and DRV135.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Audio PerformanceThe DRV134 and DRV135 were designed for enhanced ac performance. Very low distortion, low noise, and widebandwidth provide superior performance in high quality audio applications. Laser-trimmed matched resistorsprovide optimum output common-mode rejection (typically 68dB), especially when compared to circuitsimplemented with op amps and discrete precision resistors. In addition, high slew rate (15 V/μs) and fast settlingtime (2.5 μs to 0.01%) ensure excellent dynamic response.

The DRV134 and DRV135 have excellent distortion characteristics. As shown in the distortion data provided inthe Typical Characteristics section, THD+Noise is below 0.003% throughout the audio frequency range undervarious output conditions. Both differential and single-ended modes of operation are shown. In addition, theoptional 10μF blocking capacitors used to minimize VOCM errors have virtually no effect on performance.Measurements were taken with an Audio Precision System One (with the internal 80 kHz noise filter) using theTHD test circuit shown in Figure 24.

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 11

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

600Ω

VCM = 10Vp-p

300Ω(1)

300Ω(1)

VIN

Gnd

+VO

VOD

–VO

DRV134

1µF

+18V

6

8

1

7

2

1µF

–18V

5

4

3

R1 R2

RL VOUTINA137

1µF

VIN

+VO –In

+In

–VO

+18V

72

3

61

5

1µF

–18V

4

DRV134

1µF

+18V

6

8

1

7

2

1µF

–18V

5

4

3

Test Point

or

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Feature Description (continued)Up to approximately 10 kHz, distortion is below the measurement limit of commonly used test equipment.Furthermore, distortion remains relatively constant over the wide output voltage swing range (approximately 2.5V from the positive supply and 1.5 V from the negative supply). A special output stage topology yields a designwith minimum distortion variation from lot-to-lot and unit-to-unit. Furthermore, the small and large signal transientresponse curves demonstrate the stability under load of the DRV134 and DRV135.

Figure 24. Distortion Test Circuit

8.3.2 Output Common-Mode RejectionOutput common-mode rejection (OCMR) is defined as the change in differential output voltage due to a changein output common-mode voltage. When measuring OCMR, VIN is grounded and a common-mode voltage, VCM,is applied to the output as shown in Figure 25. Ideally no differential mode signal (VOD) should appear.However, a small mode-conversion effect causes an error signal whose magnitude is quantified by OCMR.

Figure 25. Output Common-Mode Rejection Test Circuit

8.3.3 Signal Balance RatioSignal balance ratio (SBR) measures the symmetry of the output signals under loaded conditions. To measureSBR an input signal is applied and the outputs are summed as shown in Figure 26. VOUT should be zero sinceeach output ideally is exactly equal and opposite. However, an error signal results from any imbalance in theoutputs. This error is quantified by SBR. The impedances of the DRV134 and DRV135’s output stages areclosely matched by laser trimming to minimize SBR errors. In an application, SBR also depends on the balanceof the load network.

12 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

VIN

Gnd

+VOA2

10kΩ

50Ω

50Ω

All resistors 30kΩ unless otherwise indicated.

+Sense

–Sense

–VO

G = +6dB

V+

(12)6

A3

A1

10kΩ

1µF

V–

DRV134

DRV135

5 (11)

1µF

4

(6)

3

(5)

8

(14)

7

(13)

2

(4)

1

(3)

600Ω

300Ω(1)

300Ω(1)

VOUT

VIN = 10Vp-p +VO

O–V

DRV134

1µF

+18V

6

8

1

7

2

1µF

–18V

Gnd

5

4

3

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

Feature Description (continued)

Figure 26. Signal Balance Ratio Test Circuit

8.4 Device Functional Modes

8.4.1 Differential-Output ModeIn differential-output mode, the DRV134 (and DRV135 in SO-8 package) converts a single-ended, ground-referenced input to a floating differential output with +6 dB gain (G = 2). Figure 27 shows the basic connectionsrequired for operation in differential-output mode.

Normally, +VO is connected to +Sense, –VO is connected to –Sense, and the outputs are taken from thesejunctions as shown in Figure 27.

Figure 27. Basic Connections for Differential-Output Mode

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 13

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

600Ω

VOUT

= 2VIN

VIN

V+

V–

DRV134

8

1

7

2

G = +6dB

4

5

6

3

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Device Functional Modes (continued)8.4.2 Single-Ended ModeThe DRV134 can be operated in single-ended mode without degrading output drive capability. Single-endedoperation requires that the unused side of the output pair be grounded (both the VO and Sense pins) to a lowimpedance return path. Gain remains +6 dB. Grounding the negative outputs as shown in Figure 28 results in anon-inverted output signal (G = +2) while grounding the positive outputs gives an inverted output signal (G = –2).

Figure 28. Typical Single-Ended Application

For best rejection of line noise and hum differential mode operation is recommended. However, single-endedperformance is adequate for many applications. In general single ended performance is comparable todifferential mode (see THD+N typical performance curves), but the common mode and noise rejection inherent inbalanced-pair systems is lost.

14 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

VIN

Gnd

A2

10kΩ

50Ω

50Ω

All resistors 30kΩ unless otherwise indicated.

INA134 (G = 1): VO = 2VININA137 (G = 1/2): VO = VIN

A3

A1

10kΩ

DRV134

DRV135

4

3

8

+VO

–VO+VO

–VO

7

2

1

INA134, INA137

RECEIVER

DRIVER

BALANCED

CABLE PAIR

VO

5

6

1

2

3

10µF(1)

10µF(1)

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

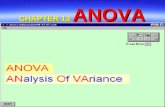

9 Application and Implementation

NOTEInformation in the following applications sections is not part of the TI componentspecification, and TI does not warrant its accuracy or completeness. TI’s customers areresponsible for determining suitability of components for their purposes. Customers shouldvalidate and test their design implementation to confirm system functionality.

9.1 Application InformationDecoupling capacitors placed close to the device pins are strongly recommended in applications with noisy orhigh impedance power supplies.

For best system performance, it is recommended that a high input-impedance difference amplifier be used as thereceiver. Used with the INA134 (G = 0 dB) or the INA137 (G = ±6 dB) differential line receivers, the DRV134forms a complete solution for driving and receiving audio signals, replacing input and output couplingtransformers commonly used in professional audio systems (Figure 29). When used with the INA137 (G = –6 dB)overall system gain is unity.

9.2 Typical Application

9.2.1 Cable Driving ApplicationThe DRV134 is capable of driving large signals into 600-Ω loads over long cables. Low impedance shieldedaudio cables such as the standard Belden 8451 or 9452 (or similar) are recommended, especially in applicationswhere long cable lengths are required.

For applications with large dc cable offset errors, a 10-µF electrolytic nonpolarized blocking capacitor at eachsense pin is recommended as shown in Figure 29.

Figure 29. Complete Audio Driver and Receiver Circuit

9.2.1.1 Design RequirementsConsider a design with the goal of differentially transmitting a single ended signal of up to 22.2 dBu through 500ft of cable with no load at the receiving side. The signal at the end of the cable should have no more than 0.002percent of total harmonic distortion plus noise (THD+N) at 10 kHz and less than 0.0005 percent of THD+N forfrequencies between 20 Hz and 1 kHz.

The system is required to put out a single ended signal 0 dB with respect to the input signal and accommodateinputs with peak to RMS ratios of up to 1.5 for the maximum 22.2 dBu range established above.

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 15

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

R1 R2

RL VOUTINA137

1µF

VIN

+VO –In

+In

–VO

+18V

72

3

61

5

1µF

–18V

4

DRV134

1µF

+18V

6

8

1

7

2

1µF

–18V

5

4

3

Test Point

or

� � PEAKPEAK_IN V97.1498.95.1V

RMS20

L

IN V98.910775.0Vu

¸¸

¹

·

¨¨

©

§

¸¹

ᬩ

§

775.0

xlog20L 10u

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

Typical Application (continued)9.2.1.2 Detailed Design ProcedureThe dBu is a common unit of measurement for input sensitivity and output level of professional audio equipment.A 0 dBu signal dissipates 1 mW into a 600-Ω resistive load; therefore, a 0 dBu signal corresponds toapproximately 0.775 VRMS. Equation 1 shows the relationship between the signal level in dBu (denoted by Lu)and the signal level in VRMS (denoted by x).

(1)

For this design, the single ended input signal of 22.2 dBu corresponds to 9.98 VRMS as shown in Equation 2.

(2)

Given that the system must accommodate for 22.2 dBu signals with up to 1.5 of peak to RMS ratio, themaximum peak input signal is 14.97 VPEAK as calculated in Equation 3.

(3)

The DRV134 is chosen to convert the single ended input signal into a differential signal and the outputs of theDRV134 will be connected to one end of the 500 ft cable. In order to prevent clipping and distortion of the inputsignal, the power supply rails for the DRV134 are chosen as 3 V above and below the peak calculated inEquation 3. The 3 V margin is derived from the output voltage swing specification given in the ElectricalCharacteristics table. The supplies selected are 18 V for V+ and –18 V for V–.

Finally, the INA137 is used at the end of the 500 ft cable in order to convert the differential signal output of theDRV134 into a single ended signal that is 0 dB with respect to the input signal.

Figure 30 shows the system diagram.

Figure 30. Diagram of System Based on DRV134 and INA137

16 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

Frequency (Hz)

TH

D+

N (

%)

20 100 1k 10k 20k

0.01

0.001

0.0001

C

See Figure 3 for Test Circuit

A: R1 = R2 = RL = (no load)∞

B: R1 = R2 = 600Ω, RL = ∞

C: R1 = R2 = , R∞ L = 600Ω

Differential Mode

VO = 10Vrms

500 ft cable

DRV134 Output

B

A

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

Typical Application (continued)9.2.1.3 Application CurveFigure 31 shows the performance obtained with the system depicted in Figure 30.

Figure 31. Measured Performance of a System Based on DRV134

10 Power Supply RecommendationsThe DRV134 and DRV135 are designed to operate from an input voltage supply range between ±4.5 V and ±18V. This input supply should be well regulated. If the input supply is located more than a few inches from theDRV134 or DRV135 additional bulk capacitance may be required in addition to the ceramic bypass capacitors.

11 Layout

11.1 Layout GuidelinesA driver/receiver balanced-pair (such as the DRV134 and INA137) rejects the voltage differences between thegrounds at each end of the cable, which can be caused by ground currents, supply variations, etc. In addition toproper bypassing (as shown in Figure 32 and Figure 33), the suggestions below should be followed to achieveoptimal OCMR and noise rejection.• The DRV134 input should be driven by a low impedance source such as an op amp or buffer.• As is the case for any single-ended system, the source’s common should be connected as close as possible

to the DRV134’s ground. Any ground offset errors in the source will degrade system performance.• Symmetry on the outputs should be maintained.• Shielded twisted-pair cable is recommended for all applications. Physical balance in signal wiring should be

maintained. Capacitive differences due to varying wire lengths may result in unequal noise pickup betweenthe pair and degrade OCMR. Follow industry practices for proper system grounding of the cables.

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 17

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

DRV135

-Vo +Vo

+Sense

V-

-Sense

1 8

Top View

LEGEND

TOP layer: copper pour & traces

PCB

via to ground plane

VIN

V+

1 µF

SMD0603

4 51 µF

SMD0603

Gnd

DRV134

NC

-Vo

NC

+Vo

+Sense

V-

NC

-Sense

1 16

Top View

LEGEND

TOP layer: copper pour & traces

PCB

via to ground plane

VIN

NC

V+

NC

NC

NCNC

1 µF

SMD0603

8 9

1 µF

SMD0603

Gnd

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

11.2 Layout Examples

Figure 32. DRV134 Layout Example

Figure 33. DRV135 Layout Example

18 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

DRV134, DRV135www.ti.com SBOS094B –JANUARY 1998–REVISED DECEMBER 2014

11.3 Thermal PerformanceThe DRV134 and DRV135 have robust output drive capability and excellent performance over temperature. Inmost applications there is no significant difference between the DIP, SOL-16, and SO-8 packages. However, forapplications with extreme temperature and load conditions, the SOL-16 (DRV134UA) or DIP (DRV134PA)packages are recommended. Under these conditions, such as loads greater than 600 Ω or very long cables,performance may be degraded in the SO-8 (DRV135UA) package.

12 Device and Documentation Support

12.1 Documentation Support

12.1.1 Related DocumentationFor related documentation see the following:• Audio Differential Line Receivers 0dB (G = 1), INA134• Audio Differential Line Receivers ±6dB (G = 1/2 or 2), INA137

12.2 Related LinksThe table below lists quick access links. Categories include technical documents, support and communityresources, tools and software, and quick access to sample or buy.

Table 1. Related LinksTECHNICAL TOOLS & SUPPORT &PARTS PRODUCT FOLDER SAMPLE & BUY DOCUMENTS SOFTWARE COMMUNITY

DRV134 Click here Click here Click here Click here Click hereDRV135 Click here Click here Click here Click here Click here

12.3 TrademarksAll trademarks are the property of their respective owners.

12.4 Electrostatic Discharge CautionThese devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foamduring storage or handling to prevent electrostatic damage to the MOS gates.

12.5 GlossarySLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

Copyright © 1998–2014, Texas Instruments Incorporated Submit Documentation Feedback 19

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.ti.com/lit/ds/symlink/ina134.pdfhttp://www.ti.com/lit/ds/symlink/ina137.pdfhttp://www.ti.com/product/DRV134?dcmp=dsproject&hqs=pfhttp://www.ti.com/product/DRV134?dcmp=dsproject&hqs=sandbuysamplebuyhttp://www.ti.com/product/DRV134?dcmp=dsproject&hqs=tddoctype2http://www.ti.com/product/DRV134?dcmp=dsproject&hqs=swdesKithttp://www.ti.com/product/DRV134?dcmp=dsproject&hqs=supportcommunityhttp://www.ti.com/product/DRV135?dcmp=dsproject&hqs=pfhttp://www.ti.com/product/DRV135?dcmp=dsproject&hqs=sandbuysamplebuyhttp://www.ti.com/product/DRV135?dcmp=dsproject&hqs=tddoctype2http://www.ti.com/product/DRV135?dcmp=dsproject&hqs=swdesKithttp://www.ti.com/product/DRV135?dcmp=dsproject&hqs=supportcommunityhttp://www.ti.com/lit/pdf/SLYZ022http://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

DRV134, DRV135SBOS094B –JANUARY 1998–REVISED DECEMBER 2014 www.ti.com

13 Mechanical, Packaging, and Orderable InformationThe following pages include mechanical, packaging, and orderable information. This information is the mostcurrent data available for the designated devices. This data is subject to change without notice and revision ofthis document. For browser-based versions of this data sheet, refer to the left-hand navigation.

20 Submit Documentation Feedback Copyright © 1998–2014, Texas Instruments Incorporated

Product Folder Links: DRV134 DRV135

http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135http://www.ti.comhttp://www.go-dsp.com/forms/techdoc/doc_feedback.htm?litnum=SBOS094B&partnum=DRV134http://www.ti.com/product/drv134?qgpn=drv134http://www.ti.com/product/drv135?qgpn=drv135

-

PACKAGE OPTION ADDENDUM

www.ti.com 10-Dec-2020

Addendum-Page 1

PACKAGING INFORMATION

Orderable Device Status(1)

Package Type PackageDrawing

Pins PackageQty

Eco Plan(2)

Lead finish/Ball material

(6)

MSL Peak Temp(3)

Op Temp (°C) Device Marking(4/5)

Samples

DRV134PA ACTIVE PDIP P 8 50 RoHS & Green NIPDAU N / A for Pkg Type -55 to 125 DRV134PA

DRV134PAG4 ACTIVE PDIP P 8 50 RoHS & Green NIPDAU N / A for Pkg Type -55 to 125 DRV134PA

DRV134UA ACTIVE SOIC DW 16 40 RoHS & Green NIPDAU Level-3-260C-168 HR DRV134UA

DRV134UA/1K ACTIVE SOIC DW 16 1000 RoHS & Green NIPDAU Level-3-260C-168 HR DRV134UA

DRV134UAE4 ACTIVE SOIC DW 16 40 RoHS & Green NIPDAU Level-3-260C-168 HR DRV134UA

DRV135UA ACTIVE SOIC D 8 75 RoHS & Green NIPDAU Level-3-260C-168 HR -55 to 125 DRV135UA

DRV135UA/2K5 ACTIVE SOIC D 8 2500 RoHS & Green NIPDAU Level-3-260C-168 HR -55 to 125 DRV135UA

DRV135UA/2K5E4 ACTIVE SOIC D 8 2500 RoHS & Green NIPDAU Level-3-260C-168 HR -55 to 125 DRV135UA

DRV135UAG4 ACTIVE SOIC D 8 75 RoHS & Green NIPDAU Level-3-260C-168 HR -55 to 125 DRV135UA

(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substancedo not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI mayreference these types of products as "Pb-Free".RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of

-

PACKAGE OPTION ADDENDUM

www.ti.com 10-Dec-2020

Addendum-Page 2

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuationof the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to twolines if the finish value exceeds the maximum column width.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on informationprovided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken andcontinues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

-

TAPE AND REEL INFORMATION

*All dimensions are nominal

Device PackageType

PackageDrawing

Pins SPQ ReelDiameter

(mm)

ReelWidth

W1 (mm)

A0(mm)

B0(mm)

K0(mm)

P1(mm)

W(mm)

Pin1Quadrant

DRV134UA/1K SOIC DW 16 1000 330.0 16.4 10.75 10.7 2.7 12.0 16.0 Q1

DRV135UA/2K5 SOIC D 8 2500 330.0 12.4 6.4 5.2 2.1 8.0 12.0 Q1

PACKAGE MATERIALS INFORMATION

www.ti.com 30-Dec-2020

Pack Materials-Page 1

-

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

DRV134UA/1K SOIC DW 16 1000 853.0 449.0 35.0

DRV135UA/2K5 SOIC D 8 2500 853.0 449.0 35.0

PACKAGE MATERIALS INFORMATION

www.ti.com 30-Dec-2020

Pack Materials-Page 2

-

www.ti.com

GENERIC PACKAGE VIEW

This image is a representation of the package family, actual package may vary.Refer to the product data sheet for package details.

SOIC - 2.65 mm max heightDW 16SMALL OUTLINE INTEGRATED CIRCUIT7.5 x 10.3, 1.27 mm pitch

4224780/A

-

www.ti.com

PACKAGE OUTLINE

C

TYP10.639.97

2.65 MAX

14X 1.27

16X 0.510.31

2X8.89

TYP0.330.10

0 - 80.30.1

(1.4)

0.25GAGE PLANE

1.270.40

A

NOTE 3

10.510.1

BNOTE 4

7.67.4

4220721/A 07/2016

SOIC - 2.65 mm max heightDW0016ASOIC

NOTES: 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side. 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.5. Reference JEDEC registration MS-013.

1 16

0.25 C A B

98

PIN 1 IDAREA

SEATING PLANE

0.1 C

SEE DETAIL A

DETAIL ATYPICAL

SCALE 1.500

-

www.ti.com

EXAMPLE BOARD LAYOUT

0.07 MAXALL AROUND

0.07 MINALL AROUND

(9.3)

14X (1.27)

R0.05 TYP

16X (2)

16X (0.6)

4220721/A 07/2016

SOIC - 2.65 mm max heightDW0016ASOIC

NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

METAL SOLDER MASKOPENING

NON SOLDER MASKDEFINED

SOLDER MASK DETAILS

OPENINGSOLDER MASK METAL

SOLDER MASKDEFINED

LAND PATTERN EXAMPLESCALE:7X

SYMM

1

8 9

16

SEEDETAILS

SYMM

-

www.ti.com

EXAMPLE STENCIL DESIGN

R0.05 TYP

16X (2)

16X (0.6)

14X (1.27)

(9.3)

4220721/A 07/2016

SOIC - 2.65 mm max heightDW0016ASOIC

NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design.

SOLDER PASTE EXAMPLEBASED ON 0.125 mm THICK STENCIL

SCALE:7X

SYMM

SYMM

1

8 9

16

-

www.ti.com

PACKAGE OUTLINE

C

.228-.244 TYP[5.80-6.19]

.069 MAX[1.75]

6X .050[1.27]

8X .012-.020 [0.31-0.51]

2X.150[3.81]

.005-.010 TYP[0.13-0.25]

0 - 8 .004-.010[0.11-0.25]

.010[0.25]

.016-.050[0.41-1.27]

4X (0 -15 )

A

.189-.197[4.81-5.00]

NOTE 3

B .150-.157[3.81-3.98]

NOTE 4

4X (0 -15 )

(.041)[1.04]

SOIC - 1.75 mm max heightD0008ASMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

NOTES: 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side. 4. This dimension does not include interlead flash.5. Reference JEDEC registration MS-012, variation AA.

18

.010 [0.25] C A B

54

PIN 1 ID AREA

SEATING PLANE

.004 [0.1] C

SEE DETAIL A

DETAIL ATYPICAL

SCALE 2.800

-

www.ti.com

EXAMPLE BOARD LAYOUT

.0028 MAX[0.07]ALL AROUND

.0028 MIN[0.07]ALL AROUND

(.213)[5.4]

6X (.050 )[1.27]

8X (.061 )[1.55]

8X (.024)[0.6]

(R.002 ) TYP[0.05]

SOIC - 1.75 mm max heightD0008ASMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

NOTES: (continued) 6. Publication IPC-7351 may have alternate designs. 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

METALSOLDER MASKOPENING

NON SOLDER MASKDEFINED

SOLDER MASK DETAILS

EXPOSEDMETAL

OPENINGSOLDER MASK METAL UNDER

SOLDER MASK

SOLDER MASKDEFINED

EXPOSEDMETAL

LAND PATTERN EXAMPLEEXPOSED METAL SHOWN

SCALE:8X

SYMM

1

45

8

SEEDETAILS

SYMM

-

www.ti.com

EXAMPLE STENCIL DESIGN

8X (.061 )[1.55]

8X (.024)[0.6]

6X (.050 )[1.27]

(.213)[5.4]

(R.002 ) TYP[0.05]

SOIC - 1.75 mm max heightD0008ASMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

NOTES: (continued) 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 9. Board assembly site may have different recommendations for stencil design.

SOLDER PASTE EXAMPLEBASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

SYMM

SYMM

1

45

8

-

IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265Copyright © 2020, Texas Instruments Incorporated

http://www.ti.com/legal/termsofsale.htmlhttp://www.ti.com

1 Features2 Applications3 Description4 Simplified SchematicTable of Contents5 Revision History6 Pin Configuration and Functions7 Specifications7.1 Absolute Maximum Ratings7.2 Handling Ratings7.3 Recommended Operating Conditions7.4 Electrical Characteristics7.5 Typical Characteristics

8 Detailed Description8.1 Overview8.2 Functional Block Diagram8.3 Feature Description8.3.1 Audio Performance8.3.2 Output Common-Mode Rejection8.3.3 Signal Balance Ratio

8.4 Device Functional Modes8.4.1 Differential-Output Mode8.4.2 Single-Ended Mode

9 Application and Implementation9.1 Application Information9.2 Typical Application9.2.1 Cable Driving Application9.2.1.1 Design Requirements9.2.1.2 Detailed Design Procedure9.2.1.3 Application Curve

10 Power Supply Recommendations11 Layout11.1 Layout Guidelines11.2 Layout Examples11.3 Thermal Performance

12 Device and Documentation Support12.1 Documentation Support12.1.1 Related Documentation

12.2 Related Links12.3 Trademarks12.4 Electrostatic Discharge Caution12.5 Glossary

13 Mechanical, Packaging, and Orderable Information

![CHARAKTERYSTYKI STAŁOPRĄDOWE … · dsp =β p V in −V DD −V tp] 2 [( ) 2 1 2 out dsn n in tn out V I =βV −V V ...](https://static.fdocument.org/doc/165x107/5b96032409d3f2d7438d1c5c/charakterystyki-stalopradowe-dsp-p-v-in-v-dd-v-tp-2-2-1-2.jpg)