Design Status for SW- EMR (Electron Muon Ranger : e μ R ) Gianrossano Giannini, Pietro Chimenti,

description

Transcript of Design Status for SW- EMR (Electron Muon Ranger : e μ R ) Gianrossano Giannini, Pietro Chimenti,

1

Design Status for SW- EMR(Electron Muon Ranger : eμR)

Gianrossano Giannini, Pietro Chimenti,Erik Vallazza, Stefano Reia (M.T.), Dario Iugovaz(M.T.),

Mauro Bari(E.T.), Giulio Orzan(E.T.)Trieste INFN and Trieste University- Physics Department

+Michela Prest, Valerio Mascagna&( Michela’s Boys&Girls:Andrea, Daniela, Davide, Said)

(Como Univ. and INFN-MiB)MICE-CM22 @RAL, October 19, 2008

2

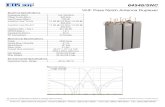

The bars will be made with the Minerva die set which gives a triangle with a base of 33mm and height of 17 mm nominal.

Alan Bross

Each layer 59 triangular bars: 30 triangular bars x 33 mm =990 mm + 29 matching triangular bars

Each layer Active Scintillator region :990 mm x 990 mm x 17 mm

Thickness ~17 mm

Total=17 mm x 40 layers = 680 mm

Half triangular edge mechanical elements

3

4

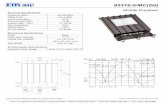

Longitudinal Segmentation:40 layers with no longitudinalinformation loss.

Tranverse Segmentation:Alternating horizontal/vertical layers59 scintillator bars /layerX 40 layers = 2360 scint. bars59 bars on 64 channels (=26) Tot. 2560 channels

Available PMT’s in Trieste:18 +(2 in prototype)= 20 x 64 ch. Hamamatsu R7600-03-M64+ 2x256 ch. Hamamatsu H9500-M256Available channels= 64x20 +2*256= 1280+512 = 1536 (< 2560)

Proposed grouping:32 layers 32 M64 (= 1 per layer) 1 scint.bar per channel 8 layers 2 M256 (= 1 per 4 layers) 1 scint.bar per channel

Needed electronics: 64x32 +256x2=2560 channels of digital pattern(+ at least from last PMT dynodes 34 channels of analog information)

5

Proposal for the electronics of the MICE EMREMR group (Michela Prest, Erik Vallazza, JSG, GG et al)

October 14, 2008

This proposal describes the frontend and readout electronics of theMICE EMR detector.

The main features of the EMR detector can be summarized as follows:

• EMR will consist of 40 layers of 59 extruded scintillator bars with a triangular shape

• each bar is interfaced with a multianode PMT through 4 WLS fibers (0.8 mm diameter); in total there will be 32 64-channel PMTs (Hamamatsu, H7645B) and 2 256-channels PMTs (Hamamatsu, H9500). In future there might be 40 64-channel PMTs

• to obtain an indication on the charge deposit in each layer, the analog signal of each PMT dynode will be digitized with a CAEN V1731; this will require 3 digitizers for the whole detector. With the foreseen electronics it is not possible to obtain the analog information of every bar without introducing dead time (see later on)

• the frontend electronics will allow to obtain a digital information for every bar, that is thetime when the bar signal is over threshold

• the system will not work in self triggering mode; the trigger will be given by an externaldetector or by the machine itself

6

General layout of the EMR electronics. 1-The frontend electronics Organized in piggy back boards (overall called FEB, Front-End-Board):

• FEB-ASIC (located inside the detector box) - It will host the PMT (through a dedicated socket), the two frontend ASICs (VA64TAP3 and LS64 2) and the Altera CYCLONE III for the ASICs digital output handling.- The FEB-ASIC will be connected directly to the digital configuration board in the VME crate, to the FEB-MEM and to the FEB-ADC

• FEB-MEM hosting the memory to store the data collected during the spill

• FEB-ADCused for the acquisition of the analog information from every bar. This last block is used to test that all the ASICs are correctly working.

• FEB-CAL is the frontend block responsibleof the calibration: the side of every bar not interfaced with the PMT will be equipped with an LED for calibration and test purposes.

7

1.1 The FEB-ASICThe ASICsGiven the integrated charge generated by a single photoelectron (considering a PM gain of the order of 105), a low noise amplification stage and a discriminator on the same die are needed to treat the PM signals.The frontend chain will be based on the VA64TAP3 + LS64 2 ASICs (Gamma Medica - Ideas (Norway), http://www.ideas.no). The VA64TAP3 is a 64 channel low noise ASIC built in 0.35 µm N-well CMOS double poly triple metal technology.

8

9

Low power low noise ASIC with 64 identical channels consisting of a preamplifier, a fast CR-RC shaper, a tunable threshold discriminator, a multiplexed analog output stage and a parallel digital output one. The shaper has a peaking time in the range 50-75 ns; the pole-zero cancellation circuit allows to minimize the pileup effects in the preamplifier and the shaper itself. Each channel has a discriminator with a general threshold and a 4-bit trim DAC for each channel to limit the threshold spread. If the channel is not disabled, the discriminator outputs triggers a monostable circuit whose width can be adjusted (but is not related to the time the signal stays over threshold). The ASIC has 64 parallel trigger outputs which are open drain requiring to be terminated to avoid noise pick-up. These outputs can be directly connected to the input of the LS64 ASIC, whose main task is the level shifting of these lines in order to feed them to the FPGA; the signals are converted to low voltage TTL (LV-TTL). The LS64 2 ASIC has 64 inputs and 64 outputs and requires only the bias for its operation. The ASICs bonded on the frontend prototype are shown in fig. 3. The output of the shapers can be connected to an analog output buffer to read the analog information collected by the detector. In this case a hold signal has to be generated to sample the shaper output at its maximum. The readout is a multiplexed one with a maximum readout clock of 10 MHz. The ASICs can be daisy-chained. This analog readout feature will be used in the test phase.The ASIC has also a trigger output which is the OR of the discriminator outputs allowing to work in self triggering mode during the commissioning phase. A dedicated trigger board will process all the planes trigger outputs in order to run in self triggering mode the system.

10

The FEB-ASICIt will host a dedicated socket for the H7645B, the pair of ASICs and an Altera Cyclone III FPGA to organize the digital info produced by the ASICs.

A 20 MHz quartz is used as a clock reference.

Two Phase-Locked Loops (PLLs) clock generators with a maximum multiplier factor of 32 can provide the up-to-640 MHz clock needed for the fast sampling.

The 64 LS64 2 output lines enter directly in the FPGA that organizes the bits in order to send them to the FEM-MEM (that cannot sample at the same high speed).

The FEB-MEM communicates only with the Altera of the FEB-ASIC. The FPGA organizes the bits as they arrive from the ASICs serializing them and stores them in the RAM on this board during the spill.

At the moment, we are considering to sample at 250 MHz and to have a RAM large enough to store 512 ksample, meaning we can store 2 ms at 250 MHz or 1 ms at 500 MHz.In the inter-spill period, a fast link connection between the FEB-ASIC and the readout electronics allows the transfer at 1 GB/s. Considering 512k words of 64 bit each, this will require 33 ms for the transfer. A dedicated hardware procedure in the readout receiving board will perform the zero-suppression to reduce the amount of data to save on disk.

11

1.2 The FEB-CALA dedicated calibration system is foreseen for the commissioning phase.

An LED will be housed in each bar on the opposite side with respect to the one where the fibers are interfaced to the PMT.

The LEDs will be controlled by a dedicated board allowing to check the map of the connections bar- PMT-ASIC channels and to perform the threshold scans to obtain the gain and offset spread of the electronics channels.

As far as the threshold scan is concerned, a scaler array will be implemented in the Cyclone III FPGA to count the number of detected pulses as a function of the threshold value, lighting one channel after the other.

12

1.3 The FEB-ADCThe VA64TAP3 is also an analog ASIC allowing to compute the charge released by the particle in the scintillating bars. The analog output is a multiplexed one as shown in fig. 4. A hold signal is generated once the trigger has been received to sample the shaper output, while the shift in signal starts the readout which can stand a maximum clock frequency of 10 MHz. A dedicated FPGA in this board will contain the state machine to generate the readout sequence. The 12-bit ADC will be hosted on this same board. The ADC digital outputs will be sent to the readout crate via a dedicated fast link. A protoype of this board is already under test. The expected deadtime is expected to be less than 20 µs. This mode will be fundamental during the commissioning phase.

13

2 The readout electronicsApart from the CAEN digitizers, all the readout boards are VME custom boards designed by INFN Trieste.

14

40 layers= 20 +8(4x2)+12(4x3)

15

21 groupingnormal single tracksSingle layer digital pattern resolution Still: 33mm/2/sqrt(12) ~ 5 mm

No grouping:normal single trackssingle layer digital pattern resolution 33mm/2/sqrt(12) ~ 5 mm

16

31 groupingnormal single trackssingle layer digital pattern resolution Still: 33mm/sqrt(12) ~ 10 mm

31 groupingnormal single tracksstaggered double layer digital pattern resolution Again: 33mm/2/sqrt(12) ~ 5 mm

17

Construction time estimate:

2 layers per week 40 layers in 20 weeks = ~ 5-6 months

In case one wants no grouping at all and 1 waveform digitizer per layer:

20 more M64 PMT’s are needed (cost = 20 x 1600 Euro = 32 k Euro)

Total 40 WFD chs.

18

19