CUARTA UNIDAD : EL AMPLIFICADOR … en estos amplificadores prima mantener las características a...

Transcript of CUARTA UNIDAD : EL AMPLIFICADOR … en estos amplificadores prima mantener las características a...

R10

+

C4

D

6

R9

+ C3

D5

-VCC

VCC

Q4

Q3

D1

D2

D3

D4

Q1

Q2

V2

V1

+ U2 C2 + U1 C1

1kH

z

Vi -

1/1V 8Ω

R3

R

R

R7

R8

R5

R4

R6

R2

R1

2010

Felipe Isaac Paz Campos

UNI

12/10/2010

CUARTA UNIDAD : EL AMPLIFICADOR OPERACIONAL(OP-AMP)

A

B

B B

C

D

E

91

CAPÍTULO 6 EL AMPLIFICADOR

OPERACIONAL (OP-AMP).

6.1 Introducción

El amplificador operacional

(habitualmente llamado OP-AMP) es un

circuito electrónico (normalmente se

presenta como circuito integrado) que

tiene dos entradas y una salida. La salida

es la diferencia de las dos entradas

multiplicada por un factor (A) (ganancia):

Vout = A (V+ − V−).

El primer amplificador operacional

monolítico data de los años 1960, era el

Fairchild μA702 (1964), diseñado por

Bob Widlar. Le siguió el Fairchild μA709

(1965), también de Widlar, y que

constituyó un gran éxito comercial. Más

tarde sería sustituido por el popular

Fairchild μA741(1968), de David

Fullagar, y fabricado por numerosas

empresas, basado en tecnología bipolar.

Originalmente los OP-AMP se

empleaban para operaciones matemáticas

(suma, resta, multiplicación, división,

integración, derivación, etc) en

calculadoras analógicas. De ahí su

nombre.

6.2 El OP-AMP IDEAL

El OP-AMP ideal tiene una ganancia

infinita(A), una impedancia de entrada

infinita(Zi), un ancho de banda también

infinito(BW), una impedancia de salida

nula(Zo), un tiempo de respuesta nulo y

ningún ruido. Como la impedancia de

entrada es infinita, también se dice que la

corriente de entrada (Ii) es cero.

6.3 Símbolo

El símbolo de un MONOLITICO es el

mostrado en la figura 6.1.

En la figura 6.1 las terminales son:

V+ : Entrada no inversora

V-: Entrada inversora

Vout: Voltaje de salida

+VS: Voltaje de alimentación positiva

-VS: Voltaje de alimentación negativa

Las terminales de alimentación pueden

recibir diferentes nombres, por ejemplo

en los OP-AMP basados en FET se les

llama VDD y VSS respectivamente. Para

los basados en BJT son VCC y VEE.

Normalmente los pines de alimentación

son omitidos en los diagramas eléctricos,

figura 6.2.

6.4 Comportamiento del OP-AMP en

continua (DC)

Se explicará el comportamiento del OP-

AMP en DC para cuando se tiene lazo

abierto y lazo cerrado.

6.4.1 Lazo abierto

Si no existe realimentación la salida del

OP-AMP será la resta de sus dos entradas

multiplicada por un factor. Este factor

suele ser del orden de 100.000 (que se

considerará infinito en cálculos con el

componente ideal). Por lo tanto si la

diferencia entre las dos tensiones es de

1V la salida debería ser 100V. Debido a

la limitación que supone no poder

+

V+

V-

Vout

-VS

+VS

+

Figura 6.1

Figura 6.2

92

entregar más tensión de la que hay en la

alimentación, el OP-AMP estará

saturado si se da este caso. Si la tensión

más alta es la aplicada a la patilla +, la

salida será la que corresponde a la

alimentación +VS, mientras que si la

tensión más alta es la de la patilla -, la

salida será la alimentación -VS.

6.4.2 Lazo cerrado

Se conoce como lazo cerrado a la

realimentación en un circuito. Aquí se

supondrá realimentación negativa. Para

conocer el funcionamiento de esta

configuración, se parte de las tensiones en

las dos entradas exactamente iguales, se

supone que la tensión en la patilla + sube

y, por tanto, la tensión en la salida

también se eleva. Como existe la

realimentación entre la salida y la patilla -

, la tensión en esta patilla también se

eleva, por tanto la diferencia entre las dos

entradas se reduce, disminuyéndose

también la salida. Este proceso pronto se

estabiliza y se tiene que la salida es la

necesaria para mantener las dos entradas,

idealmente, con el mismo valor.

Siempre que hay realimentación negativa

se aplican estas dos aproximaciones para

analizar el circuito:

V+ = V-

I+ = I- = 0

6.5 Comportamiento del OP-AMP en

alterna (AC)

En principio la ganancia calculada para

continua puede ser aplicada para alterna,

pero a partir de ciertas frecuencias

aparecen limitaciones.

6.6 Parámetros DEL OP-AMP

Ganancia en lazo abierto. Indica la

ganancia de tensión en ausencia de

realimentación. Se puede expresar en

unidades naturales (V/V, V/mV) o

logarítmicas (dB). Son valores habituales

100.000 a 1.000.000 V/V.

Tensión en modo común. Es el valor

medio de tensión aplicado a ambas

entradas del operacional.

Tensión de Offset. Es la diferencia de

tensión, aplicada a través de resistencias

iguales, entre las entradas de un

operacional que hace que su salida tome

el valor cero.

Corriente de Offset. Es la diferencia de

corriente entre las dos entradas del

operacional que hace que su salida tome

el valor cero.

Margen de entrada diferencial. Es la

mayor diferencia de tensión entre las

entradas del operacional que mantienen el

dispositivo dentro de las especificaciones.

Corrientes de polarización de entrada.

Corriente media que circula por las

entradas del operacional en ausencia de

señal.

Slew rate. Velocidad de cambio de la

tensión de salida ante un escalón a la

entrada. Se mide en V/μs, kV/μs o

similares.

Rechazo de Rizado en modo común.

Relación entre la variación de la tensión

de offset y el valor de la tensión en modo

común. Se mide en dB.

6.7 Limitaciones DEL OP-AMP

Saturación

Un OP-AMP típico no puede suministrar

más de la tensión a la que se alimenta,

normalmente algunos voltios menos.

Cuando se da este valor se dice que se

satura, pues ya no está amplificando.

93

La saturación puede ser aprovechada por

ejemplo en circuitos comparadores. Un

concepto asociado a éste es el Slew rate.

Tensión de offset

Es la diferencia de tensión que se da entre

sus dos patillas de entrada cuando la

tensión de salida es nula. Se puede

expresar su dependencia de la

temperatura (T) como:

)()( OOFFSET

OOFFSETOFFSET TTT

VTVV (6.1)

Donde T0 es una temperatura de

referencia.

Una característica derivada de ésta es el

PSRR que se expresa como:

1 OFFSET

CC

V

PSRR V (6.2)

Capacidades

El OP-AMP presenta capacitancias

parásitas, las cuales producen una

disminución de la ganancia conforme

aumenta la frecuencia.

Característica Tensión-Frecuencia.

Al OP-AMP típico también se le conoce

como amplificador realimentado en

tensión (VFA). En él hay una importante

limitación respecto a la frecuencia: El

producto de la ganancia en tensión por el

ancho de banda es constante.

Como la ganancia en lazo abierto es del

orden de 100.000, un amplificador con

esta configuración sólo tendría un ancho

de banda de unos pocos Hercios. Al

realimentar negativamente se baja la

ganancia a valores del orden de 10 a

cambio de tener un ancho de banda

aceptable. Existen modelos de diferentes

OP-AMP para trabajar en frecuencias

superiores, en estos amplificadores prima

mantener las características a frecuencias

más altas que el resto, sacrificando a

cambio un menor valor de ganancia u otro

aspecto técnico.

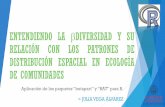

6.8 Estructura del OP-AMP.

Aunque es usual presentar al OP-AMP,

como una caja negra con características

ideales es importante entender la forma en

que funciona, de esta forma se podrá

entender mejor las limitaciones que

presenta.

Los diseños varían entre cada fabricante y

cada producto, pero todos los OP-AMP,

tienen básicamente la misma estructura

interna, que consiste en tres etapas:

a.- Amplificador diferencial: es la etapa

de entrada que proporciona una baja

amplificación del ruido y gran

impedancia de entrada. Suelen tener una

salida diferencial.

b.- Amplificador de tensión: proporciona

una ganancia de tensión.

c.- Amplificador de salida: proporciona la

capacidad de suministrar la corriente

necesaria, tiene una baja impedancia de

salida y, usualmente, protección frente a

cortocircuitos.

En la figura 6.3 se muestra la estructura

del OP-AMP LM741.

En el diagrama de la figura 6.3 se destaca:

La etapa de la parte A el amplificador

A

B

B B

C

D

E

Figura 6.3

94

diferencial. Éste es el responsable de que

las corrientes de entrada no sean cero,

pero si respecto a las de los colectores

(Nótese como a pesar de aproximar las

corrientes de entrada a 0, si éstas

realmente fueran 0 el circuito no

funcionaría). La impedancia de entrada es

de unos 2MΩ.

Las etapas de la parte B son espejos de

corriente. El superior de la izquierda sirve

para poder soportar grandes tensiones en

modo común en la entrada. El superior

de la derecha proporciona una corriente a

la circuitería de salida para mantener la

tensión. El inferior tiene una baja

corriente de colector debido a las

resistencias de 5kΩ. Se usa como

conexión de gran impedancia a la

alimentación negativa para poder tener

una tensión de referencia sin que haya

efecto de carga en el circuito de entrada.

Los pines llamados Offset null son usados

para eliminar las tensiones de offset que

pueda haber en el circuito.

La etapa de ganancia en tensión es NPN.

La sección de la parte C es un

desplazador de tensión. Esto proporciona

una caída de tensión constante sin

importar la alimentación. En el ejemplo

1V. Esto sirve para prevenir la distorsión.

El condensador se usa como parte de un

filtro paso bajo para reducir la frecuencia

y prevenir que el OP-AMP oscile.

La salida en la parte D es un amplificador

PNP seguidor con emisor push-pull. El

rango de la tensión de salida es de un

voltio menos a la alimentación, la tensión

colector-emisor de los transistores de

salida nunca puede ser totalmente cero.

Las resistencias de salida hacen que la

corriente de salida esté limitada a unos

25mA. La resistencia de salida no es cero,

pero con realimentación negativa se

aproxima.

6.9 Diferentes encapsulados

En la figura 6.4 se muestran dos de los

encapsulados más comunes utilizados

para los OP-AMP.

6.10 Análisis de circuitos con OP-AMP.

Para analizar un circuito en el que haya

OP-AMP, este análisis se hará

considerando las Características ideales

del OP-AMP.

Zi →∞; Zo→0Ω; A→∞;

V+ = V- Si existe realimentación.

6.11 Aplicaciones del OP-AMP

Debido a la sencillez con que funciona un

OP-AMP, existe un número inmenso de

aplicaciones, que las podemos dividir en

dos grandes grupos: aplicaciones lineales

y aplicaciones no lineales.

6.11.1 Aplicaciones Lineales.

En las aplicaciones lineales se debe

garantizar retroalimentación negativa,

para que el OP-AMP se comporte como

un amplificador. Para que exista

retroalimentación negativa en OP-AMP el

lazo de retroalimentación se debe dar por

el pin inversor (V-).

Figura 6.4

95

a.- Amplificador inversor.

El análisis del circuito de la figura 6.5 es

el siguiente:

V+ = V- = 0V (6.3)

Definiendo corrientes:

221 IIII i (6.4)

Ya que Ii = 0A

21

00

R

vV

R

Vv oi (6.5)

Despejando vo de (6.5):

1

2

R

Rvv io (6.6)

Se denomina amplificador inversor ya

que la señal de salida es igual a la señal

de entrada (en forma) pero con la fase

invertida 180 grados.

1

1

1

R

R

v

v

I

vZ

i

iii (6.7)

De la ecuación (6.7) se observa que se

puede controlar la impedancia de entrada

mediante la elección de R1.

Esta configuración es una de las más

importantes, porque gracias a esta

configuración, se puede elaborar otras

configuraciones, como la configuración

del derivador, integrador, sumador etc.

b.- Amplificador no inversor.

El análisis del circuito de la figura 6.6 es

el siguiente:

V+ = V- = Vi (6.8)

Definiendo corrientes:

221 IIII i (6.9)

Ya que Ii = 0A

21

0

R

vv

R

vV oii (6.10)

Despejando vo de (6.10):

io vR

Rv )1(

1

2 (6.11)

A

v

I

vZ i

i

ii

0 (6.12)

c.- Amplificador Sumador.

I1

I2

Ii

V

vo 1kHz

vi

-1/1V

R2

R1 +

1kHz

-1/1V +

Figura 6.5

1kHz

-1/1V

+

1kHz

-1/1V

+

I1 vi

R1

R2

I2

Ii vo

V

Figura 6.6

R3

1kHz

V3 -1/1V

R2

1kHz

V2 -1/1V

Vo

1kHz

V1 -1/1V

+

R4

R1

1kHz

-1/1V

1kHz

-1/1V

1kHz

-1/1V

+

I1

I2

I3

I4 Ii V

Figura 6.7

96

El análisis del circuito de la figura 6.7 es

el siguiente:

V+ = V- = 0V (6.13)

Definiendo corrientes:

4321 IIIII i (6.14)

Ya que Ii = 0A

4321 IIII (6.15)

Aplicando la ley de ohm:

43

3

2

2

1

1

R

V

R

V

R

V

R

V o

Despejando Vo:

)( 3

3

42

2

41

1

4 VR

RV

R

RV

R

RVo (6.16)

Si R1=R2=R3=R4 Entonces:

)( 321 VVVvo (6.17)

d.- Amplificador Substractor.

El análisis del circuito de la figura 6.8 es

el siguiente:

Calculando el voltaje de salida por medio

del método de superposición:

21 ooo VVV (6.18)

Donde el Vo1 es la contribución de V1 y

Vo2 es la contribución de V2.

Para calcular Vo1 se apaga V2 y se deja V1

Con V2 = 0V → V’ =V= 0V (6.19)

221 IIII i (6.20)

Con Ii=0A y aplicando la ley de ohm en

la ecuación (6.20):

2

1

1

1

R

V

R

V o Entonces:

1

1

21 V

R

RVo (6.21)

Para calcularVo2 se apaga V1 y se deja V2

21

22'

RR

RVV (6.22)

21

12

RR

RVV o (6.23)

Ya que: VV ' Entonces:

21

12

1

22

2RR

RV

RR

RV o

(6.24)

Despejando Vo2 se obtiene:

2

1

22 V

R

RVo (6.25)

Sustituyendo (6.21) y (6.25) en (6.18):

)( 12

1

2 VVR

RVo (6.26)

6.11.1.1 EJEMPLOS 6.A

Ejemplo # 1

Para el circuito mostrado en la figura 6.9,

calcule Vo.

V

Ii

I2

I1

V’

R2

R1

1kHz

V2 -1/1V

Vo 1kHz

V1

-1/1V +

R2

R1

1kHz

-1/1V

1kHz

-1/1V +

Figura 6.8

97

El análisis del circuito de la figura 6.9 es

el siguiente:

V+ = V- = 0V (6.27)

Definiendo corrientes:

4321 IIIII i (6.28)

Ya que Ii = 0A

4321 IIII (6.29)

Aplicando la ley de ohm:

43

3

2

2

1

1

R

V

R

V

R

V

R

V o (6.30)

Despejando Vo:

)( 3

3

42

2

41

1

4 VR

RV

R

RV

R

RVo (6.31)

Sustituyendo valores:

)35

105

5

102

5

10( V

k

kV

k

kV

k

kVo

VVo 20 Matemáticamente, este sería

el voltaje de salida, pero eléctricamente

esto es imposible, ya que el circuito se

alimenta con 15V. Por lo tanto el voltaje

de salida es VVo 15

Ejemplo # 2

Para el circuito mostrado en la figura 6.10

calcule Vo.

Vkkk

kkVV 1

10)1//10(

)1//10(121 (6.32)

Vk

kVxVo 10)

1

10(1 (6.33)

Ejemplo # 3

El circuito mostrado en la figura 6.11 es

un convertidor digital analógico calcule

Vo para cada una de las combinaciones

posibles en su entrada.

R

VI

f

f

Re

Re (6.35)

2

Re

3

fII (6.36)

42

Re32

fIII (6.37)

82

Re21

fIII (6.38)

162

Re1 f

o

III (6.39)

R3

1kHz

V3 3Vp

R2

1kHz

V2 5Vp

Vo

1kHz

+

R4

R1

1kHz

1kHz

1kHz

2Vp

+

I1

I2

I3

I4

Ii V 5kΩ

5kΩ

5kΩ

10kΩ

15V

0V

Figura 6.9

Vo

15V

R4 10kΩ

R2 10kΩ

R1 10kΩ

R3 1kΩ +

12V

+ V1

Figura 6.10

IRef I3 I2 I1

Io I1

I2 I3

Vo

-15V

15V RF

10kΩ

+

Do=LSB D1 D2 D3=MSB

+ VRef

10V

R=10kΩ

2R 2R

2R 2R 2R

20kΩ

+

+

R=10kΩ R=10kΩ

20kΩ 20kΩ

20kΩ

20kΩ

Isal

Figura 6.11

V1

98

Fsalo RIV (6.40)

xDresoluciónI sal )( (6.41)

R

Vxresolución

f

n

Re

2

1 (6.42)

xDRxR

VV Fn

f

o )2

1(

Re (6.43)

En la tabla 6.1 se muestra Vo. Entrada digital Entrada Voltaje de salida

D3 D2 D1 Do decimal

xDRxR

VV Fn

f

o )2

1(

Re

0 0 0 0 0 0V

0 0 0 1 1 -0.625V

0 0 1 0 2 -1.25V

0 0 1 1 3 -1.875V

0 1 0 0 4 -2.5V

0 1 0 1 5 -3.125V

0 1 1 0 6 -3.75V

0 1 1 1 7 -4.375V

1 0 0 0 8 -5V

1 0 0 1 9 -5.625V

1 0 1 0 10 -6.25V

1 0 1 1 11 -6.875V

1 1 0 0 12 -7.5V

1 1 0 1 13 -8.125V

1 1 1 0 14 -8.75V

1 1 1 1 15 -9.375V

Tabla 6.1

Ejemplo # 4

Para el circuito mostrado en la figura

6.12, calcule Vo.

21 ooo VVV (6.44)

IxREVo 21 (6.45)

IxREVo 12 (6.46)

aR

EEI 21 (6.47)

Sustituyendo (6.47) en (6.46) y en (6.45):

a

E

aExR

aR

EEEVo

12

2121 )

11( (6.48)

a

E

aExR

aR

EEEVo

21

2112 )

11( (6.49)

Sustituyendo (5.47) y (5.48) en (5.43):

a

E

aE

a

E

aEVo

21

12 )

11()

11(

)2

1)(( 12a

EEVo (6.50)

6.11.2 Aplicaciones no Lineales.

a.- Derivador ideal

Deriva e invierte la señal respecto al

tiempo.

dt

dvRCV i

o (6.51)

b.- Oscilador puente de Wien

AR

R

V

V

a

o 11

2 (6.52)

aR

E2

E1

+

-

Vo E1>E2

R

R

+

+

+

+

I

Vo1

Vo2

Figura 6.12

V C

Vo 1kHz

Vi

-1/1V +

R

1kHz

-1/1V +

Figura 6.13

Va R C

R C

Vo

+

R2

R1 +

Figura 6.14

99

SC

SCR

SCR

RSCR

R

V

V

o

a

1

1

1 (6.53)

Para garantizar la oscilación se debe

cumplir:

CRfo

2

1 (6.54)

21

2

R

R (6.55)

c.- Comparadores de Voltaje:

Voltaje de Referencia en pin

inversor y voltaje de entrada en

pin no inversor, figura 6.15.

Si Vi < VRef →Vo = -VCC+Vperd

Si Vi ≥ VRef →Vo = VCC-Vperd

Donde Vperd ≈ 1V Máximo. En la

mayoría de los casos se considera este

voltaje despreciable y el voltaje de salida

es:

Vo = VCC o Vo = -VCC según sea el caso.

Voltaje de Referencia en pin no

inversor y voltaje de entrada en

pin inversor, figura 6.16.

Si Vi < VRef →Vo = VCC-Vperd

Si Vi ≥ VRef →Vo = -VCC+Vperd

En algunas aplicaciones no es

conveniente usar comparadores de

voltajes con operacionales, cuando se

necesita rapidez en la respuesta de

salida. Los amplificadores operacionales

son un poco lento debido a su pequeña

capacitancia interna de

aproximadamente 10pF. En estos casos

se deben usar comparadores específicos.

Comparadores específicos:

LM 311, LM306, LM 393, LM 339 (4

comparadores de voltaje).

LM 311 (colector abierto)

Voltaje de Referencia en pin no

inversor y voltaje de entrada en

pin inversor, figura 6.17.

Si Vi ≥ VRef →Vo = -VCC

Si Vi < VRef →Vo = Cto abierto

Voltaje de Referencia en pin

inversor y voltaje de entrada en

pin no inversor, figura 6.18.

-VCC

VCC

VRef

Vi

Vo

+ +

Figura 6.17

-VCC

VCC

VRef

Vi Vo

+ +

Figura 6.15

-VCC

VCC

Vi

VRef Vo

+ +

Figura 6.16

100

Si Vi ≥ VRef →Vo = Cto abierto

Si Vi < VRef →Vo = -VCC

Debido que Cto abierto no es ningún

estado lógico, hay que agregar una

resistencia en el pin de salida, figura 6.19.

Si Vi ≥ VRef →Vo = -VCC

Si Vi < VRef →Vo = V

Si invertimos las entradas, figura 6.20.

Si Vi ≥ VRef →Vo = V

Si Vi < VRef →Vo = -VCC

Inconvenientes de los comparadores de

voltaje.

Estos inconvenientes se presentan en los

comparadores de voltaje con OP-AMP o

con los compradores específicos, Figura

6.21.

En el gráfico de la figura 6.21 se nota que

el voltaje de salida oscila en los falsos

puntos de disparo debido a la distorsión

de la señal de entrada.

Para esto existe una solución dada por

Schmitt Trigger, mostrada en la siguiente

figura 6.22.

Punto de disparo1 (Vref1)

Vi

Falsos puntos

de disparos

Vo

t

t

Punto de disparo2 (Vref2)

Figura 6.22

Punto de disparo (Vref)

Vi

Falsos puntos

de disparos

Vo

t

t Figura 6.21

V

R

-VCC

VCC

Vi

VRef

Vo

+ +

Figura 6.20

-VCC

VCC

VRef

Vi Vo

+ +

Figura 6.18

V

R

-VCC

VCC

Vi

VRef Vo

+ +

Figura 6.19

101

El circuito electrónico para esta solución

se muestra en la figura 6.23.

Si Vi < VRef →Vo = 0V

132

3211Re

//

//

RRR

RRVV CCf (6.56)

Si Vi ≥ VRef →Vo = V

312

12

132

3212Re

//

//

//

//

RRR

RRV

RRR

RRVV CCf (6.57)

El valor de R3>>R2

El resistor R4 depende de la carga, el

valor oscila entre 470Ω a 2.2kΩ.

Utilizándose un valor típico de 1kΩ.

6.12 EJEMPLOS 6.B

Ejemplo # 1

Para el circuito de la figura 6.24 calcule

VRef1, VRef2 y dibuje la forma de onda del

voltaje de salida.

De la ecuación (6.56) se obtiene:

kk

kV

RRR

RRVV CCf

1076.4

76.415

//

//

132

3211Re

VV f 84.41Re

De la ecuación (5.57) se obtiene:

312

12

132

3212Re

//

//

//

//

RRR

RRV

RRR

RRVV CCf

Vkk

kxVV f 23.5

10033.3

33.31284.42Re

La forma de onda del voltaje de salida se

muestra en la figura 6.25.

Ejemplo # 2

Para el circuito de la figura 6.26, calcule

cuando se enciende el diodo LED. Vi es

un voltaje ac que varía de -10V hasta

10V.

En la figura 6.26:

Si Vi ≥ VRef →Vo = VCC-Vperd

Considerando Vperd despreciable, el

voltaje de salida es 15V.

Esto significa que el diodo LED se

enciende justamente cuando Vi= 5V.

Vi

VCC1 R3

R2

R1

V

VCC2

Vo

+

R4

+

Figura 6.23

Vi

20V

-20V

4.84V

5.23V

12V

0V

Vo

Figura 6.25

Vi

VCC1=15V R3

R2

R1

V=5V

VCC2=12V

Vo

+

R4

+

10kΩ

5kΩ

100kΩ

Vi

20V

-20V

Figura 6.24

D1 LED1

-15V

15V

10V

Vi

+

R3

R1

D1 LED1

Vi

+

1kΩ

1kΩ

Figura 6.26

1kΩ

1kΩ

102

Ejemplo # 3

Para el circuito de la figura 5.27 Explique

cómo funciona. Realice los cálculos

necesarios.

n

Vsat

m

VV

f

f

Re

1Re (6.58)

m

V

n

VV

fsat

f

Re

2Re )( (6.59)

)(Re

Vctr

Vm

f (6.60)

))(

(H

satsat

V

VVn (6.61)

1Re2 frefH VVV (6.62)

m

VVVV

fff

ctr

Re1Re2Re

2 (6.63)

Sustituyendo valores en (6.61):

66.810

6.86

k

kn

Sustituyendo valores en (6.60):

25.110

5.12

k

km

Sustituyendo valores en (6.58):

VVV

V f 38.1066.8

14

25.1

151Re

Sustituyendo valores en (6.59):

VVV

V f 62.1325.1

15

66.8

142Re

Sustituyendo valores en (6.62):

VVVVH 24.338.1062.13

Sustituyendo valores en (6.63):

VV

V

m

VV

f

ctr 1225.1

15Re

Funcionamiento del circuito: Lo que se

muestra en la figura 6.27 es un cargador

de batería automático. Cuando la batería

se descarga a 10.38V a la salida del

comparador de voltaje hay un voltaje

positivo, esto hace que el transistor se

sature, activando el relé e iniciando la

carga de la batería.

Cuando la batería se carga a 13.62V a la

salida del comparador de voltaje hay un

voltaje negativo llevando a la zona de

corte al transistor, desactivando el relé

deteniendo la carga de la batería.

PROBLEMAS

6.1 Para el circuito mostrado en la figura

P5.1, determinar IL en función de Vi.

6.2 Para el circuito mostrado en la figura

P6.2, determinar i

o

V

V.

6.3 Para el circuito mostrado en la figura

P6.3, determinar i

o

V

V.

RL

R4 1kΩ

R3 2kΩ

R2 2kΩ

R5

1kΩ R1 2kΩ

Vi

+ + + +

IL

Figura P6.1

Vo

R4

R3

R1

Vi

+ +

Figura P6.2

mR=12.5kΩ

n:1

1kHz Vi

-170/170V

12V

R 10kΩ

-15V

15V

10kΩ

+ 12V

+ 1kHz

+ +

nR=86.6kΩ

Figura 6.27

R2

103

6.4 Para el circuito mostrado en la figura

P6.4, determinar Vo.

6.5 Para el circuito mostrado en la figura

P6.5, determinar Vo. Considere E1>E2.

5.6 Para el circuito mostrado en la figura

P5.6, determinar Vo.

6.7 Utilizando amplificadores

operacionales diseñe un circuito para

realizar la medición entre colector-Emisor

(VCE) en un amplificador común,

mostrado en la figura P6.7.

6.8 Utilizando amplificadores

operacionales diseñe un circuito para

obtener 3412 VVbVVaVo .

6.9 Calcule los valores de los resistores

del circuito de la figura P6.8 para obtener

un voltaje de salida, tal como se muestra

en el gráfico de la figura P6.8.1.

Punto de disparo1 (Vref1) Vi

Vo

t

t

Punto de disparo2 (Vref2)

0V

5V

5V

4.5V

Figura P6.8.1

Vi

VCC1 R3

R2

R1

V

VCC2

Vo

+

R4

+

Figura P6.8

R

R

Vo

R

R

R

Vi

+ +

Figura P6.3

V4

R4

V3 R3 +

Vo

R6

+ R5

V2

R1

R2

V1

+

+

+ +

Figura P6.4

E2

E1

R2

R2

+

R1

R1

aR

R

R

+

+

+

+

+

Vo

Figura P6.5

+

-

VCE

C2

10uF

15V

C1

1uF

1kHz

Vi

-1/1V

R1 1kΩ

R2

1kΩ

RC 2.2kΩ

RE 8.2kΩ

1kHz

-1/1V

Figura P6.7

vo

1kHz

vi

-1/1V

+

10kΩ

1kΩ

10kΩ

1kΩ

1kHz

-1/1V

+

Figura P6.6

R

104

6.10 Supóngase que en el circuito de la

figura P6.9 se desea monitorear una

batería de 12V. Cuando el voltaje de la

batería cae debajo de 8V, se desea

conectarla a un cargador. Cuando el

voltaje de la batería alcanza 13V, se desea

que se desconecte el cargador. Considere

que el voltaje de alimentación –V se

utiliza para referencia. Además suponga

que ±Vsat =14V.

a.-Encuentre VH y Vctr

b.- La resistencia mR y nR.

6.11 Para el circuito mostrado en la figura

P6.10, determinar Vo. Datos:β=100;

rb=100Ω

mR

n:1

1kHz Vi

-170/170V

12V

R

-15V

15V

+ 12V

+ 1kHz

+ +

nR

R

Figura P6.9

-15V

15V

+

15V

-5V

1kHz Vi

-10m/10mV

Q3

Q2 Q1

120kΩ

120kΩ

100kΩ

100kΩ

2.1kΩ 1kΩ

1kΩ

10kΩ 10kΩ

+

1kHz

Q3

Q2 Q1

Vo

Figura P6.10