Capítulo 2 El microcontrolador y su arquitectura

Transcript of Capítulo 2 El microcontrolador y su arquitectura

ING. MECATRNICA QUINTO SEMESTRE GRUPO A

MICROCONTROLADORES ING. RICARDO GMEZ KU

Captulo 2 El microcontrolador y su arquitectura INTEGRANTES: CHUC CAUICH JOSE GILBERTO CHUC CAUICH JULIO CESAR CONRTRERAS CONTRERAS EDWARD CUTZ VELAZQUEZ NIDIA GABRIELA PECH UUH GABRIELA SALDIVAR CABRERA DAVID FERNANDO

RESUMEN Un microcontrolador (abreviado C, UC o MCU) es un circuito integrado programable, capaz de ejecutar las rdenes grabadas en su memoria. Est compuesto de varios bloques funcionales, los cuales cumplen una tarea especfica. Un microcontrolador incluye en su interior las tres unidades funcionales principales de una computadora: unidad central de procesamiento, memoria y perifricos de entrada/salida. El modelo de programacin de los microprocesadores del 8086 al 80286 contiene registros de 8 y de 16 bits. El modelo de programacin de los microprocesadores 80386 y superiores contiene registros extendidos de 8, 16 y 32 bits, as como dos registros de segmento de 16 bits adicionales FS y GS. Todas las direcciones de memoria en modo real son una combinacin de una direccin de segmento ms de una direccin de desplazamiento. La posicin inicial de un segmento se define mediante el nmero de 16 bits en el registro de segmento al que se adjunta un cero hexadecimal en el extremo derecho. La direccin de desplazamiento es un nmero de 16 bits que se suma a la direccin de segmento de 20 bits para formar la direccin de memoria en modo real. Todas las instrucciones (cdigo) se acceden mediante la combinacin de CS (direccin de segmento) ms IP o EIP (direccin de desplazamiento). Por lo general se hace referencia a los datos a travs de una combinacin del DS (segmento de datos) y una direccin de desplazamiento o el contenido de un registro que contenga la direccin de desplazamiento. Los microprocesadores del 8086 al Pentium 4 utilizan BX, DI y SI como registro de desplazamiento predeterminados para los datos si se seleccionan registros de 16 bits. El 80386 y superiores pueden usar los registros de 32 bits EAX, EBX, ECX, EDX, EDI y ESI como registros de desplazamiento predeterminado para los datos. La operacin en modo protegido permite acceder a la memoria que est por encima del primer 1 Mbyte en los microprocesadores del 80286 al Pentium 4. Este sistema de memoria extendida (XMS) se accede a travs de una direccin de segmento ms una direccin de desplazamiento, justo igual que en el modo real. La diferencia es que la direccin de segmento se almacena en un descriptor que se selecciona mediante el registro de segmento.

2

ABSTRACT A microcontroller (abbreviated microcontrollers, UC or MCU) is a programmable integrated circuit capable of executing the orders recorded in his memory. It consists of several functional blocks, which perform a specific task. A microcontroller includes within it the three main functional units of a computer: central processing unit, memory and peripheral input / output. The programming model of the 8086 to 80286 microprocessor contains records of 8 and 16 bits. The programming model 80386 microprocessor and containing higher extended registers 8, 16 and 32 bits, and two registers additional 16-bit segment FS, and GS. All memory addresses in real mode are a combination of a segment address more than one direction of travel. The initial position of a segment is defined by the number of 16 bits in the segment to which you attach a hexadecimal zero in the far right. The direction of motion is a 16 bit number that is added to the segment address of 20 bits to form the memory address in real mode. All instructions (code) are accessed through a combination of CS (segment address) over IP or EIP (direction of travel). Usually referred to data through a combination of DS (data segment) and a traveling direction or the contents of a register containing the direction of travel. The microprocessors of the Pentium 4 use 8086 BX, DI and SI as a shift register for data default if you select 16-bit registers. The 80386 and above can use 32-bit registers EAX, EBX, ECX, EDX, EDI and ESI as default shift registers for data. The protected mode operation allows access to memory that is above the first 1 Mbyte on the 80286 microprocessor the Pentium 4. This system of extended memory (XMS) is accessed through a segment address plus an offset direction, just as in real mode. The difference is that the segment address is stored in a descriptor which is selected by the segment register.

3

NDICE

RESUMEN ......................................................................................................................................... 1 ABSTRACT ....................................................................................................................................... 3 NDICE .............................................................................................................................................. 4 INTRODUCCIN............................................................................................................................. 5 OBJETIVOS Y/O COMPETENCIAS DE LA UNIDAD .............................................................. 8 CAPTULO 2 El microprocesador y su arquitectura ...................................................................... 9 2-1 ARQUITECTURA INTERNA DEL MICROPROCESADOR .............................................. 10 2-2 REGISTROS DE SEGMENTO Y DE DESPLAZAMIENTO PREDETERMINADOS ....... 16 2-3 INTRODUCCIN AL DIRECCIONAMIENTO DE MEMORIA EN MODO PROTEGIDO ....................................................................................................................................................... 19 2-4 PAGINACIN DE MEMORIA ............................................................................................. 27 2-5 RESUMEN ............................................................................................................................. 32 CONCLUSIONES ........................................................................................................................ 34 BIBLIOGRAFA........................................................................................................................... 37

4

INTRODUCCIN

Chuc Cauich Jos Gilberto 2566 El objetivo de este captulo es la conocer y aprender sobre los sistemas digitales basados en microprocesadores, cubrindose los aspectos bsicos de hardware, software involucrados en el diseo de sistemas con microprocesador enfocados a instrumentacin y control de procesos, se dedica una seccin especial al uso de la computadora personal en algunas aplicaciones como un sistema ms accesible y fcil de programar. Un microprocesador es un controlador complejo sncrono y programable en un solo Circuito integrado. Chuc Cauich Julio Csar 2565 El objetivo de este tema es la de presentar un curso introductorio a los sistemas digitales basados en microprocesador, cubrindose los aspectos bsicos de hardware, software involucrados en el diseo de sistemas con microprocesador enfocados a instrumentacin y control de procesos, se dedica una seccin especial al uso de la computadora personal en algunas aplicaciones como un sistema ms accesible y fcil de programar. Microprocesador: Es un controlador complejo sncrono y programable en un solo circuito integrado. Registro Acumulador (A). La CPU debe poseer por lo menos un acumulador. El acumulador se encarga de guardar datos provisionalmente trados de memoria, adems guarda el resultado de las operaciones realizadas. Edward Contreras Contreras 2575 Lo interesante de esta investigacin es que analizaremos al microprocesador como un dispositivo programable. Se presentara la arquitectura de la familia completa de microprocesadores Intel. Hablaremos sobre arquitectura interna del microprocesador, el modelo de programacin , registros multipropsito , registros de propsito especial, direccionamiento de memoria en modo real, segmentacin y desplazamientos, registros de segmentacin y de desplazamiento predeterminados, esquema de direccionamiento y desplazamiento permite la reubicacin, introduccin al direccionamiento de memoria en modo protegido, selectores y descriptores, registros invisibles para los programas, paginacin de memoria, registros de paginacin, directorio de pginas y la tabla de pginas. Cutz Velazquez Nidia Gabriela 2576

5

En el siguiente trabajo documental se aborda el tema correspondiente al captulo 2 denominado el microcontrolador y su arquitectura, es importante conocer el funcionamiento y las aplicaciones de este tipo de dispositivos ya que forman parte esencial en la programacin, es decir, el manejo de autmatas programables, en el desarrollo del trabajo se abordarn diversos temas relacionados con los microcontroladores, en si nos enfocaremos ms a lo que ha sido el desarrollo de los diferentes tipos de microcontroladores, sus caractersticas y la evolucin que han tenido con el paso del tiempo. Empezaremos con la arquitectura interna del microprocesador, en ella se explican cada uno de los registros y sus caractersticas, as como la manera en que operan. Tambin se hablarn de los modos de direccionamiento de memoria, tanto real como protegido, iniciando estos subtemas se mencionan el modo de operacin de cada uno de ellos, sus diferentes caractersticas y la relacin que existen entre cada uno de ellos. Para finalizar se aborda el tema paginacin de memoria y sus registros, su funcionamiento y diversas caractersticas. Pech Uuh Gabriela 2587 En este captulo es fundamental tener conocimiento de lo que es un microprocesador, al igual conocer de manera detallada su configuracin interna y externa, sus caractersticas y comportamiento de los mismos, ya que en la actualidad con los avances y los diversos estudios que se han hecho, se han logrado mejoras en cada tipo de microprocesador existente, lo cual depende del propsito a realizar y del modo de operacin de cada microprocesador. Debido a su clasificacin, los microprocesadores pueden operar en modo real y en modo protegido (Windows), de igual manera dependen del nmero de bits que se manejan en cada modelo, ya que pueden ser de 16, de 32 y 64 bits. Cabe hacer mencin de que los microprocesadores contienen modelos de programacin, que se utilizan de manera directa e indirecta durante la programacin, todo esto se logra mediante los registros de multipropsito, registros de propsito especial, registros de segmentos, estos registros mencionados anteriormente son los que se manejan en el modo real y en el modo protegido de manera similar, sin embargo con la nica diferencia de que en el modo protegido, en vez de los registros de segmentos (modo real ), se utiliza el selector (modo protegido), al igual otra diferencias entre estas formas de operacin, es la manera en que se interpretan los registros en los microprocesadores. Otro tema que se desarrolla en este captulo, es la paginacin de memoria, que se encuentran en los diferentes tipos de microprocesadores como los son desde el 80386 y superiores, estos contienen una direccin lineal y fsica, la primera es la direccin generada por un programa, la segunda es la posicin actual de la memoria pero cuando ya ha sido utilizada, para que se lleve a cabo la paginacin, se requieren los registros de los mismos, para su posterior almacenamiento en la unidad de paginacin los cuales son CR0 y CR3,

6

cada uno, con una tarea especfica dependiendo del valor que se tenga en la paginacin (CR0 y CR3), los cuales funcionan en los microprocesadores ya sean en el modo real y en el modo protegido.

Saldivar Cabrera David Fernando 2569 En este captulo hablaremos acerca del microprocesador es un circuito integrado, programable que realiza una serie de instruccin en forma de secuencia, est constituido por millones de componentes elctricos, es bastante complicado y realiza procesamiento de datos, las operaciones que se llevan a cabo durante el procesamiento son controladas por medio de programas. Las arquitecturas tradicionales de los microprocesadores tienen atributos fundamentales que limitan su desempeo. Para lograr un alto rendimiento, los procesadores no solo deben ejecutar las instrucciones de una manera ms rpida, sino, que tambin deben ejecutar mas instrucciones por ciclo de reloj, a esto nos referimos como una mayor "ejecucin en paralelo". Mayor ejecucin en paralelo permite que ms informacin sea procesada al mismo tiempo, por consiguiente esto mejora el rendimiento global del procesador

7

OBJETIVOS Y/O COMPETENCIAS DE LA UNIDAD

El presente trabajo documental se encuentra basado en la unidad 2 enfocada a los microprocesadores y la manera en que operan, ste tiene el objetivo principal de hacer que los estudiantes conozcan, comprendan y apliquen un sistema mnimo basado en un microprocesador de por lo menos 16 bits internos, todo esto mediante la comprensin de la parte terica es decir los conceptos que engloban principalmente la arquitectura interna del microprocesador tomando en cuenta cada uno de sus subtemas que ayudan al mejor aprendizaje, entre los que se encuentran los registros multipropsito, los modos de operacin del direccionamiento de la memoria, la paginacin de memoria y sus registros

8

Capitulo 2El microprocesador y su arquitecturaINTRODUCCIN Este captulo se presenta al microprocesador como un dispositivo programable. Primero se analiza el modelo de programacin interno y luego la manera en que se direcciona su espacio de memoria. Se hace una presentacin en forma simultnea de la arquitectura de la familia completa de microprocesadores Intel, as como la manera en que los miembros de la familia direccionan el sistema de memoria. Se describen los modos de direccionamiento de esta poderosa familia de microprocesadores para los modos real y protegido. La memoria de modo real (memoria de DOS) existe en las posiciones 00000H-FFFFFH (el primer 1 Mbyte del sistema de memoria) y est presente en todas las versiones del microprocesador. La memoria de modo protegido (memoria de Windows) existe en cualquier posicin de todo el sistema de memoria, pero est disponible slo para los procesadores del 80286 contiene 16 Mbytes; para los microprocesadores del 80386 al Pentium contiene 4 Gbytes; y para los microprocesadores Del Pentium Pro al Pentium 4 contiene 4 G o 64 Gbytes. OBJETIVOS DEL CAPITULO Al termina este captulo podr: 1. Describir la funcin y el propsito de cada registro visible para un programa en los microprocesadores del 80386 al Pentium 4. 2. Detallar el registro de banderas y el propsito de cada bit de bandera. 3. Describir como se accede a la memoria mediante las tcnicas de direccionamiento de memoria en modo real. 4. Describir como se accede a la memoria mediante las tcnicas de direccionamiento de memoria en modo protegido. 5. Describir los registros invisibles para un programa que existen en los microprocesadores del 80286 al Pentium 4. 6. Detallar la operacin del mecanismo de paginacin de memoria.

9

CAPTULO 2 El microprocesador y su arquitectura

2-1 ARQUITECTURA INTERNA DEL MICROPROCESADOR

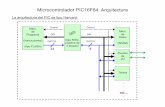

Antes de escribir un programa o de investigar una instruccin, hay que conocer la configuracin interna del microprocesador. En esta seccin veremos detalladamente la arquitectura interna de los microprocesadores del 8086 al Pentium 4, la cual est visible para los programas. Tambin detallaremos la funcin y el propsito de cada uno de estos registros internos. El modelo de programacin El modelo de programacin del 8086 al Pentium 4 se considera como visible para los programas, ya que sus registros se utilizan durante la programacin de aplicaciones y se especifican mediante las instrucciones. Otros registros, que veremos con detalle ms adelante en este captulo, se consideran como invisibles para los programas y que no pueden utilizarse en forma directa durante la programacin de aplicaciones, pero s pueden usarse en forma indirecta. Slo los microprocesadores 80286 y superiores contienen los registros invisibles para los programas que se utilizan para controlar y operar el sistema de memoria protegida y otras caractersticas. La figura 2-1 ilustra el modelo de programacin de los microprocesadores del 8086 al Pentium 4. Los primeros microprocesadores 8086, 8088, y 80286 contienen arquitecturas internas de 16 bits, un subconjunto de los registros mostrados en la figura 2-1. Los microprocesadores del 8086 al 80286 son completamente compatibles con los microprocesadores del 80386 hasta el Pentium 4. Las reas sombreadas de la figura 2-1 representan registros que no se encuentran en los microprocesadores 8086, 8088 u 80286, ya que son mejoras que se proporcionan en los microprocesadores del 80386 al Pentium 4. En el captulo 19 podr consultar la arquitectura de 64 bits de los algunos microprocesadores Pentium 4. FIGURA 2-1 El modelo de programacin de los microprocesadores Intel, del 8086 hasta el Pentium 4. Observaciones: 1. Los registros sombreados slo existen en los microprocesadores del 80386 hasta Pentium 4. 2. Los registros FS y GS no tienen nombres especiales.

10

CAPTULO 2 El microprocesador y su arquitectura

El modelo de programacin contiene registro de 8, 16 y 32 bits. Los registros de 8 bits son AH, AL, BH, BL, CH, CL, DH y DL, y se hace referencia a ellos cuando se forma una instruccin en la que se utilizan estas designaciones de dos letras. Por ejemplo, una instruccin ADD AL, AH suma el contenido de 8 bits de AH con el de AL. (Slo DX cambia debido a esta instruccin.) Los registros extendidos de 32 bits, junto con los registros de 16 bits FS y GS, estn disponibles slo en el microprocesadores 80386 y superiores. Se hace referencia a estos registros mediante las designaciones FS y GS para los dos nuevos registros de 16 bits, y mediante una designacin de tres letras para los registros de 32 bits. Por ejemplo, una instruccin ADD ECX, EBX suma el contenido de 32 bits de EBX con el de ECX. (Slo ECX cambia debido a esta instruccin.) Algunos registros de propsito general (o registros multipropsito), mientras que otros tienen propsitos especiales. Los registros multipropsito son EAX, EBX, ECX, EDX, EBP, EDI y ESI. Estos registros guardan varios tamaos de datos (bytes, palabras o dobles palabras) y se utilizan para casi cualquier propsito, segn lo dicte un programa. Registros multipropsito Se puede hacer referencia a EAX como un registro de 32 bits (EAX), como un registro de 16 bits (AX) o como uno de dos registros de 8 bits (AH y AL). Si se direcciona un registro de 8 o de 16 bits, solo cambia esa porcin de registro de 32 bits sin afectar a los bits restantes. El acumulador se utiliza para instrucciones tales como multiplicacin, divisin y algunas de las instrucciones de ajuste. Para estas instrucciones el acumulador tiene un propsito especial, pero por lo general se considera como un registro multipropsito. En los microprocesadores 80386 y superiores, el registro EAX puede guardar tambin la direccin de desplazamiento de una posicin en el sistema de memoria. Este ndice base puede direccionarse como EBX, BX, BH o BL. Algunas EBX veces el registro BX guarda la direccin de desplazamiento de una posicin (ndice base) en el sistema de memoria, en todas las versiones de microprocesador. En el 80386 y superiores, EBX tambin puede direccionar datos de la memoria. ECX es un registro de propsito general que tambin guarda la cuenta de ECX varias instrucciones. En el 80386 y superiores, el registro ECX tambin (Conteo) puede guardar la direccin de desplazamiento de datos de la memoria. Las instrucciones que utilizan un conteo son las instrucciones de cadena repetida (REP/REPE/REPNE); y las instrucciones desplazamiento (shift), rotacin utilizan CL como el conteo, las instrucciones de cadena repetida usan CX y las instrucciones LOOP/LOOPD utilizan CX o ECX. EDX es un registro de propsito general que guarda una parte del resultado EDX de una multiplicacin, o parte del dividendo antes de una divisin. En el (Datos) 80386 y superiores, este registro tambin puede direccionar datos de la memoria. EBP apunta a una posicin de memoria en todas las versiones del EBP (apuntador de microprocesador para las transferencias de datos de memoria. Este registro EAX (acumulador)

11

CAPTULO 2 El microprocesador y su arquitectura

la base) EDI (ndice destino) ESI (ndice origen)

se direcciona como BP o EBP. Frecuentemente, EDI direcciona datos de destino de cadena para las de instrucciones de cadenas. Tambin funciona como un registro de propsito general de 32 bits (EDI) o de 16 bits (DI) El ndice de origen se utiliza como ESI o SI. A menudo el registro de ndice de de origen direcciona datos de cadena de origen para las instrucciones de cadenas. Al igual que EDI, ESI tambin funciona como registro de propsito general. Se direcciona como la SI al utilizarlo como registro de 16 bits; se direcciona como ESI al utilizarlo como registro de 32 bits.

Registro de propsito especial. Estos registros son EIP, ESP y EFLAGS; y los registros de segmento CS, DS, ES, SS, FS y GS. EIP direcciona la siguiente instruccin en una seccin de memoria EIP (Apuntador de definida como segmento de cdigo. Este registro es IP (16 bits) cuando el microprocesador opera en modo real y EIP (32 bits) cuando el 80386 instrucciones) y superiores operan en modo protegido. Los microprocesadores 8086, 8088 y 80286 no contienen un registro EIP, por lo que slo el 80286 y superiores operan en modo protegido. El apuntador de instrucciones, que apunta a la siguiente instruccin en un programa, se utiliza por el microprocesador para encontrar la siguiente instruccin secuencial en un programa ubicado dentro del segmento de cdigo. El apuntador de instrucciones puede modificarse mediante un salto (jump) o una instruccin de llamada (call) ESP direcciona un rea de la memoria llamada pila. La memoria de la ESP (apuntador de pila almacena datos a travs de este apuntador, explicaremos su funcionamiento ms adelante en el texto, con las instrucciones que la pila) direccionan los datos de la pila. Se hace referencia a este registro como SP si se utiliza como un registro de 16 bits, y como ESP si se utiliza como registro de 32 bits. Este registro indica la condicin del microprocesador y controla su EFLAGS operacin. La figura 2-2 muestra los registros de bandera de todas las (banderas) versiones del microprocesador. Las banderas son compatibles hacia arriba desde los microprocesadores 8086/8088 hasta la Pentium 4. Los microprocesadores del 8086-80286 contienen un registro FLAG (16 bits) y los microprocesadores 80386 y superiores contienen un registro EFLAG (registro extendido de banderas de 32 bits). Los cinco bits de bandera de la extrema derecha y la bandera de desbordamiento cambian despus de la ejecucin de muchas instrucciones aritmticas y lgicas. Las banderas nunca cambian cuando hay transferencia de datos o cuando se realiza una operacin de control del programa. Algunas de las banderas se utilizan tambin para controlar caractersticas incluidas en el microprocesador. A continuacin se muestra una lista de cada bit de bandera, con una breve descripcin de su funcin. A medida que vayamos presentando

12

CAPTULO 2 El microprocesador y su arquitectura

instrucciones en los siguientes captulos, proporcionaremos detalles adicionales sobre los bits de bandera. Las cinco banderas de ms a la derecha y la bandera de desbordamiento cambian en base a la mayora de las operaciones aritmticas y lgicas, aunque las transferencias de datos no les afectan. C (acarreo) ste guarda el valor del acarreo despus de la suma, o la sustraccin despus de la resta. La bandera de acarreo tambin indica condiciones de error, segn lo indiquen algunos programas y procedimientos. Esto es definitivamente cierto en las llamadas a las funciones del DOS.

FIGURA 2-2 El conteo de los registros EFLAGS y FLAG para la familia completa de microprocesadores 80X86 y Pentium.

P (paridad)

A (acarreo auxiliar)

Z (cero)

S (signo)

La paridad es un 0 lgico para paridad impar y un 1 lgico para paridad par. La paridad es el conteo de los unos en un nmero expresado como par o impar. Por ejemplo, si un nmero contiene tres bits uno binario, tiene una paridad impar. Si un nmero no contiene bits uno, tiene una paridad par. La bandera de paridad tiene poca aplicacin en la programacin moderna; se implemento en los primero microprocesadores Intel para comprobar los datos en los entornos de comunicaciones. En la actualidad la comprobacin de paridad a menudo la realiza el equipo de comunicaciones de datos, en vez del microprocesador. El acarreo auxiliar guarda el acarreo (medio acarreo) despus de la suma o la sustraccin despus de la resta entre las posiciones de bit 3 y 4 del resultado. Este bit de bandera altamente especializado lo comprueban las instrucciones DAA y DAS para ajustar el valor de AL despus de una suma o resta BCD. En cualquier otro caso, ni el microprocesador ni otras instrucciones utilizan este bit de bandera. La bandera cero indica que el resultado de una operacin aritmtica o lgica es cero. Si Z=1, el resultado es cero; si Z=0, el resultado no es cero. Esto puede ser confuso, pero es la manera en que Intel decidi nombrar esta bandera La bandera de signo guarda el signo aritmtico del resultado despus de la ejecucin de una instruccin aritmtica o lgica. Si S=1, el bit de

13

CAPTULO 2 El microprocesador y su arquitectura

signo (el bit est ms a la izquierda de un nmero) est activado o es negativo; si S=0, el bit de signo esta desactivado o es positivo. La bandera de trampa habilita el atrapamiento a travs de una T (trampa) caracterstica de depuracin integrada en el chip. (Un programa se depura para encontrar un error o bug) Si la bandera T est habilitada (1), el microprocesador interrumpe el flujo del programa basndose en las condiciones indicadas por los registros de depuracin y los registros de control. Si la bandera T es un lgico, se deshabilita la caracterstica de atrapamiento (depuracin). La herramienta de depuracin de Visual C++ utiliza la caracterstica de trampa y los registros de depuracin para depurar el software con fallas. La bandera de interrupcin controla la operacin de la terminal de I (interrupcin) entrada INTR (peticin de interrupcin). Si I=1, se habilita la terminal INTR; si I=0, se deshabilita la terminal INTR. El estado del bit de bandera I se controla mediante las instrucciones STI (establecer bandera I) y CLI (borrar bandera I). La bandera de direccin selecciona el modo de incremento o de D (direccin) decremento para los registros DI y/o Si durante las instrucciones de cadena. Si D=1; Si D=0 entonces incrementa automticamente. Los registros se decrementan automticamente. La bandera D se establece con la instruccin STD (establecer direccin) y se borra con la instruccin CLD (borrar direccin). Un desbordamiento ocurre cuando se suman o restan nmeros con O (desbordamiento) signo. Un desbordamiento indica que el resultado ha excedido la capacidad de la mquina. Por ejemplo, si se suma 7FH (+128) (usando una suma de 8 bits) con 01H (+1), el resultado es 80H (-128). Este resultado representa una condicin de desbordamiento indicada por la bandera de desbordamiento para la suma con signo. En las operaciones sin signo se ignora esta bandera. Esta bandera se utiliza en operacin de modo protegido para IOPL (nivel de privilegio de E/S) seleccionar el nivel de privilegio para los dispositivos de E/S. Si el nivel de privilegio actual es mayor o de ms confianza que el IOPL, la operacin de E/S se ejecuta sin impedimento. Si el IOPL es menor que el nivel de privilegio actual se produce una interrupcin, haciendo que se suspenda la ejecucin. Hay que tener en cuenta que un IOPL de 11 es el ms bajo o de menor confianza. La bandera de tarea anidada indica que la tarea actual est anidada NT (tarea dentro de otra tarea en operacin de modo protegido. Esta bandera se anidada) establece cuando la tarea se anida mediante software. La bandera de continuacin se utiliza con la depuracin para controlar RF la continuacin de la ejecucin despus de la siguiente instruccin. (continuacin) El bit de bandera VM selecciona la operacin en modo virtual en un VM (modo sistema de modo protegido. Un sistema de modo virtual permite que virtual) coexistan barias participaciones de memoria de DOS de 1 Mbyte de longitud en el sistema de memoria. En esencia, esto permite al programa del sistema ejecutar varios programas de DOS. VM utiliza para simular el DOS en el entorno moderno Windows.

14

CAPTULO 2 El microprocesador y su arquitectura

AC (comprobacin de alineacin)

VIF (interrupcin virtual) VIP (interrupcin virtual pendiente) ID (identificacin)

El bit de comprobacin de alineacin se activa si se direcciona una palabra o doble palabra en un lmite que no sea de palabra o de doble palabra. Slo el microprocesador 80487SX contiene el bit de comprobacin de alineacin que es utilizado para sincronizacin principalmente por el coprocesador numrico 80487SX que lo acompaa. El VIF es una copia del bit de bandera de interrupcin disponible para los microprocesadores del Pentium al Pentium 4. VIP proporciona informacin sobre una interrupcin en modo virtual para los microprocesadores del Pentium 4. Se utiliza en entornos multitarea para proporcionar banderas de interrupcin virtual al sistema operativo, adems de informacin de interrupciones pendientes. La bandera ID indica que los microprocesadores del Pentium al Pentium 4 soportan la instruccin CPUID. Esta instruccin proporciona informacin al sistema sobre el microprocesador Pentium, como su nmero de versin y el fabricante.

Registro de segmento. Los registros adicionales, llamados registros de segmento, generan direcciones de memoria cuando se combinan con otros registros en el microprocesador. Hay de cuatro a seis registros de segmento en diversas versiones del microprocesador. Un registro de segmento funciona en forma distinta en el modo real, cuando se compara con la operacin del microprocesador en modo protegido. Ms adelante en este captulo proporcionaremos los detalles sobre su funcin en modo real y en modo protegido. A continuacin se muestra una lista de cada uno de los registros de segmento, junto con su funcin en el sistema: CS (cdigo) El segmento de cdigo es una seccin de la memoria que guarda el cdigo (programas y procedimientos) utilizado por el microprocesador. El registro del segmento de cdigo define la direccin inicial de la seccin de memoria que guarda el cdigo. En la operacin en modo real, define el inicio de una seccin de 64 Kbytes de memoria; en modo protegido selecciona un descriptor que describe la direccin inicial y la longitud de una seccin de memoria que guarda el cdigo. El segmento de cdigo est limitado a 64 Kbytes en los microprocesadores del 8088 al 80286, y a 4 Gbytes en los microprocesadores 80386 y superiores cuando stos operan en modo protegido. El segmento de datos es una seccin de memoria que contiene la mayor parte de los datos utilizados por un programa. Se accede a los datos en el segmento de datos mediante una direccin de desplazamiento o el contenido de otro registro que guardan la direccin de desplazamiento. Al igual que con el segmento de cdigo y otros segmentos, la longitud est limitada a 64 Kbytes en los microprocesadores del 8086 al 80286, y a 4 Gbytes en los microprocesadores 80386 y superiores.

DS (datos)

15

CAPTULO 2 El microprocesador y su arquitectura

ES (extra) SS (pila)

FS y GS

El segmento extra es un segmento de datos adicionales utilizado por algunas de las instrucciones de cadena para guardar datos de destino El segmento de pula define el rea de memoria utilizada para la pila. El punto de entrada de la pila se determina mediante los registros segmento de pila y apuntador de pila. El registro BP tambin direcciona datos dentro del segmento de pila. Los segmentos FS y GS son registros de segmento suplementario, disponibles en los microprocesadores del 80386 al Pentium 4 para que los programas puedan acceder a dos segmentos de memoria adicionales. Windows utiliza estos segmentos para operaciones internas, pero no hay disponible una definicin de su uso. SEGMENTO Y DE DESPLAZAMIENTO

2-2 REGISTROS DE PREDETERMINADOS

El microprocesador tiene un conjunto de reglas que se aplican a los segmentos, siempre que se direcciona la memoria. Estas reglas, que se aplican en modo real y en modo protegido, definen la combinacin del registro de segmento y del registro del desplazamiento. Por ejemplo, el registro de segmento de cdigo siempre se utiliza con el apuntador de instrucciones para direccional la siguiente instruccin en un programa. Esta combinacin es CS: IP o CS: EIP, dependiendo del modo de operacin del microprocesador. El registro de segmento de cdigo define el inicio del segmento de cdigo y el apuntador de instrucciones localiza la siguiente instruccin dentro del segmento de cdigo. Esta combinacin (CS: IP o CS: EIP) localiza la siguiente instruccin que va a ejecutar el microprocesador. Por ejemplo, si CS= 1400H e IP/EIP= 1200H, el microprocesador obtiene su siguiente instruccin de la posicin de memoria 14000H + 1200H, o 15200H. Otra de las combinaciones predeterminadas es la pila. Se hace referencia a los datos de la pila a travs del segmento pila en la posicin de memoria direccionada por el apuntador de la pila (SP/ESP) o por el apuntador (BP/EBP). Se hace referencia a estas combinaciones como SS: SP (SS: ESP) o SS: BP (SS: EBP). Por ejemplo, si SS= 2000H y BP= 3000H, el microprocesador direcciona la posicin de memoria 23000H para la posicin de memoria del segmento de la pila. En modo real solo los 16 bits mas a la derecha de la direccin del registro extendido direccional una posicin dentro del segmento de memoria. En los microprocesadores del 80386 al Pentium 4 nunca se debe colocar un nmero mayor de FFFFH en un registro de desplazamiento si el microprocesador se opera en modo real. Esto hace que el sistema se detenga y que indique un error de direccionamiento. En la tabla 2-2 se muestran otras combinaciones predeterminadas para direccional memoria mediante un microprocesador Intel con registros de 16 bits. La tabla 2-3 muestra las combinaciones predeterminadas que se asumen en los microprocesadores 80386 y superiores, los cuales utilizan registros de 32 bits. Estos microprocesadores tienen una

16

CAPTULO 2 El microprocesador y su arquitectura

mayor seleccin de combinaciones de direccin de segmento/desplazamiento que los microprocesadores del 8086 al 80286.

TABLA 2-3 Combinaciones predeterminadas de segmento y desplazamiento de 32 bits

Segmento CS SS DS ES FS GS

Desplazamiento Propsito especial EIP Direccin de la instruccin ESP o EBP Direccin de la pila EAX, EBX, ECX, ESI, EDI, un Direccin de los datos nmero de 8 o de 32 bits EDI para las instrucciones de Direccin de la destino de cadena cadena No hay predeterminado Direccin general No hay predeterminado Direccin general

FIGURA 2-4 Un sistema de memoria que muestra la colocacin de cuatro segmentos de memoria

O incluso traslaparse con otro, si no se requieren 64 Kbytes de memoria para un segmento. Piense en los segmentos como si fueran ventanas que pueden desplazarse sobre cualquier

17

CAPTULO 2 El microprocesador y su arquitectura

rea de memoria para acceder a los datos o al cdigo. Adems, un programa puede tener ms de cuatro o de seis segmentos, pero solo puede acceder a cuatro o seis segmentos a la vez. Suponga que un programa de aplicacin requiere 1000H bytes de memoria para su cdigo, 190H bytes de memoria para sus datos y 200H bytes de memoria para su pila. Esta aplicacin no requiere un segmento extra. Cuando el DOS coloca este programa en el sistema de memoria, se carga en la TPA en la primera rea disponible de memoria por encima de los controladores y otros programas de la TPA. Esta rea se indica mediante un apuntador libre que es mantenido por el DOS. La carga del programa se maneja automticamente mediante el cargador de programas que se encuentra dentro del DOS. La figura 2-5 muestra como se almacena una aplicacin en el sistema de memoria. Los segmentos muestran un traslapamiento ya que no se requieren 64 Kbytes de memoria para la cantidad de datos en ellos. La vista lateral de los segmentos muestra claramente el traslapamiento. Tambin muestra cmo pueden desplazarse los segmentos sobre cualquier rea de la memoria, si se cambia la direccin inicial del segmento. Afortunadamente, el cargador de programas del DOS calcula y asigna las direcciones inciales de los segmentos. El esquema de direccionamiento mediante segmento y desplazamiento permite la reubicacin. El esquema de direccionamiento mediante segmento y desplazamiento parece exclusivamente complicado. En realidad es complicado, pero tambin ofrece una ventaja para el sistema. Este complicado esquema de direccionamiento de segmento ms desplazamiento permite reasignar los programas DOS en FIGURA 2-5 Un programa de aplicacin que contiene un segmento de cdigo, uno de datos y uno de pila, cargado en la memoria de un sistema DOS

18

CAPTULO 2 El microprocesador y su arquitectura

el sistema de memoria. Tambin permite que los programas escritos para funcionar en modo real operen en un sistema en modo protegido. Un programa reubicable puede colocar rea de memoria, y puede utilizarse sin necesidad de hacerle cambios. El esquema de direccionamiento mediante segmento y desplazamiento permite la reubicacin de programas y datos sin necesidad de hacer cambios. Esto es ideal para usarse en un sistema computacional de propsito general, en el que no todos los equipos contienen las mismas reas de memoria. La estructura de memoria de la computadora personal es distinta dependiendo del equipo, por lo que se necesita usar datos y software que puedan reubicarse. Como la memoria se direcciona dentro de un segmento mediante una direccin de desplazamiento, el segmento de memoria puede moverse a cualquier lugar del sistema de memoria sin necesidad de cambiar las direcciones de desplazamiento. Esto se logra mediante el desplazamiento del programa completo, como un bloque, hacia una nueva rea y despus se cambia slo el contenido de los registros de segmento. Si una direccin est cuatro bytes por encima del inicio del segmento, su direccin de desplazamiento es de 4. Si todo el programa se desplaza hacia una nueva rea de memoria, esta direccin de desplazamiento de 4 sigue apuntando a cuatro bytes por encima del inicio del segmento. Slo hay que cambiar el contenido del registro de segmento para direccionar el programa en la nueva rea de memoria. Sin esta caracterstica, un programa tendra que reescribirse o alterarse exhaustivamente antes de poder moverlo. Para ello se requerira de tiempo adicional o de muchas versiones del programa para las distintas configuraciones de sistemas computacionales. Este concepto tambin se aplica a los programas escritos para ejecutarse en el modo protegido para Windows. En el entorno de Windows todos los programas se escriben suponiendo que los primeros 2 G de memoria estn disponibles para cdigo y datos. Cuando el programa se carga, se coloca en la memoria actual, que podra estar en cualquier parte, y una porcin podra estar localizada en el disco, en forma de archivo de intercambio. 2-3 INTRODUCCIN AL DIRECCIONAMIENTO DE MEMORIA EN MODO PROTEGIDO Este mtodo de direccionamiento (disponible para el 80826 y superiores) permite el acceso a los datos y programas localizados por encima del primer 1 Mbyte de memoria, as como los que estn dentro del primer 1 Mbyte de memoria. El modo protegido es el que opera Windows. Para direccionar esta seccin extendida del sistema de memoria se requiere un cambio en el esquema de direccionamiento mediante un segmento ms un desplazamiento que se utiliza con el direccionamiento de memoria en modo real. Cuando los datos y los programas se direccionan en memoria extendida, la direccin de desplazamiento se sigue utilizando para acceder a la informacin localizada dentro del segmento de memoria. Una diferencia es que la direccin de segmento, segn lo visto con el direccionamiento de memoria en modo real, ya no est presente en el modo protegido. En lugar de la direccin de segmento, el registro de segmento contiene un selector que

19

CAPTULO 2 El microprocesador y su arquitectura

escoge un descriptor de una tabla de descriptores. El descriptor presenta la posicin, longitud y derechos de acceso del segmento de memoria. Como el registro de segmento y la direccin de desplazamiento siguen accediendo a la memoria, las instrucciones en modo protegido son idnticas a las instrucciones en modo real. De hecho, la mayora de los programas escritos para funcionar en el modo real funcionaran sin cambios en el modo protegido. La diferencia entre los modos es a manera en que el microprocesador interpreta el registro de segmento para acceder al segmento de memoria. Otra diferencia en los microprocesadores 80386 y superiores es que la direccin de desplazamiento puede ser de 32 bits, en vez de 16 bits en modo protegido. Una direccin de desplazamiento de 32 bits permite que el microprocesador acceda a los datos dentro de un segmento que puede tener hasta 4 Gbyte de longitud.

Selectores y descriptores El selector que se encuentra en el registro de segmento, selecciona uno de 8192 descriptores de una o dos tablas de descriptores. El descriptor presenta la posicin, longitud y derechos de acceso del segmento de memoria. El registro de segmento an selecciona un segmento de memoria (aunque de forma indirecta), pero no de forma directa como en el modo real. Por ejemplo en el modo real si CS= 0008H, el segmento de cdigo empieza en la posicin 00080H. En el modo protegido, este nmero de segmento puede direccionar cualquier posicin de memoria en todo el sistema para que el segmento de cdigo, como explicaremos en breve. Hay dos tablas de descriptores que se utilizan con los registros de segmento: una contiene descriptores globales y la otra contiene descriptores locales. Los descriptores globales contienen definiciones de segmentos que se aplican a todo los programas, mientras que los descriptores locales son por lo general nicos para una aplicacin. Al descriptor global lo podemos llamar descriptor de sistema y al descriptor local lo podemos llamar descriptor de aplicacin. Cada tabla contiene 8192 descriptores, por lo que hay un total de 16384 descriptores para una aplicacin en un momento dado. Como el descriptor describe un segmento de memoria, esto permite que se describan hasta 16384 segmentos de memoria para cada aplicacin. Como un segmento de memoria puede tener hasta 4 Gbyte de longitud, esto significa que una aplicacin podra tener acceso a 4 G x 16384 bytes de memoria, o de 64 Tbyte.

20

CAPTULO 2 El microprocesador y su arquitectura

FIGURA 2-6 80386 al Pentium 4

Los formatos de descriptores para los microprocesadores 80286 y

La figura 2-6 muestra el formato de un descriptor para los microprocesadores del 80286 al Pentium 4. Observe que cada descriptor es de ocho bytes de longitud, por lo que las tablas de descriptores globales y de descriptores locales tienen cada una un mximo de 64 Kbytes de longitud. Los descriptores para el microprocesador 80286 y para los microprocesadores del 80386 al Pentium 4 difieren ligeramente, pero el descriptor del 80286 es compatible con los ms recientes. La porcin de direccin base del descriptor indica la posicin inicial del segmento de memoria. Para el microprocesador 80286 la direccin base es de 24 bits, por lo que los segmentos empiezan en cualquier porcin de sus 16 Mbyte de memoria. La limitacin en cuanto al lmite de los prrafos se elimina en estos microprocesadores cuando se operan en modo protegido, por lo que los segmentos pueden comenzar en cualquier direccin. Los microprocesadores 80386 y superiores pueden utilizar una direccin base de 32 bits que permite los segmentos inicien en cualquier posicin dentro de sus 4 Gbyte de memoria. Observe cmo la direccin base del descriptor del 80286 es compatible hacia arriba con el descriptor de los microprocesadores 80386 al Pentium 4, ya que sus 16 bits ms significativos son 0000H. Consulte los captulos 18 y 19 para ver los detalles adicionales sobre el espacio de memoria de 64 G que proporcionan los microprocesadores del Pentium Pro al Pentium 4. El lmite de segmento contiene la ltima direccin de desplazamiento de un segmento. Por ejemplo, si un segmento comienza en la posicin de memoria F00000H y termina en la posicin F000FFH, la direccin base es F00000H y el lmite es FFH. Para el microprocesador 80286, la direccin base es F00000H y el lmite es 00FH. Para los microprocesadores 80386 tiene un lmite de base 00F00000H y el lmite es 000FFH. Observe que el microprocesador 80286 tiene un lmite de 16 bits y los microprocesadores del 80386 al Pentium 4 tienen un lmite de 20 bits. Un 80286 accede a los segmentos de memoria que tienen entre 1 y 64 Kbytes de longitud. El 80386 y superiores acceden a los segmentos de memoria que tienen entre 1 y 1Mbyte, o entre 4 K y 4 Gbyte de longitud. Hay otra caracterstica incluida en el descriptor de los microprocesadores del 80386 al Pentium 4 que no se encuentra en el descriptor del 80286: el bit G, o bit de granularidad. Si G = 0, lmite especifica un lmite de segmento de 00000H a FFFFFH. Si G = 1, el valor del lmite se multiplica por 4 Kbytes (se adjunta a FFFH). El lmite sera entonces de

21

CAPTULO 2 El microprocesador y su arquitectura

00000FFFFH a FFFFFFFFH si G = 1. Esto permite una longitud de segmento de 4 K a 4 Gbyte, en intervalos de 4 bytes. La razn por la que la longitud de segmento es de 64 bytes en el 80286 es que la direccin de desplazamiento siempre es de 16 bits, debido a su arquitectura interna de 16 bits. Los microprocesadores 80386 y superiores utilizan una arquitectura de 32 bits que permite una direccin de desplazamiento (en la operacin en modo protegido) de 32 bits. Esta direccin de desplazamiento de 32 bits permite longitudes de segmento de 4 Gbyte y la direccin de desplazamiento de 16 bits permite longitudes de segmento de 64 Kbytes. Los sistemas operativos funcionan en un entorno de 16 o de 32 bits. Por ejemplo, DOS utiliza un entorno de 16 bits, mientras que la mayora de las aplicaciones Windows utilizan un entorno de 32 bits llamado WIN32. El ejemplo 2-1 muestra cmo empieza y termina el segmento si la direccin base es de 10000000H, el lmite es 001FFH y G = 0. EJEMPLO 2-1 Base = Inicio = 10000000H G=0 Final = Base + Lmite = 10000000H + 001FFH =100001FFH El ejemplo 2-2 utiliza los mismos datos que el ejemplo 2-1, slo que el bit G = 1. Observe que el lmite se adjunta con FFFH para determinar la direccin de segmento final. EJEMPLO 2-2 Base = Inicio = 10000000H G=1 Final = Base + Lmite = 10000000H + 001FFFFFH =101FFFFFH El bit AV en el descriptor de los microprocesadores 80386 y superiores es utilizado por algunos sistemas operativos para indicar que el segmento est disponible (AV = 1) o no est disponible (AV = 0). El bit D indica cmo las instrucciones de los microprocesadores del 80386 al Pentium 4 acceden a los

22

CAPTULO 2 El microprocesador y su arquitectura

FIGURA 2-7 El byte de derechos de acceso para el descriptor de los microprocesadores del 80286 al Pentium 4 datos que los registros y de la memoria en el modo real o protegido. Si D = 0, las instrucciones son de 16 bits, compatibles con los microprocesadores 886-80286. Esto significa que las instrucciones utilizan direcciones de desplazamientos de 16 bits y registros de 16 bits de manera predeterminada. A este modo se le llama por lo general el modo de instrucciones de 16 bits o modo DOS. Si D = 1, las instrucciones son de 32 bits. De manera predeterminada, el modo de instrucciones de 32 bits supone que todas las direcciones de desplazamiento y registros son de 32 bits. El valor predeterminado por el tamao de los registros y la direccin de desplazamiento se redefinen en los modos de instrucciones de 16 bits y de 32 bits. Los sistemas operativos MSDOS y PCDOS requieren que las instrucciones siempre se utilicen en el modo de instrucciones de 16 bits. Windows 3.1 y cualquier aplicacin que haya sido escrita para este sistema tambin requieren que se seleccione el modo de instrucciones de 16 bits. El modo de instrucciones es accesible slo es un sistema de modo protegido como Windows XP. En los captulos 3 y 4 veremos ms detalles sobre estos modos y su aplicacin en el conjunto de instrucciones. El byte de derechos de acceso (vea la figura 2-7) controla el acceso al segmento en modo protegido. Este byte describe la manera en que funciona el segmento en el sistema. El byte de derechos de acceso permite un completo control sobre el segmento. Si el segmento es de datos, se especifica la direccin de crecimiento. Si el segmento crece ms all de su lmite se interrumpe el programa del sistema operativo del microprocesador, indicando una falla de proteccin general. Incluso se puede especificar si se puede escribir en un segmento de datos o si est protegido contra escritura. El segmento de cdigo tambin se controla de una forma similar y puede inhibir la lectura para proteger el software.

23

CAPTULO 2 El microprocesador y su arquitectura

Los descriptores se seleccionan de la tabla mediante el registro de segmento. La figura 2-8 muestra cmo funciona el registro de segmento en el sistema en modo protegido. El registro de segmento contiene un campo selector de 13 bits, un bit selector de tabla y un campo de nivel de privilegio solicitado. El selector de 13 bits selecciona uno de los 8192 descriptores de la tabla. El bit T1 selecciona ya sea la tabla de descriptores globales (T1 = 0) o la tabla de descriptores locales. El Nivel de privilegio solicitado (RPL) solicita el nivel de privilegio de acceso de un segmento de memoria. El nivel de privilegio ms alto es de 00 y el menor es 11. Si el nivel de privilegio solicitado concuerda o tiene mayor prioridad que el nivel de privilegio establecido por el byte de derechos de acceso, se otorga el acceso. Por ejemplo. Si el novel de privilegio solicitado es de 10 y el byte de derechos de acceso establece el nivel de privilegio del segmento en 11, se otorga el acceso ya que 10 es mayor en prioridad que el nivel de

FIGURA 2-8 El contenido de un registro de segmento durante la operacin en modo protegido de los microprocesadores de 80286 al Pentium 4 privilegio 11. Los niveles de privilegio se utilizan en entornos multiusuario. Windows utiliza el nivel de privilegio 00 (anillo 0) para el ncleo (kernel) y los programas controladores, y el nivel 11 (anillo 3) para las aplicaciones. Windows no utiliza los niveles 01 o 10. Si se violan los niveles de privilegio, el sistema por lo general indica una marca de violacin de aplicacin o de nivel de privilegio. La figura 2-9 muestra cmo el registro de segmento, que contiene un selector, escoge un descriptor de la tabla de descriptores globales. La entrada en la tabla de descriptores globales selecciona un segmento en el sistema de memoria. En esta ilustracin DS contiene 0008H, que accede al nmero de descriptor 1 de la tabla de descriptores globales mediante el uso de un nivel de privilegio solicitado de 00. El nmero de descriptor 1 contiene un descriptor que define la direccin base como 00100000H con un lmite de segmento de 000FFH. Esto significa que si una carga un valor de 0008H en DS el microprocesador utilizar para el segmento de datos con esta tabla de descriptores de ejemplo. Al descriptor cero se le nombra descriptor nulo, el cual debe contener slo ceros y no puede utilizarse para acceder a la memoria.

24

CAPTULO 2 El microprocesador y su arquitectura

FIGURA 2-9 Uso del registro DS para seleccionar una descripcin de la tabla de descriptores globales. En este ejemplo, el registro DS accede a las posiciones de memoria 100000H-1000FFG como segmento de datos Registros invisibles para los programas Las tablas de descriptores globales y locales se encuentran en el sistema de memoria. Para poder acceder a estas tablas y especificar su direccin, los microprocesadores del 80286 al Pentium 4 contienen registros invisibles para los programas. Como es software no direcciona directamente estos registros invisibles para los programas, por eso se les da ese nombre (aunque el software del sistema accede a algunos de estos registros). La figura 2-10 ilustra la manera en que aparecen los registros invisibles para los programas en los microprocesadores del 80286 al Pentium 4. Estos registros controlan el microprocesador cuando ste opera en modo protegido. Cada uno de los registros de segmento contiene una porcin invisible para los programas que se utilizan en el modo protegido. La porcin invisible para los programas de estos registros se llama por lo general memoria cach. Ya que la cach es cualquier memoria que almacena informacin. Esta cach no debe confundirse con las cachs de nivel 1 0 de nivel 2 que se encuentran en el microprocesador. La porcin de registro de segmento invisible para los programas se carga con la direccin base, con el lmite y derechos de acceso cada vez que se modifica el nmero del registro del segmento. Cuando se coloca un nuevo nmero de segmento en un registro de segmento, el microprocesador accede a una tabla de descriptores y carga el descriptor en la porcin del registro de segmento invisible para los programas. Se mantiene ah y se utiliza para acceder a segmento de memoria hasta el nmero de segmento se cambie de nuevo. Esto permite al

25

CAPTULO 2 El microprocesador y su arquitectura

microprocesador acceder varias veces a un segmento de memoria sin hacer referencia a la tabla de descriptores (de ah que se utilice el trmino cach). El GDTR (registro de tabla de descriptores globales) y el IDTR (registro de tabla de descriptor de interrupciones) contienen la direccin base de la tabla de descriptores y su lmite. El lmite de cada tabla de descriptores es de 16 bits, ya que la mxima longitud de tabla es de 64 Kbyte. Cuando se desea la operacin en modo protegido, se carga la direccin de la tabla de descriptores globales y su lmite en el GDTR. Antes de usar el modo protegido hay que inicializar la tabla de descriptores de interrupciones y el IDTR. Ms adelante veremos los detalles sobre la operacin en modo protegido. En este punto es imposible ver la programacin y la descripcin adicional de estos registros.

FIGURA 2-10 El registro invisible para los programas dentro de los microprocesadores del 80286 al Pentium 4 La posicin de la tabla de descriptores locales se selecciona de la tabla de descriptores globales. Uno de los descriptores globales se establece de manera que direccione la tabla de descriptores locales. Para acceder a la tabla de descriptores locales, el LDTR (registro de tabla de descriptores locales) se carga con un selector, de igual forma que un registro de segmento se carga la direccin, el lmite y los derechos de acceso de la tabla de descripciones locales en la porcin da la cach de LDTR. El TR (registro de tareas) guarda un selector, el cual accede a un descriptor que define una tarea. sta viene siendo por lo general un procedimiento o un programa de aplicacin. El descriptor para el procedimiento o el programa de aplicacin se almacena en la tabla de descriptores globales, por lo que el acceso puede controlarse a travs de los

26

CAPTULO 2 El microprocesador y su arquitectura

niveles de privilegio. El registro de tareas permite cambiar de contexto o de tarea en aproximadamente 17 s. La conmutacin de tareas permite al microprocesador conmutar entre varias tareas en un tiempo considerablemente corto. El conmutador de tareas permite a los sistemas de multitarea conmutar de una tarea a otra de una forma simple y ordenada. 2-4 PAGINACIN DE MEMORIA

El mecanismo de paginacin de memoria ubicado dentro de los microprocesadores 80386 y superiores permite asignar cualquier posicin de memoria fsica a cualquier direccin lineal. La direccin lineal se define como la direccin generada por un programa. La direccin fsica es la posicin actual de memoria utilizada por un programa. Con la unidad de paginacin de memoria, la direccin lineal se traduce de forma invisible a cualquier direccin fsica, lo cual permite que una aplicacin escrita para funcionar en una direccin especfica pueda reubicarse mediante el mecanismo de paginacin. Tambin permite colocar la memoria en reas en las que no existe. Un ejemplo son los bloques de memoria superior que proporciona EMM386.EXE en un sistema DOS. El programa EMM386.EXE reasigna la memoria extendida, en bloques de 4 K, a la memoria del sistema que est entre el BIOS del video y los ROMS del BIOS del sistema para los bloques de memoria superior. Sin el mecanismo de paginacin es imposible utilizar esta rea de la memoria. En Windows cada aplicacin tiene permitido un espacio de direcciones lineales de 2 G en las posiciones 00000000-H7FFFFFFFH, an y cuando no pueda haber suficiente memoria o memoria disponible en estas direcciones. Cualquier aplicacin Windows puede ejecutarse mediante la paginacin en la unidad de disco duro y la paginacin en la memoria a travs de la unidad de paginacin de memoria. Registros de paginacin La unidad de paginacin se controla basndose en el contenido de los registros de control del microprocesador. En la figura 2-11 podr ver el contenido de los registros de control CRO al CR4. Tenga en cuenta que estos registros estn disponibles en los microprocesadores del80386 al Pentium. Comenzando con el Pentium hay un registro de control adicional CR4, que controla las extensiones a la arquitectura bsica proporcionada en el Pentium o en los microprocesadores ms recientes. Una de estas caractersticas es una pgina de 4 Mbytes que se habilita al establecer la posicin del bit 4 del CR4. En los captulos 18 y 19 podr consultar ms detalles sobre el sistema de paginacin de memorias de 4 Mbytes. Los registros que son importantes para la unidad de paginacin son CR0 y CR3. La posicin del bit ms a la izquierda (PG) de CR0 selecciona la paginacin cuando se coloca

27

CAPTULO 2 El microprocesador y su arquitectura

a un nivel lgico de 1. Si el bit PG est inactivo (0), la direccin lineal que genera el programa se convierte en la direccin fsica que se utilice para acceder a la memoria. Si el bit PG est activo (1), la direccin lineal se convierte en una direccin fsica a travs de mecanismo de paginacin. Este mecanismo funciona en los modos real y protegido. El CR3 contiene la base del directorio de pginas, o direccin raz, y los bits PCD y PWT. Estos bits controlan la operacin de las terminales PCD y PWT en el microprocesador. Si PCD est activo (1), la terminal PCD se convierte en uno lgico durante los ciclos de bus que no se paginen. Esto permite al hardware externo controlar la memoria de cach de nivel 2. (Tenga en cuenta que esta memoria es una memoria interna [en versiones modernas del Pentium] de alta velocidad que

FIGURA 2-11 La estructura del registro de control del microprocesador funciona como un bfer entre el microprocesador y el sistema de memoria DRAM principal.) El bit PWT tambin aparece en la terminal PWT durante los ciclos de bus que no se paginan para controlar la escritura a travs de la cach en el sistema. La direccin base del directorio de paginas localiza el directorio para la unidad de traduccin de pginas. Esta direccin localiza el directorio de pginas en cualquier lmite de 4 K en el sistema de memoria, ya que se adjunta en forma interna con 000H. El directorio de pginas contiene 1024 entradas de cuatro bytes cada una. Cada entrada en el directorio de pginas direcciona una tabla de pginas que contiene 1024 entradas. A medida que el software genera la direccin lineal, sta se descompone en tres secciones que se utilizan para acceder a la entrada en el directorio de pginas, la entrada en la tabla de pginas y la direccin de desplazamiento de la pgina de memoria. La figura 2-12 muestra la direccin lineal y su estructura para la paginacin. Observe cmo los 10 bits de ms a la izquierda direccionan una entrada en el directorio de pginas. Para la direccin lineal

28

CAPTULO 2 El microprocesador y su arquitectura

00000000H-003FFFFFH, se accede al primer directorio de pginas. Cada entrada en el directorio de paginas representan o repagina una seccin de 4 M del sistema de memoria. El contenido del directorio de pginas selecciona una tabla de pginas que esta indizada por los siguientes 10 bits de la direccin lineal (posiciones de bits 12-21). Esto significa que la direccin 00000000H-00000FFFH selecciona la entrada 0 en el directorio de pginas y la entrada 0 en la tabla de pginas. Este rango de direcciones es de 4 Kbytes. La parte de la direccin lineal correspondiente al desplazamiento (posiciones de bits 0-11) selecciona a continuacin un byte en la pgina de memoria de 4 Kbytes. En la figura 2-12, si la entrada 0 de la tabla de pginas contiene la direccin 00100000H, entonces la direccin fsica es 00100000H-00100FFFH para la direccin lineal 00000000H-00000FFFH. Esto significa que cuando el programa accede a una posicin entre 00000000H y 00000FFFH, el microprocesador direcciona fsicamente la posicin 00100000H-00100FFFH.

FIGURA 2-12 El formato para la direccin lineal (a) y una entrada en la tabla de pginas o en el directorio de pginas (b). Como el acto de repaginar una seccin de memoria de 4 Kbytes requiere del acceso al directorio de pginas y a una tabla de pginas, las cuales se encuentran en memoria, Intel ha incorporado un tipo especial de cach llamado TLB (bfer de traduccin adelantada). En el microprocesador 80486 la cach guarda las 32 direcciones de traduccin de pgina ms recientes. Esto significa que las ltimas 32 traducciones de la tabla de pginas se almacenan en el TLB, por lo que si se accede a la misma rea de memoria, la direccin ya est presente en el TLB y no se requiere el acceso al directorio de pginas ni a las tablas de pginas. Esto agiliza la ejecucin del programa. Si una traduccin no est en el TLB hay que acceder al directorio de pginas y a la tabla de pginas, lo cual requiere de un tiempo de ejecucin adicional. Los microprocesadores del Pentium al Pentium 4 contiene TLB separados para cada una de sus cachs de instruccin y de datos.

29

CAPTULO 2 El microprocesador y su arquitectura

El directorio de pginas y la tabla de pginas La figura 2-13 muestra el directorio de pginas, unas cuantas tablas de pginas y algunas pginas de memoria. Slo hay un directorio de pginas en el sistema. ste contiene 1024 direcciones con tamao de doble palabra que localiza hasta 1024 tablas de pginas. El directorio de pginas y cada tabla de pginas son de 4 Kbytes de longitud. Si se paginan todos los Gbytes de memoria, el sistema debe asignar 4 Kbytes de memoria para el directorio de pginas y 4 K por 1024, o 4 Mbytes para 1024 tablas de pginas. Esto representa una inversin considerable en recursos de memoria. El sistema DOS y el programa EMM386.EXE utilizan tablas de pginas para redefinir el rea de memoria entre las posiciones C8000H-EFFFFH como bloques de memoria superior. Esto se hace mediante una repaginacin de la memoria extendida para rellenar esta parte del sistema de memoria convencional y permitir que el DOS tenga acceso a la memoria adicional. Suponga que el programa EMM386.EXE permite el acceso al 16 Mbytes de memoria extendida y convencional a travs de la paginacin, y que las posiciones C8000H-EFFFFH deben repaginarse a las posiciones 110000-138000H, en donde las dems reas de memoria se paginan a sus posiciones normales. Dicho esquema se describe en la figura 2-14.

FIGURA 2-13 El mecanismo de paginacin en los microprocesadores del 80386 al Pentium 4.

30

CAPTULO 2 El microprocesador y su arquitectura

FIGURA 2-14 El directorio de pginas, la tabla de pginas 0 y dos pginas de memoria, observe cmo la direccin de la pgina 000C8000000C9000 se ha desplazado a 00110000-00110FFF

Aqu el directorio de pginas contiene cuatro entradas. Recuerde que cada entrada en el directorio de pginas corresponden a 4 Mbytes de memoria fsica. El sistema tambin contiene cuatro tablas de pginas con 1024 entradas cada una. Este esquema requiere un total de 16 K de memoria para las cuatro tablas de pginas y 16 bytes de memoria para el directorio de pginas. Al igual que el DOS, el programa Windows tambin repagina el sistema de memoria. La versin 3.11 de Windows soporta la paginacin slo para 16 Mbytes de memoria, debido a la cantidad de memoria requerida para almacenar las tablas de pginas. Las versiones ms recientes de Windows repaginan todo el sistema de memoria. En los microprocesadores Pentium-Pentium 4 las pginas pueden ser de 4 Kbytes de longitud o de 4 Mbytes. Aunque no hay software en la actualidad que soporte las paginas de 4 Mbytes, a medida que el Pentium 4 y versiones ms avanzadas se difundan en el rea de la computadoras personales, sin duda los sistemas operativos del futuro empezaran a soportar pginas de memoria de 4 Mbytes.

31

CAPTULO 2 El microprocesador y su arquitectura

2-5 RESUMEN

1. El modelo de programacin de los microprocesadores del 8086 al 80286 contiene registros de 8 y de 16 bits. El modelo de programacin de los microprocesadores 80386 y superiores contiene registros extendidos de 8, 16 y 32 bits, as como dos registros de segmento de 16 bits adicionales FS y GS. 2. Los registro de 8 bits son AH, AL, BH, BL, CH, CL, DH y DL. Los registros de 16 bits son AX, BX, CX, DX, SP, BP, DI y SI. Los registros de segmento son CS, DS, ES, SS, FS y GS. Los registros extendidos de 32 bits son EAX, EBX, ECX, EDX, ESP, EBP, EDI y ESI. Adems el microprocesador contiene un apuntador de instrucciones (IP/EIP) y un registro de bandera (FLAGS o EFLAGS)3. Todas las direcciones de memoria en modo real son una combinacin de una direccin de segmento ms de una direccin de desplazamiento. La posicin inicial de un segmento se define mediante el nmero de 16 bits en el registro de segmento al que se adjunta un cero hexadecimal en el extremo derecho. La direccin de desplazamiento es un nmero de 16 bits que se suma a la direccin de segmento de 20 bits para formar la direccin de memoria en modo real. 4. Todas las instrucciones (cdigo) se acceden mediante la combinacin de CS (direccin de segmento) ms IP o EIP (direccin de desplazamiento). 5. Por lo general se hace referencia a los datos a travs de una combinacin del DS (segmento de datos) y una direccin de desplazamiento o el contenido de un registro que contenga la direccin de desplazamiento. Los microprocesadores del 8086 al Pentium 4 utilizan BX, DI y SI como registro de desplazamiento predeterminados para los datos si se seleccionan registros de 16 bits. El 80386 y superiores pueden usar los registros de 32 bits EAX, EBX, ECX, EDX, EDI y ESI como registros de desplazamiento predeterminado para los datos. 6. La operacin en modo protegido permite acceder a la memoria que est por encima del primer 1 Mbyte en los microprocesadores del 80286 al Pentium 4. Este sistema de memoria extendida (XMS) se accede a travs de una direccin de segmento ms una direccin de desplazamiento, justo igual que en el modo real. La diferencia es que la direccin de segmento se almacena en un descriptor que se selecciona mediante el registro de segmento. 7. Un descriptor de modo protegido contiene una direccin base, un lmite y un byte de derechos de acceso. La direccin base localiza la direccin inicial del segmento de memoria; el limite define la ltima posicin del segmento. El byte de derechos de acceso define como se accede al segmento de memoria mediante un programa. El microprocesador 80286 permite que un segmento de memoria empiece en cualquier de sus 16 Mbytes de memoria mediante el uso de una direccin base de 24 bits. El

32

CAPTULO 2 El microprocesador y su arquitectura

80386 y superiores permiten que un segmento de memoria empiece en cualquier de sus 4 Gbytes de memoria, mediante el uso de una direccin base de 32 bits. El lmite es un nmero de 16 bits en el 80286 y un nmero de 20 bits en el 80386 y superiores. Esto permite el 80286 un lmite de 64 Kbytes en el segmento de memoria, y al 80386 y superiores un lmite de 1 Mbyte (G=0) o de 4 Gbytes (G=1) en el segmento de memoria. 8. El registro de segmento contiene tres campos de informacin en el modo protegido. Los 13 bits de ms a la izquierda del registro de segmento direccionan uno de 8192 descriptores de una tabla de descriptores. El bit TI accede a la tabla de descriptores globales (TI=0) o a la tabla de descriptores locales (TI=1). Los 2 bits de ms a la derecha del registro de segmento seleccionan el nivel de prioridad solicitado para el acceso al segmento de memoria. 9. Los microprocesadores 80286 y superiores utilizan los registros invisibles para los programas para acceder a las tablas de descriptores. Cada registro de segmento contiene una porcin de cach que se utilizan en modo protegido para guardar la direccin base, el limite y los derechos de acceso adquiridos de un descriptor. La cach permite al microprocesador acceder al segmento de memoria sin tener que volver a hacer referencia a la tabla de descriptores, hasta que se cambie el contenido del registro de segmento. 10. Una pgina de memoria tiene 4 Kbytes de longitud. La direccin lineal, como la genera un programa, puede asignarse a cualquier direccin fsica a travs del mecanismo de paginacin que se encuentra dentro de los microprocesadores del 80386 al Pentium 4. 11. La paginacin de memoria se lleva a cabo a travs de los registros de control CR0 y CR3. El bit PG de CR0 habilita la paginacin y el contenido de CR3 direcciona el directorio de pginas. Este directorio contiene hasta 2024 direcciones de tablas de pginas que se utilizan para acceder a las tablas de pginas. La tabla de pginas contiene 1024 entradas que localizan la direccin fsica de una pgina de memoria de 4 kbytes. 12. El TLB (bfer de traduccin adelantada) guarda en la cach las 32 traducciones ms recientes de tablas de pginas. Esto evita la traduccin de tablas de pginas si sta reside en el TLB, con lo cual se agiliza la ejecucin del software.

33

CONCLUSIONES

Chuc Cauich Jos Gilberto 2566 El microprocesador es la parte de la computadora diseada para llevar acabo o ejecutar los programas. Este viene siendo el cerebro de la computadora, el motor, el corazn de esta mquina. Este ejecuta instrucciones que se le dan a la computadora a muy bajo nivel haciendo operaciones lgicas simples, como sumar, restar, multiplicar y dividir. El microprocesador, o simplemente el micro, es el cerebro del ordenador. Es un chip, un tipo de componente electrnico en cuyo interior existen miles (o millones) de elementos llamados transistores, cuya combinacin permite realizar el trabajo que tenga encomendado el chip. Microprocesador CI digital, programable, que ejecuta secuencialmente una serie de instrucciones para realizar unas funciones determinadas con los datos. Chuc Cauich Julio Csar 2565 El microprocesador es la parte de la computadora diseada para llevar acabo o ejecutar los programas. Este viene siendo el cerebro de la computadora, el motor, el corazn de esta mquina. Este ejecuta instrucciones que se le dan a la computadora a muy bajo nivel haciendo operaciones lgicas simples, como sumar, restar, multiplicar y dividir. El microprocesador, o simplemente el micro, es el cerebro del ordenador. Es un chip, un tipo de componente electrnico en cuyo interior existen miles (o millones) de elementos llamados transistores, cuya combinacin permite realizar el trabajo que tenga encomendado el chip. Microprocesador CI digital, programable, que ejecuta secuencialmente una serie de instrucciones para realizar unas funciones determinadas con los datos. Edward Contreras Contreras 2575 Podemos rescatar importantes conceptos de esta investigacin, aprendimos que existen registros de 8bts de 16bits y de 32 bits. Las direcciones de memoria en modo real son una combinacin de una direccin de segmento ms una direccin de desplazamiento. La posicin inicial de un segmento se define mediante el nmero de 16 bits en el registro de segmentos al que se adjunta un cero hexadecimal en el extremo derecho. Por lo general se hace referencia a los datos a travs de una combinacin de DS, que es el segmento de datos, y una direccin de desplazamiento o el contenido de un registro que contenga la direccin de desplazamiento. Un descriptor de modo protegido contiene una direccin base, un lmite y un byte de derechos de acceso. Cutz Velazquez Nidia Gabriela 2576

El tema visto anteriormente tiene gran importancia debido al uso que se le da a los microcontroladores en la industria es por ello que se deben conocer los puntos ms importantes que se relacionan con ellos. En el trabajo documental desarrollado se tom en cuenta la manera en que estos dispositivos funcionan, empezando con su arquitectura interna, se mencion la descripcin de la funcin y el propsito de cada registro visible para un programa en los microprocesadores del 80386 al Pentium 4, con sus diversas caractersticas y modo de operacin, el registro de banderas y el propsito de cada bit de bandera. Tambin fue importante el estudio de la descripcin de como se accede a la memoria mediante las tcnicas de direccionamiento de memoria en modo real y en modo protegido, ya que con ello se conocen la diferencias y la relacin que existen entre ambos. En la paginacin de memoria se toman en cuenta los registros invisibles para un programa que existen en los microprocesadores del 80286 al Pentium 4. As como detallar la operacin del mecanismo de paginacin de memoria. Todo lo mencionado anteriormente ayuda a una mejor comprensin y aprendizaje de lo que son los microcontroladores y con ello al realizar la prctica podemos darnos cuenta de la manera en que funcionan para tener una mejor idea de ellos. Pech Uuh Gabriela 2587 Al trmino del captulo que trat de los microprocesadores, en s fue un tema interesante, ya que de esa forma, llegue a comprender su configuracin interna, su funcionamiento, sus caractersticas y conocer ms a detalle cada tipo de microprocesador, los cuales han ido mejorando para ciertas tareas en especificas, ya sean en el modo real y en el modo protegido. Lo importante es saber el modo en que trabajan los microprocesadores, para con ello realizar la programacin de manera directa e indirecta, de tal manera comunicarnos con dicho microprocesador mediante los registros adecuados. Entre estos registros se encuentran tres diferentes los cuales son los registros multipropsito, tienen como funcin principal el almacenamiento de datos y realizacin de ciertas operaciones. Tambin se encuentran los registros de propsito especial, que tienen como funcin principal la realizacin, determinacin del lugar que debe ocupar cada instruccin, as como el control y ejecucin del programa en el microprocesador. Por ltimo tenemos a los registros de segmentos los cuales son aquellos que generan direcciones de memoria cuando se combinan los registros en los microprocesadores, stos pueden ser de cuatro a seis registros de segmentos. Cada tipo de registro se utiliza de manera diferente de acuerdo al modo en el cual se trabaja en el microprocesador, es de importancia saber que en estos modos real y modo protegido, se realizan la paginacin de memoria y registros de memoria, mediante la divisin de los segmentos que se encuentran en dichos.

35

Saldivar Cabrera David Fernando 2569 Ahora en nuestra actualidad este dispositivo llamado microprocesador puede cambiar muchas caractersticas de las computadoras. Gracias a l las computadoras podrn hacerse mucho ms pequeas, ya que su estructura fsica se hace mucho ms simple. Tambin permite el mejor aprovechamiento de las bateras pues, como vimos, su tecnologa LongRun y menor nmero de componentes discretos hacen que se consuma menos energa los programas cada vez ms grandes y complejos demandan mayor velocidad en el procesamiento de informacin, lo que implica la bsqueda de microprocesadores ms rpidos y eficientes. Los avances y progresos en la tecnologa de semiconductores han reducido las diferencias en las velocidades de procesamiento de los microprocesadores con las velocidades de las memorias, lo que ha repercutido en nuevas tecnologas en el desarrollo de microprocesadores. Hay quienes consideran que en breve los microprocesadores RISC sustituirn a los CISC, pero existe el hecho que los microprocesadores CISC tienen un mercado de software muy difundido

36

BIBLIOGRAFA

Brey, Barry B., Microprocesadores Intel, Ed. Prentice May, 7a. Edicin. Captulo 2: el microprocesador y su arquitectura. Pp. 49-69.

37