Analog to Digital Converter(Atmega128)

-

Upload

meredith-moss -

Category

Documents

-

view

66 -

download

5

description

Transcript of Analog to Digital Converter(Atmega128)

KyungHee Univ. 2-1

Analog to Digital Converter(Atmega128)

KyungHee Univ. 1-2

Analog to Digital Converter

Features10-bit Resolution13 - 260 μs Conversion Time8 Multiplexed Single Ended Input

Channels7 Differential Input Channels2 Differential Input Channels with Op-

tional Gain of 10x and 200xOptional Left Adjustment for ADC Re-

sult Readout0 - VCC ADC Input Voltage RangeSelectable 2.56 V ADC Reference Volt-

ageFree Running or Single Conversion

ModeInterrupt on ADC Conversion Complete

KyungHee Univ. 1-3

ATmega128 ADC

8 채널 아날로그 입력은 PORT F 를 통해 입력되며 , Analog Multiplexer 에 의해 A/D 변환기에 연결된다 .

변환 기간 동안 아날로그 입력전압을 일정하게 하는 Sample/Hold 회로를 내장 하고 있다 .

기준전압 VREF 는 A/D 변환되는 전압의 범위를 나타내며 , 단 극성 모드에서 VREF 는 0x3FF 로 변환된다 . VREF 는 AVCC, 내부 2.56V, 외부 AREF 단자에 공급되는 전압 중에서 선택 한다 .

단 극성인 경우 0~ VREF 의 입력전압이 공급되어 x000~0x3FF(0~1023) 의 디지털 값으로 변환되며 ,

차동입력의 경우 차동 입력전압이 2 의 보수 0x200~0x1FF(-512~511) 로 변환된다 .

변환결과는 16 비트 A/D 변환기 데이터 레지스터에 좌측 또는 우측으로 정렬되어 저장

KyungHee Univ. 2-4

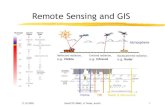

Analog to Digital Converter Block Schematic

KyungHee Univ. 2-5

ADC Prescaler

KyungHee Univ. 2-6

ADC Conversion Time

ADC Conversion ResultSingle Ended Conversion

ADC = (Vin *1024) / VREF

Differential Channel ConversionADC = ((Vpos – VNEG) * Gain * 512) / VREF

KyungHee Univ. 1-7

ATmega128 ADC 레지스터

ADCMUX (ADC Multiplexer Selection Re-gister)ADC 기준전압 (reference voltage) 선택ADC 변환 값 정렬 방법 지정ADC 입력채널 지정

(ADCSRA)ADC Control and Status Register ADC Enable/DisableADC Start ConversionADC Free Running SelectADC Interrupt FlagADC Interrupt Enable/DisableADC Clock Division Factor

ADCL, ADCH ( ADC Data Register)

KyungHee Univ. 1-8

Register Description

ADMUX - ADC Multiplexer Selection Re-gisterA/D 변환기의 아날로그 입력채널 선택 , A/D 변환의 기준

전압을 설정하거나 변환결과의 저장 형식을 지정

Bit 7:6 – REFS1:0: Reference Selection Bits ADC 기준 전압을 설정하는 비트 , 만약 이 Bit(7:6)

값들이 ADC 변환 도중에 변경된다면 , 그 변환이 끝난 이후부터 변경된 값이 적용된다 .

KyungHee Univ. 1-9

Register Description

Bit 5 – ADLAR: ADC Left Adjust Result A/D 변환결과를 ADCH:ADCL 에 저장하는 형식을 지정 0: 하위부터 10 비트를 사용 , 1: 상위부터 10 비트를

사용Bits 4:0 – MUX4:0: Analog Channel and Gain Selection

Bits

KyungHee Univ. 1-10

Bits 4:0 – MUX4:0: Analog Channel and Gain Selection Bits

KyungHee Univ. 1-11

Bits 4:0 – MUX4:0: Analog Channel and Gain Selection Bits

(1) 은 offset calibration 에 사용 한다 .

KyungHee Univ. 1-12

ADC Control and Status Register A

Bit 7 – ADEN: ADC Enable ADEN = 1 ; ADC EnablesADEN = 0 ; ADC Disables

Bit 6 – ADSC: ADC Start ConversionSingle Conversion mode 일 경우

ADSC 에 1 을 Write ; A/D 변환이 시작 , 변환완료 시 0로 Reset

ADSC 에 0 을 Write ; No effectFree Running mode 일 경우

ADSC 에 1 을 Write ; Start the first conver-sion

KyungHee Univ. 1-13

ADC Control and Status Register A

Bit 5 – ADFR: ADC Free Running Se-lect

Bit 4 – ADIF: ADC Interrupt FlagBit 3 - ADIE: ADC Interrupt EnableBits 2:0 – ADPS2:0: ADC Prescaler Se-

lect BitsXTAL frequency 과 ADC Input clock 의 divi-

sion factor

KyungHee Univ. 1-14

ADC Control and Status Register A

Bit 4 – ADIF: ADC Interrupt FlagBit 3 - ADIE: ADC Interrupt EnableBits 2:0 – ADPS2:0: ADC Prescaler Se-

lect Bits XTAL frequency 과 ADC Input clock 의 division factor

KyungHee Univ. 1-15

ADC Register

Right Adjusted Mode: ADLAR = 0

Left Adjusted Mode: ADLAR = 1

KyungHee Univ. 2-16

ATmega128 ADC 프로그램 예

cho_adc_basic_lcd 참고 요