ΕΓΧΕΙΡΙ∆ΙΟ ΧΡΗΣΗΣxanthippi.ceid.upatras.gr/people/psarakis/courses/... ·...

Transcript of ΕΓΧΕΙΡΙ∆ΙΟ ΧΡΗΣΗΣxanthippi.ceid.upatras.gr/people/psarakis/courses/... ·...

ΕΕΓΓΧΧΕΕΙΙΡΡΙΙ∆∆ΙΙΟΟ ΧΧΡΡΗΗΣΣΗΗΣΣ

DDSSKK TTMMSS332200CC66771111

II

ΠΠεερριιεεχχόόµµεενναα ΚΕΦΑΛΑΙΟ 1..................................................................................................................................1 ΚΕΦΑΛΑΙΟ 1

1.1 Εισαγωγή.............................................................................................................................. 1 1.2 Γενική περιγραφή της πλατφόρµας TMS320C6711 DSK................................................... 1

1.2.1 Σήµατα χρονισµού ........................................................................................................ 3 1.2.2 Θύρα Εισόδου / Εξόδου................................................................................................ 4 1.2.3 ∆ιακόπτες καθορισµένοι από το χρήστη και ενδείξεις ................................................. 4 1.2.4 Έλεγχος Επανεκκίνησης (Reset) .................................................................................. 5 1.2.5 Ελεγκτής παράλληλης θύρας ........................................................................................ 5 1.2.6 Εξωτερική µνήµη.......................................................................................................... 5

1.3 Κύκλωµα αναλογικής αλληλεπίδρασης ............................................................................... 7 1.3.1 Η συσκευή TLC320AD535 .......................................................................................... 8

1.3.1.1 Περιγραφή λειτουργιών του TLC320AD535........................................................ 9 1.3.1.2 Περιγραφή λειτουργιών του codec...................................................................... 11 1.3.1.3 ADC κανάλι σήµατος .......................................................................................... 11 1.3.1.4 DAC κανάλι σήµατος .......................................................................................... 12 1.3.1.5 Οι διαµορφώσεις sigma-delta του ΑDC και του DAC........................................ 12 1.3.1.6 Φίλτρα αποδεκατισµού και φίλτρα παρεµβολής ................................................. 12 1.3.1.7 ∆ιακοπή τροφοδοσίας µέσω λογισµικού (Power Down) .................................... 12 1.3.1.8 Σειριακές επικοινωνίες ........................................................................................ 13

1.4 Σύνοψη ............................................................................................................................... 15 ΚΕΦΑΛΑΙΟ 2................................................................................................................................17 ΚΕΦΑΛΑΙΟ 2

2.1 Εισαγωγή............................................................................................................................ 17 2.2 Η οικογένεια TMS320C6000............................................................................................. 17 2.3 Γενική περιγραφή του επεξεργαστή TMS320C6711......................................................... 20 2.4 Ανάλυση της κεντρικής µονάδας επεξεργασίας (DSP core).............................................. 24 2.5 Η µορφή των ακεραίων και κινητής υποδιαστολής λέξεων............................................... 26 2.6 Περιγραφή του Enhanced Direct Memory Access (EDMA) Controller............................ 30

2.6.1 Ορολογία για τον EDMA............................................................................................ 31 2.6.2 Καταχωρητές Ελέγχου και Επεξεργασία Γεγονότων ................................................ 33 2.6.3 Κωδικοποιητής Γεγονότων ......................................................................................... 34 2.6.4 Μνήµη RAM παραµέτρων (PaRAM)......................................................................... 35 2.6.5 EDMA Παράµετροι Μεταφοράς ................................................................................ 37

2.6.5.1 Παράµετρος Επιλογών (OPT) ............................................................................. 38 2.6.5.2 ∆ιεύθυνση Πηγής / Προορισµου (SRC/DST) .................................................... 40 2.6.5.3 Μετρητής Στοιχείων (ELECNT)......................................................................... 41 2.6.5.4 Μετρητής Πλαισίου / Πίνακα (FRMCNT).......................................................... 41 2.6.5.5 Περιεχόµενα ∆είκτη στοιχείου / ∆είκτη πλαισίου (ELEIDX / FRMIDX).......... 41 2.6.5.6 Επαναφόρτωση Μετρητή Στοιχείου (ELERLD)................................................. 41 2.6.5.7 ∆ιεύθυνση Σύνδεσης (LINK) .............................................................................. 42

2.6.6 Αρχικοποίηση EDMA Μεταφοράς............................................................................. 42 2.6.7 Συγχρονισµός των EDMA Μεταφορών ..................................................................... 43 2.6.8 Τύποι EDMA Μεταφορών ......................................................................................... 43 2.6.9 Ενηµέρωση των Μετρητών Στοιχείου (ELECNT) και Πλαισίου / Πίνακα (FRMCNT).............................................................................................................................................. 46 2.6.10 Element Count Reload (ECRLD) ............................................................................. 47 2.6.11 SRC/DST Address Updates ...................................................................................... 47 2.6.12 Παραγωγή διακοπών από το EDMA ........................................................................ 48

III

2.6.13 Σύνδεση EDMA Μεταφορών ................................................................................... 49 2.6.14 Chaining EDMA Καναλιών µέσω ενός Γεγονότος .................................................. 50 2.6.15 ∆ιαιτησία και επεξεργασία προτεραιοτήτων ............................................................ 51

2.7 Πολυκαναλική Αποµονωµένη Σειριακή Θύρα (Multichannel Buffered Serial Port) ........ 52 2.7.1 McBSP ∆ιεπαφή Σηµάτων και Καταχωρητών ........................................................... 53 2.7.2 Προγραµµατισµός Σειριακής Θύρας .......................................................................... 56 2.7.3 Kαταχωρητές Ελέγχου Λήψης κι Αποστολής: RCR and XCR .................................. 60 2.7.4 Αποστολή και Λήψη ∆εδοµένων................................................................................ 63 2.7.5 Αρχικοποίηση της Σειριακής Θύρας: (R/X)RST, GRST, and RESET....................... 64 2.7.6 Καθορισµός Κατάστασης Ετοιµότητας ...................................................................... 66 2.7.7 Κατάσταση Ετοιµότητας Αποστολής: XEVT, XINT, και XRDY ............................. 66 2.7.8 CPU ∆ιακοπές: (R/X)INT .......................................................................................... 67 2.7.9 Τυπική λειτουργία του McBSP................................................................................... 67 2.7.10 Μέγιστη Συχνότητα µεταφοράς πλαισίου ................................................................ 68 2.7.11 ∆ιάταξη Bit (Bit Ordering) ....................................................................................... 69 2.7.12 Προγραµµατιζόµενο Ρολόι και Πλαισίωση (Framing)............................................. 69 2.7.13 Γεννήτρια Ρυθµού ∆ειγµατοληψίας, Χρονισµός και Πλαισίωση (Sample Rate Generator Clocking and Framing) ........................................................................................ 70 2.7.14 Επιλογή πολυκαναλικής λειτουργίας (Multichannel Selection Operation) .............. 70

2.8 ∆ιεπαφή Θύρας-Ξενιστή(Host Port Interface) ................................................................... 71 2.8.1 Εξωτερικό Interface του HPI ...................................................................................... 72

Host Connection ............................................................................................................... 73 2.9 ∆ιεπαφή εξωτερικής µνήµης (External Memory Interface - EMIF) .................................. 74

2.9.1 SDRAM ∆ιεπαφή ....................................................................................................... 75 2.9.2 ∆ιεπαφή SBSRAM ..................................................................................................... 76 2.9.3 Ασύγχρονη ∆ιεπαφή ................................................................................................... 76 2.9.4 Εύρος µνήµης και τρόπος διαχείρισης των bytes ....................................................... 76

2.10 ∆ίαυλος Επέκτασης........................................................................................................... 76 2.11 PCI ................................................................................................................................... 77 2.12 Χρονιστές ......................................................................................................................... 78

2.12.1 Καταχωρητές διαµόρφωσης των χρονιστών............................................................. 79 2.12.2 Επανατοποθέτηση (resetting) των Χρονιστών κι Ενεργοποίηση της Μέτρησης: GO and HLD ............................................................................................................................... 80 2.12.3 Μέτρηση Χρονιστή................................................................................................... 80

2.13 Επιλογέας ∆ιακοπών και Εξωτερικές ∆ιακοπές .............................................................. 81 2.13.1 Καταχωρητές επιλογής διακοπής (Interrupt Selector).............................................. 82 2.13.2 ∆ιαµόρφωση του Επιλογέα ∆ιακοπών...................................................................... 82

2.14 Σύνοψη ............................................................................................................................. 82 ΚΕΦΑΛΑΙΟ 3................................................................................................................................85 ΚΕΦΑΛΑΙΟ 3

3.1 Εισαγωγή............................................................................................................................ 85 3.2 ∆ιαχείριση των projects ..................................................................................................... 85 3.3 Η διαδικασία build ............................................................................................................. 87 3.4 Εκσφαλµάτωση (Debugging)............................................................................................. 88 3.5 Σύνοψη ............................................................................................................................... 89

Βιβλιογραφία..................................................................................................................................91 Βιβλιογραφία

IV

ΛΛίίσστταα ΣΣχχηηµµάάττωωνν Σχήµα 1.1 : Κάτοψη της αναπτυξιακής πλατφόρµας TMS320C6711 DSK...................................... 2 Σχήµα 1.2 : Σχηµατικό ∆ιάγραµµα των βασικών στοιχείων και των διασυνδέσεων της

αναπτυξιακής πλατφόρµας TMS320C6711 DSK ..................................................................... 3 Σχήµα 1.3 : Οι τοπολογίες του δίαυλου δεδοµένων και διευθύνσεων του EMIF ........................... 6 Σχήµα 1.4 : Σχηµατικό διάγραµµα του AIC.................................................................................... 7 Σχήµα 1.5 : Το ολοκληρωµένο TLC320AD535.............................................................................. 9 Σχήµα 1.6 : Το διάγραµµα λειτουργιών του TLC320AD535 .......................................................... 9 Σχήµα 1.7 : Format δεδοµένων των DIN και DOUT για τη πρωτεύουσα επικοινωνία ................. 14 Σχήµα 1.8 : Format δεδοµένων των DIN και DOUT για τη δευτερεύουσα επικοινωνία ............... 15 Σχήµα 2.1 : Η κάτοψη του ολοκληρωµένου TMS320C6711 ......................................................... 21 Σχήµα 2.2 : Σχηµατικό ∆ιάγραµµα του επεξεργαστή TMS320C6711 ........................................... 22 Σχήµα 2.3 : Σχηµατικό διάγραµµα του ελεγκτή EDMA ................................................................ 31 Σχήµα 2.4 : Καταχωρητές Ελέγχου EDMA ................................................................................... 33 Σχήµα 2.5 : Πεδία Παραµέτρου της PaRAM ................................................................................. 38 Σχήµα 2.6 : Παράµετρος ΟPT....................................................................................................... 40 Σχήµα 2.7 : Γεγονότα Συγχρονισµού EDMA Καναλιού................................................................. 43 Σχήµα 2.8 : Ενηµέρωση Μετρητών ............................................................................................... 46 Σχήµα 2.9 : Τρόποι Ανανέωσης ∆ιεύθυνσης.................................................................................. 47 Σχήµα 2.10 : Αντιστοίχιση TCC και CIPR .................................................................................... 49 Σχήµα 2.11 : Συνθήκες Τερµατισµού Καναλιού ............................................................................ 50 Σχήµα 2.12 : Προτεραιότητες ........................................................................................................ 51 Σχήµα 2.13 : ∆ιάγραµµα McBSP................................................................................................... 53 Σχήµα 2.14 : MCBSP - SPCR Καταχωρητής ................................................................................ 58 Σχήµα 2.15 : MCBSP - PCR Καταχωρητής .................................................................................. 59 Σχήµα 2.16 : MCBSP – RCR/XCR Καταχωρητής ......................................................................... 63 Σχήµα 2.17 : Κύκλωµα Επιλογής Χρονισµού και Framing ........................................................... 69 Σχήµα 2.18 : Κύκλωµα Παραγωγής Ρυθµού ∆ειγµατοληψίας ....................................................... 70 Σχήµα 2.19 : Το block διάγραµµα του ΗΡΙ ................................................................................... 72 Σχήµα 2.20 : Σήµατα της ΕΜΙF .................................................................................................... 75 Σχήµα 2.21 : Καταχωρητές της ΕΜΙF ........................................................................................... 75 Σχήµα 2.22 : ∆ίαυλος Επέκτασης .................................................................................................. 77 Σχήµα 2.23 :Σχηµατικό διάγραµµα PCI θύρας.............................................................................. 78 Σχήµα 2.24 : ∆ιάγραµµα Χρονιστών ............................................................................................. 79 Σχήµα 2.25 : Καταχωρητές Χρονισµού ......................................................................................... 80 Σχήµα 2.26 : ∆ιαθέσιµες ∆ιακοπές................................................................................................ 81 Σχήµα 3.1 : Tο Project View παράθυρο ........................................................................................ 86 Σχήµα 3.2 : Tο παράθυρο Edit Variable ...................................................................................... 89

V

VI

ΛΛίίσστταα ΠΠιιννάάκκωωνν

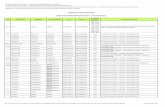

Πίνακας 2.1 : Περιεχόµενα PaRAM .............................................................................................. 37 Πίνακας 2.2 : ∆ιευθύνσεις των McBSP καταχωρητών................................................................... 55 Πίνακας 2.3 : Τρόποι προσπέλασης των McBSP καταχωρητών .................................................... 55 Πίνακας 2.4 : McBSP σήµατα διεπαφής ........................................................................................ 55 Πίνακας 2.5 :Σήµατα διακοπής από τον McBSP .......................................................................... 55 Πίνακας 2.6 :Κατάσταση των ακροδεκτών της McBSP µετά από reset ......................................... 64 Πίνακας 2.7 : Σήµατα του host port interface................................................................................ 74 Πίνακας 2.8 : Πίνακας µνήµης (µemory map) του επεξεργαστή .................................................... 83 Πίνακας 3.1 : Υποθέσεις µε βάση τις καταλήξεις των αρχείων ...................................................... 87

VII

VIII

ΚΚΕΕΦΦΑΑΛΛΑΑΙΙΟΟ 11 Η πλατφόρµα TMS320C6711 DSK

1.1 Εισαγωγή Στο κεφάλαιο θα γίνει µια γενική αναφορά στα χαρακτηριστικά / δυνατότητες που προσφέρει η αναπτυξιακή πλατφόρµα TMS320C6711 DSK. Συγκεκριµένα, παρουσιάζονται τα κύρια χαρακτηριστικά της πλατφόρµας µε σκοπό να γίνουν κατανοητές οι λειτουργίες της, καθώς και οι λύσεις που παρέχονται για την υλοποίηση αλγορίθµων. Βασικό συστατικό της πλατφόρµας, το οποίο θα αναλυθεί σε ξεχωριστή ενότητα, αποτελεί το αναλογικό κύκλωµα αλληλεπίδρασης (analog interface circuit), που χρησιµοποιείται για τη µετατροπή του ψηφιακού σήµατος σε αναλογικό και αντίστροφα (D/A και A/D µετατροπέας). 1.2 Γενική περιγραφή της πλατφόρµας TMS320C6711 DSK Η συγκεκριµένη πλατφόρµα (Σχήµα 1.1) αναπτύχθηκε από την Texas Instruments (TI) µε σκοπό να προσφέρει ένα περιβάλλον ανάπτυξης χαµηλού κόστους, το οποίο παράλληλα να είναι εύκολο στη χρήση του. Τα χαρακτηριστικά υψηλής απόδοσης που διαθέτει η κάρτα εξασφαλίζονται από τις δυνατότητες που παρέχει ο επεξεργαστής στον οποίο βασίζεται και ο οποίος την καθιστά µια από τις πιο αποτελεσµατικές αναπτυξιακές πλατφόρµες. Το DSK αλληλεπιδρά µε τον υπολογιστή µέσω της παράλληλης θύρας και έτσι επιτρέπει την αποδοτική ανάπτυξη και εξέταση των εφαρµογών του χρήστη. Παρακάτω παρουσιάζουµε, επιγραµµατικά, τα βασικά συστατικά µέρη από τα οποία αποτελείται η πλατφόρµα καθώς και τα βασικά χαρακτηριστικά της :

• Τον ψηφιακό επεξεργαστή σήµατος ‘C6711DSP’ ικανό να εκτελεί 900 εκατοµµύρια εντολές κινητής υποδιαστολής το δευτερόλεπτο (MFLOPS) • Υποστήριξη διπλού σήµατος χρονισµού, ένα για την ΚΜΕ στα 150MHz κι ένα για την αλληλεπίδραση µε την εξωτερική µνήµη (EMIF) στα 100MHz • Ελεγκτή παράλληλης θύρας (PPC) που επιτρέπει την αλληλεπίδραση µε την παράλληλη

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

θύρα του υπολογιστή µας (host PC) • 16M Bytes των 100MHz σύγχρονη δυναµική RAM (SDRAM) • 128K Bytes ROM • 8-bit memory – mapped θύρα εισόδου/εξόδου • ∆υνατότητα εξοµοίωσης JTAG (Joint Test Action Group) µέσω της παράλληλης θύρας και εξωτερική υποστήριξη µέσω του XDS510 • Host Port Interface (HPI) που εξασφαλίζει πρόσβαση σ’ όλες τις µνήµες του επεξεργαστή µέσω της παράλληλης θύρας • Κωδικοποιητή/Αποκωδικοποιητή audio σηµάτων των 16 bits • Ρυθµιστής τάσης πάνω στη πλακέτα για παροχή συνεχούς ρεύµατος 1.8 και 3.3V • 6 φωτεινές ενδεικτικές δίοδοι (LEDs) για διάφορες λειτουργίες • Εξωτερική παροχή ρεύµατος και ΙΕΕΕ 1284 παράλληλο καλώδιο • Επεκτάσιµη µνήµη και περιφερειακός συνδετήρας για υποστήριξη θυγατρικής κάρτας (daughterboard)

Σχήµα 1.1 : Κάτοψη της αναπτυξιακής πλατφόρµας TMS320C6711 DSK

2

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

Σχήµα 1.2 : Σχηµατικό ∆ιάγραµµα των βασικών στοιχείων και των διασυνδέσεων της αναπτυξιακής πλατφόρµας TMS320C6711 DSK

1.2.1 Σήµατα χρονισµού Το ‘C6711 DSK, όπως ήδη αναφέρθηκε, υποστηρίζει δυο σήµατα χρονισµού, όπως ήδη αναφέρθηκε, γεγονός που επιτρέπει στη CPU να τρέχει στη µια συχνότητα, και στην εξωτερική σύγχρονη µνήµη (ΕΜΙF) να τρέχει στην άλλη. Συγκεκριµένα η ΚΜΕ λειτουργεί στα 150MHz ενώ η EMIF στα 100ΜΗz.

3

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

Για την παραγωγή των σηµάτων χρονισµού της ΚΜΕ (CLKIN) και του ΕΜΙF (ECLKIN) , το DSK χρησιµοποιεί έναν οικονοµικό ταλαντωτή µαζί µε εξωτερικά χρονιζόµενους πολλαπλασιαστές. Επιπλέον, χρησιµοποιεί και µία ειδική συσκευή, την SN74LVTH125, η οποία παρέχει σήµατα χρονισµού τον ‘C6711, και προσφέρει πολλαπλές λειτουργίες όπως µετατροπές του επιπέδου σήµατος από 5V σε 3.3V και έλεγχο ακµής του ρολογιού σε περιπτώσεις ταχύτατης αλλαγής που απαιτεί ο DSP. 1.2.2 Θύρα Εισόδου / Εξόδου Το DSK διαθέτει µία θύρα εισόδου / εξόδου (Ι/Ο) των 8 bits και τη βοήθεια της συσκευή SN74LVTH16374 καθορίζει αν η θύρα χρησιµοποιείται ως είσοδος ή έξοδος κάθε φορά. Η θύρα αυτή είναι συνδεδεµένη µε το υψηλότερο byte του δίαυλου δεδοµένων (data bus). Η Ι/Ο θύρα συγχρονίζεται από το ΕMIF ρολόι ενώ ένα ενσωµατωµένο PAL (Programmable Array Logic) καθορίζει τη κατεύθυνση των σηµάτων ελέγχου (είσοδος ή έξοδος). Η Ι/Ο θύρα έχει πολλές χρήσεις. Η θύρα εισόδου συνδέεται µε τρία DIP switches, τα οποία, όπως θα δούµε στην επόµενη παράγραφο, µπορούν να καθοριστούν από το χρήστη, τρεις DSK διορθωτικές αντιστάσεις (PWB) και δύο σήµατα κατάστασης για το θυγατρική κάρτα. Η θύρα εξόδου συνδέεται µε τρία LEDs, καθοριζόµενα από το χρήστη, και δύο σήµατα ελέγχου για το θυγατρική κάρτα. Τα εναποµείναντα 5 bits, µένουν αχρησιµοποίητα και δε συνδέονται. 1.2.3 ∆ιακόπτες καθορισµένοι από το χρήστη και ενδείξεις Το ‘C6711 DSK διαθέτει ένα τεσσάρων θέσεων DIP διακόπτη. Όλες οι θέσεις του διακόπτη θέτονται στην ‘υψηλή’ θέση όταν ανοίγει και στην ‘χαµηλή’ όταν κλείνει. Τρεις από τις θέσεις αυτές καθορίζονται από τον ίδιο τον χρήστη (µέσω των τιµών 0 ή 1 που παίρνουν οι θέσεις USER_SW1 ως USER_SW3) κι είναι προσβάσιµες µέσω της Ι/Ο θύρας. Η τέταρτη θέση είναι συνδεδεµένη σε ένα σηµείο πάνω στη πλατφόρµα για να µπορεί να χρησιµοποιηθεί για έλεγχο από το χρήστη και όχι από την Ι/Ο θύρα. Τρεις ενδείξεις LED, των οποίων η λειτουργία µπορεί να καθοριστεί από το χρήστη, είναι προσπελάσιµες µέσω της I/O θύρας. Η τιµή 0 στο κατάλληλο bit της Ι/Ο θύρας έχει ως αποτέλεσµα ν’ ανάβει το αντίστοιχο LED. Αντίθετα, υψηλή τιµή στο κατάλληλο bit στην Ι/Ο θύρα σβήνει το αντίστοιχο LED.

4

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

1.2.4 Έλεγχος Επανεκκίνησης (Reset) H Programmable Array Logic συνεργάζεται άµεσα µε τον επόπτη τροφοδοσίας τάσης TPS3307-33 για να παρέχει διάφορους τύπους σηµάτων reset στο DSK. Μία ένδειξη LED ανάβει όσο ο DSP διατηρείται σε κατάσταση reset. Υπάρχουν τρεις πηγές παραγωγής ενός σήµατος reset :

1. Ένα κουµπί για το reset του codec, του daughterboard και του DSP 2. Resets που χρησιµοποιεί ο επόπτης τάσης τα οποία κάνουν reset όλα τα ολοκληρωµένα κυκλώµατα που µπορούν να δεχθούν το σήµα αυτό 3. Resets µέσω του ελεγκτή της παράλληλης θύρας από τον host µε έλεγχο από το λογισµικό για να γίνει reset ο Test Bus Controller (TBC) ή / και ο DSP.

Ο επόπτης της τροφοδοσίας τάσης TPS3307-33 βεβαιώνει ένα αδρανές low reset στην PAL όταν κάποια από τις ψηφιακές πηγές είναι κάτω από κάποια καθορισµένα επίπεδα, π.χ. κατά την τροφοδοσία µε ρεύµα ή τη διακοπή του ηλεκτρικού ρεύµατος στη πλατφόρµα. Ο ελεγκτής αλληλεπίδρασης της παράλληλης θύρας παρέχει ενεργητικές low reset εξόδους στον DSP και στον ΤΒC για να πραγµατοποιηθεί ο έλεγχος από το λογισµικό του host υπολογιστή. ∆ύο από τους ελεγκτές αυτούς που αφορούν τις γενικού σκοπού εξόδους, παρέχουν ανεξάρτητα σήµατα reset του DSP και του TBC µέσω λογισµικού του host υπολογιστή. Το DSK, όµως, δε προσφέρει ένα ξεχωριστό σήµα reset για το daughterboard. 1.2.5 Ελεγκτής παράλληλης θύρας Το DSK χρησιµοποιεί ένα σύστηµα αλληλεπίδρασης παράλληλης θύρας για να ελέγχει τη µεταφορά των πληροφοριών µεταξύ του host και του DSK. Ο ελεγκτής παράλληλης θύρας (Parallel Port Controller PPC) παρέχει ένα τρόπο αναγέννησης των σηµάτων από τη θύρα εκτυπωτή του PC σε πληροφορία κατάλληλη για το δίαυλο ISA. Κατά την αντίστροφη διαδικασία µετατρέπει 8-bit και 16-bit ISA δεδοµένα σε τµήµατα των 4-bit ή 8-bit, κατάλληλα για τη παράλληλη θύρα. 1.2.6 Εξωτερική µνήµη Το DSK διαθέτει ένα σύνολο από 4M λέξεις (words) των 32 bits µε ταχύτητα προσπέλασης 10ns(100MHz) SDRAM, 128KΒ flash ROM και µια memory-mapped θύρα εισόδου – εξόδου των 8 bits. Επίσης παρέχεται ένας διασυνδετής για δυνατότητα επέκτασης µνήµης. Η εξωτερική SDRAM λειτουργεί στα 3.3V.

5

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

H 3.3V SDRAM που χρησιµοποιείται στο DSK δε χρειάζεται να χρησιµοποιήσει κάποια glue logic για να αλληλεπιδράσει µε το DSP, γιατί το ‘C6711 EMIF παρέχει όλα τα απαραίτητα σήµατα ελέγχου και ανανέωσης. Η SDRAM πρέπει να ανανεώνεται περιοδικά για να διατηρεί τα δεδοµένα της. Το DSK χρησιµοποιεί τη δυνατότητα ανανέωσης που παρέχει ο DSP για την SDRAM. Για να γίνει αυτό, το RFEN bit στο καταχωρητή ελέγχου της SDRAM πρέπει να είναι τοποθετηµένο στο λογικό 1. Επιπλέον, το DSK διαθέτει µια 128KΒ flash ROM µνήµη, προγραµµατιζόµενη και διαγράψιµη. Τα 128KΒ ασύγχρονης µνήµης καταλαµβάνουν τα 128ΚΒ LSBs από τα 256ΜΒ του χώρου διευθύνσεων CE1. O δίαυλος δεδοµένων των 8 bits της συσκευής συνδέεται µε το χαµηλότερο byte του δίαυλου δεδοµένων του επεξεργαστή ‘C6711. Η µνήµα αυτή επιτρέπει στο DSK να κάνει boot αυτόµατα µια εφαρµογή κατά τη παροχή ρεύµατος ή / και κατά τη διαδικασία reset. Για παράδειγµα, ο κώδικας του Power-On Self-Test(POST), που αποτελεί ένα τεστ για την εξέταση της καλής λειτουργίας της κάρτας, αντιγράφεται από τη µνήµη αυτή στο DSP και εκτελείται κατά τη διαδικασία reset. Επιπλέον, αχρησιµοποίητα τµήµατα της µνήµης µπορούν να χρησιµοποιηθούν για εφαρµογές του χρήστη. Για την καλύτερη κατανόηση της διεπαφής (interface) της εξωτερικής µνήµης, παρέχονται οι τοπολογίες του δίαυλου διευθύνσεων και του δίαυλου δεδοµένων :

Σχήµα 1.3 : Οι τοπολογίες του δίαυλου δεδοµένων και διευθύνσεων του EMIF

6

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

1.3 Κύκλωµα αναλογικής αλληλεπίδρασης Το ‘C6711 DSK περιλαµβάνει ένα κύκλωµα αναλογικής αλληλεπίδρασης (analog interface circuit AIC) µε το οποίο γίνεται η µετατροπή της αναλογικής πληροφορίας εισόδου στη κάρτα σε ψηφιακή καθώς επίσης και η αντίστροφη διαδικασία(A/D και D/A αντίστοιχα). Τα βασικά χαρακτηριστικά του AIC είναι:

• 16-bit επεξεργασία σήµατος • Ανεξάρτητα κανάλια φωνής και δεδοµένων – µονό το κανάλι φωνής χρησιµοποιείται από το DSK • Συχνότητα δειγµατοληψίας στα 8ΚΗz • Ξεχωριστές καταστάσεις διακοπής τροφοδοσίας για τα κανάλια φωνής και δεδοµένων • Προγραµµατιζόµενοι ενισχυτές • Οδηγός(driver) 60-Ω ακουστικών µε προγραµµατιζόµενο ενισχυτή • Υποστήριξη για µικρόφωνα που διαθέτουν αυτόνοµη τροφοδοσία • Μια 3.5-mm(1/8 inch) µονοφωνική υποδοχή εισόδου • Μια 3.5-mm(1/8 inch) στερεοφωνική υποδοχή εξόδου

Παρακάτω παρουσιάζεται το σχηµατικό διάγραµµα του αναλογικού κυκλώµατος αλληλεπίδρασης στο οποίο φαίνονται τα βασικά του µέρη :

Σχήµα 1.4 : Σχηµατικό διάγραµµα του AIC

Όπως φαίνεται και στο παραπάνω σχήµα κυρίαρχο ρόλο στο κύκλωµα κατέχει ο κωδικοποιητής/αποκωδικοποιητής TLC320AD535 που είναι µια οικονοµική συσκευή που απαιτεί

7

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

τη χρήση ενός µικρού αριθµού επιπρόσθετων στοιχείων για τη λειτουργία της. Η συγκεκριµένη συσκευή είναι ιδιαίτερα σηµαντική και για αυτό το λόγο αναλύεται στη σχέση. 1.3.1 Η συσκευή TLC320AD535 Ο κωδικοποιητής/αποκωδικοποιητής (codec) διπλού καναλιού φωνής/δεδοµένων TLC320AD535 είναι µια συσκευή συνδυασµού σηµάτων ευρείας ζώνης. Το ολοκληρωµένο αποτελείται από έναν δι-κάναλο codec και ένα υβριδικό αναλογικό κύκλωµα µε δύο ανεξάρτητες σειριακές θύρες για επικοινωνία µε το host επεξεργαστή και εξωτερικές αντιστάσεις και πυκνωτές για το καθορισµό του κέρδους ενίσχυσης του σήµατος καθώς και των πόλων του φίλτρου. Τα περισσότερα από τα χαρακτηριστικά που αναφέρθηκαν παραπάνω για τον AIC ανήκουν στο TLC320AD535 ενώ µπορούµε, επιπλέον, να αναφέρουµε επιπροσθέτως τα ακόλουθα χαρακτηριστικά:

• Αναλογική, ψηφιακή και ρυθµιζόµενη τροφοδοσία: 5V ή 3.3V • Ανεξάρτητα κανάλια φωνής και ήχου µε συχνότητες δειγµατοληψίας µέχρι και τα 11.025kHz • ∆υναµικό εύρος των 80 dB στα κανάλια δεδοµένων και φωνής • Συνολικό Signal-to-Noise + παραµόρφωση στα 77dB για τον ADC • Συνολικό Signal-to-Noise + παραµόρφωση στα 74dB για τον DAC • 600Ω TAPI drivers των καναλιών του ήχου και δεδοµένων • 8Ω ΑΤ41 οδηγός ηχείων µε προγραµµατιζόµενο ενισχυτή • Μέγιστο bias µικροφώνου των 5mA στα 2.5/1.5 V • Μέγιστο handset reference των 2.5mA στα 2.5/1.5 V • Μέγιστη τάση αναφοράς του καναλιού δεδοµένων των 10mA στα 2.5/1.5 V • 5/3.3V MVDD power reset κύκλωµα • Κύκλωµα εγγραφής της flash µνήµης • ∆ιαθέσιµο σε 64-pin PM (QFP) πακέτο που λειτουργεί από –40οC ως 85oC

Το ολοκληρωµένο, οι λειτουργίες και τα βασικά µέρη του TLC320AD535 φαίνονται στα ακόλουθα σχήµατα :

8

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

Σχήµα 1.5 : Το ολοκληρωµένο TLC320AD535

Σχήµα 1.6 : Το διάγραµµα λειτουργιών του TLC320AD535 1.3.1.1 Περιγραφή λειτουργιών του TLC320AD535 Το τµήµα του codec του TLC320AD535 πραγµατοποιεί τις λειτουργίες που απαιτούνται για τα δυο κανάλια A/D και D/A µετατροπής, για το χαµηλοπερατό φιλτράρισµα, για τον έλεγχο της αναλογικής εισόδου και των ενισχυµένων εξόδων, για την εσωτερική υπερδειγµατοληψία µαζί µε τον εσωτερικό υποβιβασµό και παρεµβολή καθώς και για τις δυο σειριακές θύρες των 16 bits για αλληλεπίδραση µε το host επεξεργαστή. Οι δύο αυτές σειριακές θύρες λειτουργούν ανεξάρτητα

9

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

και είναι δυνατόν να λειτουργήσουν σε διαφορετικούς ρυθµούς δειγµατοληψίας. Όπως αναφέρθηκε, ο µέγιστος ρυθµός δειγµατοληψίας για κάθε ένα από τα κανάλια του codec φτάνει τα 11.025kHz. Το υβριδικό κύκλωµα για το κανάλι δεδοµένων περιλαµβάνει ολοκληρωµένους ενισχυτές των οποίων τα κέρδη ενίσχυσης κι οι πόλοι του φίλτρου καθορίζονται από εξωτερικές αντιστάσεις και πυκνωτές. Αυτό επιτρέπει µέγιστη ευελιξία στις ρυθµίσεις ώστε να εναρµονίζονται µε πολλά διεθνή πρότυπα λειτουργίας για τη κάρτα. Το φίλτρο ενίσχυσης που εφαρµόζεται στο κανάλι δεδοµένων ακολουθείται από ένα ενισχυτή κέρδους ο οποίος είναι προγραµµατιζόµενος και ο οποίος τροφοδοτεί τους drivers των ηχείων. Ο ελεγχόµενος driver του ηχείου µπορεί να προγραµµατιστεί για 0dB ενίσχυση ή να µη χρησιµοποιηθεί καθόλου µέσω του καταχωρητή ελέγχου. Η πηγή εισόδου για το ρυθµιζόµενο ηχείο µπορεί να είναι είτε η ενισχυµένη DAC (Data_Out PGA) έξοδος είτε το σήµα εισόδου στον ADC µέσω ενός δεύτερου καταχωρητή ελέγχου. Το αναλογικό κύκλωµα στο κανάλι φωνής περιλαµβάνει ένα bias µικροφώνου, το πολύ 5mA στα 2.5/1.5V , και προενισχυτές για το µικρόφωνο που µπορούν να επιλεχθούν για ενίσχυση στα 0dB ή 20dB. Η συσκευή διαθέτει επιπλέον µια ειδική διεπαφή µε ενισχυτές αποστολής και λήψης. Αυτές οι τρεις είσοδοι µπορούν να συνδυαστούν µε κάθε τρόπο και το αποτέλεσµα στέλνεται σε ένα Line_In προγραµµατιζόµενο ενισχυτή (Programmable Gain Amplifier-PGA) µε κέρδος ενίσχυσης από 12dB έως 36dB µε βήµα 1.5dB. Αυτός τροφοδοτεί το κανάλι φωνής ADC. Στο κανάλι DAC, η έξοδος του DAC στέλνεται σε ένα Line_Out PGA πάλι µε κέρδος ενίσχυσης από 12dB έως 36dB µε βήµα 1.5dB. Αυτός τροφοδοτεί τόσο το 600Ω TAPI driver εξόδου όσο και το driver των 60Ω µονοφωνικού ηχείου το οποίο µπορεί είτε να απενεργοποιηθεί τελείως είτε να προγραµµατιστεί για ενίσχυση 0dB. Η λήξη χρόνου για την αλλαγή στη τιµή του κέρδους ενίσχυσης ή ο µέγιστος χρόνος που το σύστηµα µπορεί να περιµένει για την εµφάνιση του φαινοµένου zero crossing στο σήµα, προτού επιδράσει η αλλαγή στο κέρδος ενίσχυσης, είναι ακριβώς 9ms. Στη συνέχεια θα αναφερθούµε στις λογικές λειτουργίες και το κύκλωµα που απαιτείται για να υλοποιηθούν δυο ανεξάρτητες σειριακές θύρες και να προγραµµατιστεί ο καταχωρητής ελέγχου µέσω δευτερεύουσας επικοινωνίας σ’ αυτές τις θύρες. Υπάρχουν πέντε καταχωρητές ελέγχου οι οποίοι προγραµµατίζονται κατά τη διάρκεια των δευτερευόντων επικοινωνιών είτε από τη σειριακή θύρα που αντιστοιχεί στο κανάλι δεδοµένων είτε από τη θύρα που αντιστοιχεί στο κανάλι φωνής. Αυτοί οι καταχωρητές θέτουν τα κέρδη ενίσχυσης, επιλέγουν πολυπλεγµένες εισόδους και συναρτήσεις ανάδρασης ενώ επίσης διαβάζουν και τα flags υπερχείλισης του ADC. Η συσκευή περιλαµβάνει επιπλέον ένα κύκλωµα power-on reset (POR) για να ελέγχει την 5/3.3V MVDD τροφοδοσία στο σύστηµα και να παρέχει ένα σήµα reset όταν η τροφοδοσία MVDD πέφτει κάτω από ένα προκαθορισµένο κατώφλι. Επιπροσθέτως, διαθέτει ένα κύκλωµα flash write enable

10

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

(FWE) που λαµβάνοντας µια εξωτερική είσοδο παρέχει 40mA ρεύµατος για να ενεργοποιήσει το write enable κύκλωµα µιας συσκευής εξωτερικής µνήµης. Το FWE κύκλωµα ενεργοποιείται από τη ψηφιακή παροχή τροφοδοσίας. 1.3.1.2 Περιγραφή λειτουργιών του codec Όπως ήδη έχει αναφερθεί το TLC320AD535 είναι ικανό να υποστηρίξει, είτε στο κανάλι δεδοµένων είτε στο κανάλι φωνής, οποιοδήποτε ρυθµό δειγµατοληψίας µε µέγιστη τιµή αυτή των 11.025kΗz. Ο ρυθµός δειγµατοληψίας καθορίζεται από τη συχνότητα του πρωτεύοντος ρολογιού του codec το οποίο είναι είσοδος στη σειριακή θύρα γι΄ αυτό το κανάλι. Η συχνότητα δειγµατοληψίας προκύπτει από το εσωτερικό κύκλωµα διαιρέτη του πρωτεύοντος ρολογιού του codec µέσω της ακόλουθης σχέσης :

512xMCKLfrequencysamplingf s ==

όπου xMCKL αναφέρεται είτε στο ρολόι του codec για το κανάλι δεδοµένων είτε για το κανάλι φωνής (δηλ. VC_MCKL είτε DT_MCKL) και το οποίο τροφοδοτείται εξωτερικά µε το ρυθµό ρολογιού του κυκλώµατος του διαιρέτη. Το κύκλωµα αυτό διαιρεί το πρωτεύον ρολόι ώστε να παράγει τη συχνότητα ρολογιού που είναι απαραίτητη για να τροφοδοτήσει τους codecs. Το αντίστροφο της συχνότητας δειγµατοληψίας αποτελεί τη περίοδο δειγµατοληψίας. Ο ρυθµός των δειγµάτων τόσο στο κανάλι φωνής όσο και στο κανάλι δεδοµένων ορίζεται ανεξάρτητα από το ρυθµό του αντίστοιχου πρωτεύοντος ρολογιού του codec. Τα δυο κανάλια του codec µπορούν να δειγµατοληπτηθούν µε διαφορετικούς ρυθµούς ταυτόχρονα. 1.3.1.3 ADC κανάλι σήµατος Τα σήµατα εισόδου ενισχύονται και φιλτράρονται σε buffers που βρίσκονται στο chip, προτού παραληφθεί από την αντίστοιχη είσοδο του ADC. Στη περίπτωση του καναλιού φωνής, οι είσοδοι που προέρχονται από το µικρόφωνο και από το handset µπορεί να προστεθούν µαζί προτού ενισχυθούν /υποβαθµιστούν από τον PGA του ΑDC. Ο ADC µετατρέπει το σήµα σε ψηφιακές λέξεις εξόδου σε µορφή συµπληρώµατος ως προς 2 και οι οποίες αντιστοιχούν στη τιµή του αναλογικού σήµατος τη στιγµή της δειγµατοληψίας. Αυτές οι ψηφιακές λέξεις των 16 bits στέλνονται στο host, µέσω της αλληλεπίδρασης της σειριακής θύρας για το αντίστοιχο κανάλι. Εάν ο ADC φτάσει στη µέγιστη τιµή του, τίθεται µια σηµαία (flag) ενός καταχωρητή ελέγχου. Αυτό το bit ένδειξης υπερχείλισης τοποθετείται στη θέση D0 του καταχωρητή ελέγχου 2 του καναλιού δεδοµένων ή του καταχωρητή ελέγχου 5 του καναλιού φωνής. Αυτά τα bits µπορούν να διαβαστούν µόνο από τις αντίστοιχες σειριακές θύρες και η σηµαία υπερχείλισης καθαρίζεται

11

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

µόνο αφού διαβαστεί µέσω της σειριακής θύρας του καναλιού φωνής ή αντίστοιχα απ’ αυτή του καναλιού δεδοµένων. Οι ADC και DAC µετατροπές είναι σύγχρονες και phase-locked. 1.3.1.4 DAC κανάλι σήµατος O DAC δέχεται τις 16-bit λέξεις δεδοµένων από το host µέσω της διεπαφής της σειριακής θύρας για κάθε κανάλι. Τα δεδοµένα µετατρέπονται σε αναλογικές τάσεις µέσω µιας συνάρτησης ανακατασκευής που διαθέτει ο DAC και που αποτελείται από ένα ψηφιακό φίλτρο παρεµβολής και ένα ψηφιακό διαµορφωτή. Η έξοδος του κάθε DAC περνάει στη συνέχεια από εσωτερικά χαµηλοπερατά φίλτρα για να ολοκληρωθεί η ανακατασκευή του σήµατος δίνοντας το τελικό αναλογικό σήµα. Αυτά τα αναλογικά σήµατα στη συνέχεια αποθηκεύονται σε ένα buffer και ενισχύονται από έναν οδηγό εξόδου κατάλληλο για να οδηγήσει τα δεδοµένα. 1.3.1.5 Οι διαµορφώσεις sigma-delta του ΑDC και του DAC Κάθε ADC και DAC αποτελεί ουσιαστικά ένα διαµορφωτή sigma – delta που υπερδειγµατοληπτεί το σήµα εισόδου, [4]. Ο ADC εξασφαλίζει υψηλή ανάλυση και χαµηλά ποσοστά θορύβου εκµεταλλευόµενος τα πλεονεκτήµατα των τεχνικών υπερδειγµατοληψίας και µορφοποίησης του θορύβου που παρουσιάζουν οι διαµορφωτές sigma - delta. Από την άλλη, ο DAC προσφέρει κι αυτός υψηλή ανάλυση, όπως, επίσης, και χαµηλά επίπεδα θορύβου κατά την D2A µετατροπή χρησιµοποιώντας και αυτός διαµόρφωση sigma – delta. 1.3.1.6 Φίλτρα αποδεκατισµού και φίλτρα παρεµβολής Κάθε φίλτρο αποδεκατισµού µειώνει το ρυθµό των ψηφιακών δεδοµένων στο ρυθµό της δειγµατοληψίας, [4]. Αυτό επιτυγχάνεται µε τον υποβιβασµό της πληροφορίας κατά ένα παράγοντα ίσο µε τον παράγοντα υπερδειγµατοληψίας. Η έξοδος αυτού του φίλτρου είναι µια λέξη των 16 bits (σε συµπλήρωµα ως προς 2), η οποία ακολουθεί τον επιλεγµένο ρυθµό δειγµάτων. Αντίθετα, το φίλτρο παρεµβολής «επαναδειγµατοληπτεί» τη ψηφιακή πληροφορία µε ρυθµό N φορές µεγαλύτερο από το ρυθµό των δειγµάτων εισόδου, όπου το Ν είναι ο παράγοντας υπερδειγµατοληψίας. Η έξοδος των δεδοµένων από αυτό το φίλτρο, που γίνεται µε υψηλή ταχύτητα, εφαρµόζεται στη συνέχεια στο sigma – delta διαµορφωτή. 1.3.1.7 ∆ιακοπή τροφοδοσίας µέσω λογισµικού (Power Down) Η διακοπή τροφοδοσίας που επιτελείται µέσω λογισµικού κάνει reset όλους τους εσωτερικούς µετρητές, αλλά αφήνει τα περιεχόµενα των καταχωρητών ελέγχου αµετάβλητα για το κάθε κανάλι. Η συσκευή έχει ξεχωριστά και ανεξάρτητα software power down bits για τα κανάλια

12

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

φωνής και δεδοµένων. Χρησιµοποιείται ο συγκεκριµένος τρόπος διακοπής τροφοδοσίας µιας και στον TLC320AD535 δε παρέχεται λειτουργία hardware power down.

1.3.1.8 Σειριακές επικοινωνίες Τα σειριακά σήµατα επικοινωνίας για τη σειριακή θύρα του καναλιού δεδοµένων είναι τα DT_DOUT, DT_DIN, DT_SCLK και DT_FS ενώ τα αντίστοιχα σήµατα για τη σειριακή θύρα του καναλιού φωνής είναι τα VC_DOUT, VC_DIN, VC_SCLK, και VC_FS. Τα ψηφιακά δεδοµένα εξόδου από τον ADC λαµβάνονται από το DT_DOUT (ή το VC_DOUT). Τα ψηφιακά δεδοµένα εισόδου για τον DAC δίνονται µέσω του DT_DIN (ή το VC_DIN). Τα DT_SCLK και VC_SCLK χρησιµοποιούνται για το συγχρονισµό των καναλιών δεδοµένων και φωνής αντίστοιχα. Τέλος τα DT_FS και VC_FS χρησιµοποιούνται στα κανάλια δεδοµένων και φωνής αντίστοιχα, για το καθορισµό της χρονικής στιγµής που θα ξεκινήσει η µεταφορά δεδοµένων στον ΑDC και στον DAC. Η µετάδοση σηµάτων δεδοµένων από τον ADC ή προς τον DAC γίνεται µε χρήση πρωτεύουσας σειριακής επικοινωνίας. Αντίθετα, µέσω µιας δευτερεύουσας σειριακής επικοινωνίας γράφονται ή διαβάζονται λέξεις στους καταχωρητές ελέγχου, οι οποίοι ελέγχουν τόσο τις επιλογές όσο και τις ρυθµίσεις του κυκλώµατος της συσκευής. Ο σκοπός της πρωτεύουσας και δευτερεύουσας επικοινωνίας είναι να επιτρέπει τα δεδοµένα που έχουν υποστεί µετατροπή καθώς και τα δεδοµένα ελέγχου να µεταφερθούν κατά µήκος της ίδιας σειριακής θύρας. Μια πρωτεύουσα µεταφορά αναφέρεται αποκλειστικά και µόνο στα δεδοµένα που έχουν υποστεί µετατροπές. Αντίθετα µια δευτερεύουσα µεταφορά χρησιµοποιείται για να θέσει ή να διαβάσει τις τιµές του αντίστοιχου καταχωρητή ελέγχου. Μια πρωτεύουσα αναφορά συµβαίνει σε κάθε περίοδο που έχουµε µετατροπή δεδοµένων. Αντίστοιχα µια δευτερεύουσα µεταφορά δεδοµένων πραγµατοποιείται µόνο όταν γίνει δεκτή µια αίτηση. Η αίτηση αυτή γίνεται µέσω λογισµικού από το D0 των πρωτευόντων δεδοµένων εισόδου προς το DT_DIN για τη σειριακή θύρα του καναλιού δεδοµένων ή προς το VC_DIN για την αντίστοιχη θύρα του καναλιού φωνής. Μια αίτηση για δευτερεύουσα επικοινωνία µπορεί να πραγµατοποιηθεί για το κανάλι φωνής χωρίς να είναι απαραίτητο να γίνει µια αντίστοιχη για το κανάλι δεδοµένων και αντίστροφα. Οι καταχωρητές ελέγχου 1 και 2 µπορούν να διαβάσουν ή να γράψουν δεδοµένα µόνο στη σειριακή θύρα του καναλιού δεδοµένων ενώ οι καταχωρητές ελέγχου 3 έως 6 µπορούν να διαβάσουν ή να γράψουν δεδοµένα µόνο στη σειριακή θύρα του καναλιού φωνής. Όπως έχει ήδη αναφερθεί η πρωτεύουσα σειριακή επικοινωνία µεταδίδει και λαµβάνει δεδοµένα που έχουν υποστεί µετατροπή. Μετά την παροχή τροφοδοσίας ή το reset, η συσκευή έρχεται σε µια 15-bit DAC mode. Το µήκος της λέξης του DAC είναι 15 bits και το τελευταίο bit από τη 16-bit λέξη της πρωτεύουσας σειριακής επικοινωνίας είναι ένα bit ελέγχου που χρησιµοποιείται για την αίτηση µιας δευτερεύουσας σειριακής επικοινωνίας. Για κάθε σειριακή επικοινωνία το πιο σηµαντικό bit (MSB) µεταφέρεται πρώτο. Για τη 16-bit λέξη του ADC, το MSB είναι το D15 και το D0 είναι το LSB. Για τη 15-bit λέξη του DAC στη πρωτεύουσα επικοινωνία το D15 είναι το

13

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

MSB, το D1 είναι το LSB και το D0 χρησιµοποιείται για αίτηση δευτερεύουσας επικοινωνίας. Στο παρακάτω σχήµα που απεικονίζει το format των δεδοµένων της πρωτεύουσας επικοινωνίας για τα DIN και DOUT συνοψίζονται τα προαναφερθέντα .

Σχήµα 1.7 : Format δεδοµένων των DIN και DOUT για τη πρωτεύουσα επικοινωνία Η δευτερεύουσα σειριακή επικοινωνία διαβάζει και γράφει 16-bit λέξεις οι οποίες προγραµµατίζουν τόσο τις επιλογές όσο και τις ρυθµίσεις του κυκλώµατος της συσκευής είτε για το κανάλι φωνής είτε για το κανάλι δεδοµένων. Για τη δευτερεύουσα επικοινωνία χρησιµοποιείται προγραµµατισµός µέσω καταχωρητών για το αντίστοιχο κανάλι. Τέσσερις πρωτεύοντες και δευτερεύντες κύκλοι επικοινωνίας απαιτούνται για να προγραµµατιστούν οι τέσσερις καταχωρητές του καναλιού φωνής. Κατ’ αναλογία, δύο πρωτεύοντες και δευτερεύοντες κύκλοι επικοινωνίας είναι απαραίτητοι για να προγραµµατιστούν οι καταχωρητές του καναλιού δεδοµένων. Αν η default τιµή για ένα συγκεκριµένο καταχωρητή είναι η επιθυµητή, τότε η διυεθυνσιοδότηση του καταχωρητή µπορεί να επιτευχθεί κατά τη διάρκεια της δευτερεύουσας επικοινωνίας. Η εντολή NOOP (no operation) διευθυνσιοδοτεί ένα ψευδοκαταχωρητή, τον καταχωρητή 0 και δεν γίνεται κανένας προγραµµατισµός κάποιου άλλου καταχωρητή κατά τη διάρκεια της δευτερεύουσας επικοινωνίας. Αυτό µπορεί να χρησιµοποιηθεί είτε για τη σειριακή θύρα του καναλιού δεδοµένων είτε για την αντίστοιχη του καναλιού φωνής. Κατά τη διάρκεια της δευτερεύουσας επικοινωνίας γράφεται ή διαβάζεται ένας καταχωρητής. Για να εγγραφεί µία τιµή σε έναν καταχωρητή, πρέπει να ληφθεί από το DT__IN (ή το VC_DIN) . Τα δεδοµένα που επιστρέφονται στο DT_DOUT (ή στο VC_DOUT) είναι το 00h.

14

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

Σχήµα 1.8 : Format δεδοµένων των DIN και DOUT για τη δευτερεύουσα επικοινωνία

1.4 Σύνοψη Σε αυτό το κεφάλαιο παρουσιάστηκε η βασική δοµή και οι σηµαντικότερες λειτουργίες της αναπτυξιακής πλατφόρµας TMS320C6711 DSK. Ιδιαίτερη αναφορά έγινε στο Analog Interface Circuit µε το οποίο γίνεται η µετατροπή της αναλογικής πληροφορίας εισόδου στη κάρτα σε ψηφιακή καθώς επίσης και η αντίστροφη διαδικασία . Το τµήµα αυτό του DSK θα παίξει ουσιαστικό ρόλο κατά την δειγµατοληψία του αναλογικού σήµατος της γεννήτριας παλµών και την µετατροπή του σε ψηφιακό σήµα προς επεξεργασία από τον DSP καθώς και στην αντίστροφη διαδικασία κατά την έξοδο του σήµατος από την κάρτα. και την δυνατότητα παρατήρησής της τελικής µορφής του στον παλµογράφο. Στο κεφάλαιο που ακολουθεί θα αναπτυχθεί διεξοδικά ο ψηφιακός επεξεργαστής σήµατος TMS320C6711, ο οποίος αποτελεί την καρδιά της αναπτυξιακής πλατφόρµας.

15

Κεφάλαιο 1 – Η πλατφόρµα TMS320C6711 DSK

16

ΚΚΕΕΦΦΑΑΛΛΑΑΙΙΟΟ 22 Ο επεξεργαστής TMS320C6711 2.1 Εισαγωγή

Στην ενότητα αυτή θα αναφερθούν κάποια γενικά χαρακτηριστικά των επεξεργαστών της οικογένειας TMS320C6000 καθώς και οι µεγάλες δυνατότητες που προσφέρει ο επεξεργαστής TMS320C6711 και η ευρεία χρήση του σε µοντέρνες εφαρµογές επεξεργασίας σήµατος. Στη συνέχεια, η περιγραφή εστιάζεται στην αρχιτεκτονική του επεξεργαστή TMS320C6711. Ειδικότερα, θα γίνει αναφορά στα :

• Enhanced Direct Memory Access ελεγκτή (EDMA controller), • ∆ιεπαφή Θύρας-Ξενιστή (Host Port Interface-HPI) • ∆ιεπαφή Εξωτερικής Μνήµης (External Memory Interface-EMIF) • Boot Configuration • Πολυκαναλικές Αποµονωµένες Σειριακές Θύρες (Multichannel Buffered Serial Ports-

McBSP) • Χρονιστές (timers), • Επιλογέα διακοπών (Interrupt Selector και External Interrupts), • Εσωτερική µνήµη, καθώς και τον τρόπο διασύνδεσής τους. • ∆ίαυλο επέκτασης (Expansion Bus), • PCI, • Εσωτερική µνήµη, καθώς και τον τρόπο διασύνδεσής τους.

2.2 Η οικογένεια TMS320C6000

Η TMS320C6000 πλατφόρµα συσκευών αποτελείται από ψηφιακούς επεξεργαστές σήµατος (DSPs) που χρησιµοποιούν τη VelociTITM Very Long Instruction Word (VLIW) αρχιτεκτονική και επιτυγχάνουν υψηλή απόδοση µέσω αυξηµένου παραλληλισµού σε επίπεδο εκτέλεσης εντολών. Η αρχιτεκτονική αυτή σε συνδυασµό µε τα υποστηριζόµενα εργαλεία ανάπτυξης και εκτίµησης παρέχει ταχύτερο χρόνο ανάπτυξης και υψηλότερη απόδοση για multichannel, multifunction και embedded DSP εφαρµογές που είναι µέχρι και δέκα φορές υψηλότερη από αυτήν των

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

superscalar επεξεργαστών. Τµήµα αυτών των αναπτυξιακών εργαλείων είναι ο νέος, αποδοτικός C Compiler, ο assembly optimizer και µια WindowsΤΜ debugger διεπαφή που διευκολύνουν τον προγραµµατισµό.

Η υψηλή τους απόδοση, µέχρι και 4800 ΜΙPS, σε συνδυασµό µε τη χαµηλή τιµή τούς καθιστά ιδανική λύση σε µια πληθώρα εφαρµογών, όπως :

• Pooled modems • Wireless local loop base stations • Beamforming base stations • Remote Access Servers (RAS) • Digital Subscriber Loop (DSL) systems • Cable modems • Multichannel telephony systems • Virtual reality 3D graphics • Speech recognition • Audio • Radar • Atmospheric modeling • Finite element analysis • Imaging (π.χ.: fingerprint recognition, ultrasound και MRI) • Personalized home security µε face και hand/fingerprint recognition • Advanced cruise control µε global positioning systems (GPS) πλοήγηση

και αποφυγή ατυχηµάτων • Remote medical diagnostics κ.ά.

Οι ’C6000 συσκευές εκτελούν µέχρι και οκτώ εντολές των 32 bits σε κάθε κύκλο ρολογιού. Ο πυρήνας της CPU αποτελείται από :

• 32 καταχωρητές γενικού σκοπού µε µήκος λέξης 32 bits • 8 λειτουργικές µονάδες :

o 2 πολλαπλασιαστές o 6 Αριθµητικές Λογικές Μονάδες (ALUs)

Οι ‘C62x/C67x συσκευές διαθέτουν επιπλέον µία hardware emulation board, συµβατή µε τη διεπαφή : TI XDS510E emulator. Αυτό το εργαλείο ακολουθεί το IEEE Standard 1149.1–1990, IEEE Standard Test Access Port and Boundary-Scan Architecture. Μερικά από τα χαρακτηριστικά αυτών των συσκευών είναι τα ακόλουθα :

18

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

aΗ εξελιγµένη VLIW CPU µε τις οκτώ παραπάνω λειτουργικές µονάδες :

• εκτελεί µέχρι και οκτώ εντολές σε κάθε κύκλο, παρέχοντας µέχρι και δέκα φορές καλύτερη απόδοση από τους τυπικούς DSPs,

• επιτρέπει στους σχεδιαστές να αναπτύξουν υψηλά αποδοτικό RISC-like κώδικα σε σύντοµο χρόνο.

aΗ Οµαδοποίηση Εντολών (Instruction packing) :

• παρέχει µέγεθος κώδικα που ισοδυναµεί µε οκτώ εντολές που εκτελούνται σειριακά ή παράλληλα,

• µειώνει το µέγεθος του κώδικα, τα program fetches και την κατανάλωση. aΌλες οι εντολές εκτελούνται υπό όρους :

• µειώνεται το branching, • αυξάνεται ο παραλληλισµός, οδηγώντας σε υψηλότερη απόδοση.

aΟ εισαγόµενος από το χρήστη κώδικας εκτελείται σε ανεξάρτητες λειτουργικές µονάδες. Για το σκοπό αυτό διαθέτει έναν :

• αποδοτικό C compiler κι έναν • assembly optimizer για γρήγορη ανάπτυξη και βελτιωµένο παραλληλισµό.

aΥποστηρίζει δεδοµένα 8/16/32-bit, παρέχοντας ευελιξία για µια πληθώρα εφαρµογών :

• 40-bit αριθµητικές επιλογές, οι οποίες δίνουν επιπλέον ακρίβεια στο σχεδιασµό vocoders και άλλων υπολογιστικά δύσκολων εφαρµογών,

• υποστηρίζεται κορεσµός (saturation) και κανονικοποίηση (normalization), οι οποίες παρέχουν υποστήριξη σε αριθµητικές πράξεις,

• ο χειρισµός των πεδίων και των εντολών µαζί µε το bit counting υποστηρίζουν τις απαραίτητες πράξεις σε εφαρµογές ελέγχου και χειρισµού δεδοµένων.

Για τη µνήµη και τα περιφερειακά παρέχονται οι εξής επιλογές:

• µεγάλη on-chip RAM για γρήγορη εκτέλεση των αλγορίθµων,

19

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

• 32-bit interface εξωτερικής µνήµης, το οποίο υποστηρίζει SDRAM, SBSRAM, SRAM κι άλλες ασύγχρονες µνήµες,

• πρόσβαση του host στη µνήµη και στα περιφερειακά των συσκευών’C62x/C67x µέσω της παράλληλης θύρας,

• multichannel DMA controller, ο C6711 περίεχει enhanced DMA (EDMA) controller, • multichannel serial port(s), • 32-bit timer(s).

Ειδικότερα, οι συσκευές ’C67x έχουν τα ακόλουθα χαρακτηριστικά :

• το πολύ 1336 MIPS στα 167 MHz, o C6711: 900 MIPS µε 6.7 nsec cycle time στα 150 MHz.

• το πολύ 1G FLOPS στα 167 MHz για single-precision πράξεις, • το πολύ 250M FLOPS στα 167 MHz για double-precision πράξεις, • το πολύ 688M FLOPS στα 167 MHz για πράξεις πολλαπλασιασµού και συσσώρευσης, • υποστήριξη υλικού για single-precision (32-bit) και double-precision (64-bit) IEEE

πράξεις κινητής υποδιαστολής, • 32x32-bit πολλαπλασιασµό ακεραίων µε 32- ή 64-bit αποτέλεσµα.

2.3 Γενική περιγραφή του επεξεργαστή TMS320C6711 Η ταχύτητα του επεξεργαστή TMS320C6711 αγγίζει τις 900 εκατοµµύρια εντολές κινητής υποδιαστολής το δευτερόλεπτο (MFLOPS) µε ρυθµό ρολογιού στα 150ΜHz. Ο συγκεκριµένος επεξεργαστής διαθέτει τη λειτουργική ικανότητα των ελεγκτών υψηλής ταχύτητας όσο και την αριθµητική ικανότητα των επεξεργαστών πινάκων. Αυτός ο επεξεργαστής έχει 32 καταχωρητές γενικού σκοπού των 32-bit µήκους λέξεων και 8 ανεξάρτητες λειτουργικές µονάδες που παρέχουν 4 κινητής/σταθερής υποδιαστολής ALUs, 2 σταθερής υποδιαστολής ALUs και 2 κινητής/σταθερής υποδιαστολής πολλαπλασιαστές. Χρησιµοποιεί µια διεπίπεδη αρχιτεκτονική κρυφής µνήµης και έχει ένα ισχυρό και ποικίλο σύνολο από διαφορετικά περιφερειακά που βρίσκονται on-chip. Η επιπέδου 1 program cache (LP1) είναι µία 32-Kbit direct memory cache και η επιπέδου 1 data cache (LD1) είναι µία 32-bit 2-way set-associative µνήµη. Η επιπέδου 2 κρυφή µνήµη (L2) αποτελείται από ένα χώρο µνήµης 512-Kbit ο οποίος µοιράζεται σε χώρο για πρόγραµµα και χώρο για δεδοµένα. Η L2 µνήµη µπορεί να ρυθµιστεί ως κλασική µνήµη, ως cache ή ως συνδυασµός των δύο. Το σύνολο των περιφερειακών περιλαµβάνει δύο Multichannel Buffered Serial Ports (McBSP), δύο γενικού

20

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

σκοπού timers, ένα Host Port Interface (HPI), ένα External Memory Interface (EMIF) ικανό να αλληλεπιδράσει µε SDRAM, SBSRAM και ασύγχρονα περιφερειακά. Τα περιφερειακά που είναι προσβάσιµα από το χρήστη ρυθµίζονται µέσω ενός συνόλου καταχωρητών ελέγχου που είναι memory-mapped. Ο ελεγκτής του διαύλου των περιφερειακών αναλαµβάνει να εκτελέσει τις προσβάσεις στα περιφερειακά που βρίσκονται πάνω στο chip. Παρακάτω παρουσιάζεται το chip του επεξεργαστή TMS320C6711 στο οποίο φαίνεται η διαρρύθµιση των pins.

Σχήµα 2.1 : Η κάτοψη του ολοκληρωµένου TMS320C6711

Στη συνέχεια δίνεται το σχηµατικό διάγραµµα του επεξεργαστή, όπου µπορούµε να παρατηρήσουµε τη ΚΜΕ και τη διασύνδεση της µε τις υπόλοιπες µονάδες του ολοκληρωµένου και µε τα εξωτερικά περιφερειακά.

21

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Σχήµα 2.2 : Σχηµατικό ∆ιάγραµµα του επεξεργαστή TMS320C6711

Στη συνέχεια παρατίθεται µια συνοπτική περιγραφή των βασικών στοιχείων που διαθέτει το ολοκληρωµένο (Σχήµα 2.2). Ελεγκτής EDMA Ο ελεγκτής EDMA (Enhanced Direct Memory Access) µεταφέρει δεδοµένα µεταξύ διευθύνσεων της µνήµης, χωρίς τη συµµετοχή της CPU. ∆ιαθέτει 16 προγραµµατιζόµενα κανάλια όπως επίσης χώρο RAM όπου κρατάει πολλαπλές ρυθµίσεις για µελλοντικές µεταφορές. ∆ιεπαφή Θύρας-Ξενιστή (Host Port Interface-HPI) Το HPI είναι διεπαφή παράλληλης θύρας, µέσω της οποίας ο host επεξεργαστής µπορεί να έχει απ΄ ευθείας πρόσβαση στο χώρο της µνήµης της ΚΜΕ. H host συσκευή έχει ευκολία πρόσβασης, γιατί είναι ο master στη διεπαφή που αναπτύσσεται µε τη κάρτα. Ο host και η ΚΜΕ µπορεί να

22

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

ανταλλάξουν πληροφορία µέσω εσωτερικής ή εξωτερικής µνήµης. Επιπλέον, ο host έχει απ΄ ευθείας πρόσβαση σε όλα τα memory mapped περιφερειακά. ∆ιεπαφή Εξωτερικής Μνήµης (External Memory Interface-EMIF) Όπως ήδη έχει αναφερθεί, το EMIF υποστηρίζει αλληλεπίδραση µε διάφορες εξωτερικές συσκευές όπως:

• σύγχρονες burst SRAM (SBSRAM), • σύγχρονες DRAM (SDRAM), • ασύγχρονες συσκευές όπως SRAM, ROM και FIFOs, • εξωτερικές συσκευές διαµοιραζόµενης µνήµης.

Boot Configuration Οι συσκευές της οικογένειας TMS320C6000 προσφέρουν µία ποικιλία από boot configurations που καθορίζουν ποιες ενέργειες θα πρέπει να κάνει ο DSP ύστερα από το reset της συσκευής, για τις απαραίτητες αρχικοποιήσεις. Αυτές οι ενέργειες περιλαµβάνουν το φόρτωµα κώδικα από µία εξωτερική ROM µέσω EMIF και το φόρτωµα κώδικα µέσω του HPI από ένα εξωτερικό host. Πολυκαναλικές Αποµονωµένες Σειριακές Θύρες ( Multichannel Buffered Serial Ports- McBSP) Χρησιµοποιούνται για να κάνουν buffering σειριακά δεδοµένα στη µνήµη αυτόµατα και µε τη βοήθεια του EDMA ελεγκτή. Επιπλέον, έχουν δυνατότητες για πολυκαναλικές µεταφορές ικανές να συγκριθούν µε τα T1, E1, SCSA και MVIP δικτυακά standards, [3]. Ακόµη προσφέρονται για full-duplex επικοινωνία, διαθέτουν double-buffered καταχωρητές δεδοµένων, ανεξάρτητο framing και χρονισµό για εκποµπή και λήψη καθώς και απ΄ ευθείας διεπαφή µε codecs που χρησιµοποιεί κατά κόρον η σύγχρονη βιοµηχανία, µε AICs και άλλες σειριακές A/D και D/A συσκευές. Χρονιστές (Timers) O επεξεργαστής TMS320C6711 διαθέτει 32-bit γενικού σκοπού timers που χρησιµοποιούνται για να εκτελέσουν τις παρακάτω λειτουργίες

• time events • count events • γεννήτριες παλµών

23

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

• διακοπή της CPU • αποστολή σηµάτων συγχρονισµού στον EDMA ελεγκτή

Επιλογέας ∆ιακοπών (Interrupt Selector) Το σύνολο των περιφερειακών αποτελεί µία πηγή παροχής interrupts. Ο interrupt selector επιτρέπει στο χρήστη να επιλέξει ποια interrupts χρειάζεται το σύστηµά του. Επίσης επιτρέπει την αλλαγή της πολικότητας των εξωτερικών interrupt σηµάτων. Κατάστασης Μειωµένης Ισχύος (Power-down) Η power-down λογική επιτρέπει ο µειωµένος χρονισµός να µειώσει την κατανάλωση ισχύος. Το µεγαλύτερο µέρος της ισχύς της CMOS λογικής καταναλώνεται κατά τη µεταγωγή κυκλώµατος από τη µια λογική κατάσταση στην άλλη. Αν αποφευχθεί µέρος ή όλη η διαδικασία µεταγωγής απο τη µια λογική κατάσταση στην άλλη, τότε πραγµατοποιείται πολύ σηµαντική εξοικονόµηση ενεργείας χωρίς να χαθούν δεδοµένα ή λειτουργικά περιεχόµενα. Εσωτερική Μνήµη Οι TMS320C6211/C6711 συσκευές διαθέτουν µια αρχιτεκτονική µνήµης δύο επιπέδων τόσο για την εσωτερική µνήµη όσο και για τους διαύλους δεδοµένων. Το πρώτο επίπεδο µνήµης για το εσωτερικό πρόγραµµα και το δίαυλο δεδοµένων είναι µια 4KΒ cache, L1P για την cache προγράµµατος και L1D για την cache δεδοµένων. Το δεύτερο επίπεδο µνήµης είναι ένα 64KΒ block µνήµης το οποίο µοιράζεται τόσο στο πρόγραµµα όσο και στους διαύλους δεδοµένων µνήµης˙ το L2 επίπεδο.

2.4 Ανάλυση της κεντρικής µονάδας επεξεργασίας (DSP core) Η κεντρική µονάδα επεξεργασίας, όπως έχει ήδη αναφερθεί, είναι σχεδιασµένη µε βάση την αρχιτεκτονική Very Long Instruction Word (VLIW) και είναι ικανή να προµηθεύσει το πολύ µέχρι και 8 32-bit εντολές τις 8 λειτουργικές µονάδες µέσα σε έναν κύκλο ρολογιού. Αν κάποιες από τις 8 λειτουργικές µονάδες δεν είναι έτοιµες να εκτελέσουν κάποια εντολή, η VLIW αρχιτεκτονική ελέγχει και εντοπίζει ποιες είναι αυτές και δεν τις τροφοδοτεί µε εντολές. Το πρώτο bit κάθε 32-bit εντολής καθορίζει εάν η επόµενη εντολή ανήκει στο ίδιο πακέτο εκτέλεσης µε την προηγούµενη εντολή ή εάν θα πρέπει να εκτελεστεί στον επόµενο κύκλο ρολογιού ως µέρος του επόµενου πακέτου εκτέλεσης. Παρότι τα ανακληθέντα πακέτα είναι πάντοτε εύρους 256 (8x32) bits, τα πακέτα εκτέλεσης µπορούν να ποικίλουν σε µέγεθος. Τα µεταβλητού

24

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

µεγέθους πακέτα εκτέλεσης είναι ένας ιδιαίτερος τρόπος εξοικονόµησης µνήµης, που κάνει τη CPU του TMS320C6711 να ξεχωρίζει από τις άλλες VLIW αρχιτεκτονικές. Η CPU διαθέτει δύο σύνολα λειτουργικών µονάδων. Καθ’ ένα από τα σύνολα αυτά αποτελείται από τέσσερις µονάδες και ένα αρχείο καταχωρητών. Το ένα σύνολο περιέχει τις λειτουργικές µονάδες .L1, .S1, .M1 και .D1 ενώ το άλλο περιέχει αντίστοιχα τις .L2, .S2, .M2 και .D2. Το κάθε ένα από τα δύο αρχεία καταχωρητών περιέχει 16 32-bit καταχωρητές, σχηµατίζοντας ένα σύνολο 32 καταχωρητών γενικού σκοπού. Τα δύο σύνολα λειτουργικών µονάδων µαζί µε τα αρχεία καταχωρητών συνθέτουν τα τµήµατα Α και Β της CPU (βλέπε Σχήµα 2.2). Οι τέσσερις λειτουργικές µονάδες στο κάθε τµήµα της CPU µπορούν ελεύθερα να µοιραστούν τους 16 καταχωρητές που ανήκουν στο τµήµα αυτό. Επιπλέον, κάθε τµήµα διαθέτει ένα δίαυλο δεδοµένων που συνδέεται µε όλους τους καταχωρητές του άλλου τµήµατος, µέσω του οποίου τα δύο σύνολα λειτουργικών µονάδων µπορούν να έχουν πρόσβαση στα δεδοµένα του αρχείου καταχωρητή του άλλου τµήµατος. Η πρόσβαση στο αρχείο καταχωρητή γίνεται στη διάρκεια ενός ωρολογιακού κύκλου για τις λειτουργικές µονάδες που βρίσκονται στο ίδιο τµήµα µε τον καταχωρητή, ενώ για αυτές που βρίσκονται στο άλλο τµήµα απαιτείται ένας κύκλος ρολογιού για διάβασµα και γράψιµο. Η CPU του ’C6711 εκτελεί όλες τις εντολές σταθερής υποδιαστολής που υποστηρίζουν όλοι οι επεξεργαστές της σειράς C62x και επιπλέον οι έξι από τις οχτώ λειτουργικές του µονάδες (.L1, .S1, .M1, .M2, .S2, και .L2) υποστηρίζουν εντολές κινητής υποδιαστολής. Οι υπόλοιπες δύο µονάδες (.D1 και .D2) έχουν επιπλέον τη δυνατότητα να εκτελούν LDDW εντολές, όπου σε κάθε τµήµα της CPU (Α και Β) φορτώνονται 64 bits για ένα σύνολο από 128 bits. Ένα ακόµη βασικό χαρακτηριστικό της επεξεργαστικής µονάδας είναι και η αρχιτεκτονική load/store. Οι δύο data – addressing µονάδες (.D1 και .D2) είναι υπεύθυνες για όλες τις µεταφορές δεδοµένων µεταξύ των αρχείων καταχωρητών και της µνήµης. Η διεύθυνση δεδοµένων που οδηγείται από τις .D µονάδες, επιτρέπει τη διευθυνσιοδότηση δεδοµένων που προκύπτουν από το ένα αρχείο καταχωρητών, να χρησιµοποιηθούν ώστε να λαµβάνονται/αποθηκεύονται δεδοµένα από/προς το άλλο αρχείο καταχωρητών. Η ΚΜΕ υποστηρίζει ένα πλήθος από τρόπους έµµεσης διευθυνσιοδότησης χρησιµοποιώντας είτε γραµµικό είτε κυκλικό τρόπο διευθυνσιοδότησης µε 5 ή 15-bits offsets [9]. Όλες οι εντολές είναι υπό συνθήκη εντολές και οι περισσότερες έχουν πρόσβαση σε οποιοδήποτε από τους 32 καταχωρητές. Παρόλα αυτά ορισµένοι καταχωρητές έχουν σχεδιαστεί για να υποστηρίζουν συγκεκριµένες λειτουργίες διευθυνσιοδότησης ή να κρατούν τη συνθήκη για τις υπό συνθήκη εντολές. Οι δύο .Μ λειτουργικές µονάδες χρησιµοποιούνται για πολλαπλασιασµούς. Οι δύο .S και .L λειτουργικές µονάδες εκτελούν ένα γενικό σύνολο από αριθµητικές, λογικές συναρτήσεις και συναρτήσεις διακλάδωσης των οποίων τα αποτελέσµατα παράγονται εντός ενός κύκλου ρολογιού [9].

25

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Η διαδικασία εκτέλεσης ξεκινά όταν προσκοµιστεί ένα 256-bit πακέτο ανάκλησης από τη program memory. Οι 32-bit εντολές που προορίζονται για µεµονωµένες λειτουργικές µονάδες, προωθούνται µε ένα συνηµµένο “1” στο LSB της εντολής. Οι εντολές που ενώνονται «αλυσιδωτά» για ταυτόχρονη εκτέλεση (µέχρι 8 σύνολο) αποτελούν ένα πακέτο εκτέλεσης. Ένα “0” στο LSB µιας εντολής «σπάει» την αλυσίδα και τοποθετεί τις επόµενες εντολές που ακολουθούν στο επόµενο πακέτο εκτέλεσης. Εάν ένα πακέτο εκτέλεσης ξεπεράσει το όριο του πακέτου ανάκλησης (256-bits) ο assembler τοποθετεί τα πλεονάζοντα δεδοµένα στο επόµενο πακέτο ενώ το υπόλοιπος χώρος στο τρέχον πακέτο εκτέλεσης συµπληρώνεται µε NOP εντολές. Ο αριθµός των πακέτων εκτέλεσης για ένα πακέτο ανάκλησης µπορεί να κυµαίνεται από 1 έως 8. Τα πακέτα εκτέλεσης αποστέλλονται στις αντίστοιχες λειτουργικές µονάδες µε ρυθµό ένα πακέτο ανά κύκλο ρολογιού και το επόµενο 256-bit πακέτο ανάκλησης δε προσκοµίζεται µέχρι όλα τα πακέτα εκτέλεσης του τρέχοντος πακέτου ανάκλησης να αποσταλούν στους προορισµούς τους. Μετά την διερµηνεία, οι εντολές ταυτόχρονα οδηγούνται σε όλες τις λειτουργικές µονάδες που είναι ενεργές, αποδίδοντας µέγιστο ρυθµό εκτέλεσης 8 εντολές ανά κύκλο ρολογιού. Ενώ τα περισσότερα αποτελέσµατα αποθηκεύονται στους 32-bit καταχωρητές, µπορούν διαδοχικά να µεταφερθούν στη µνήµη ως bytes ή half words. Όλες οι load-store εντολές είναι byte-, half-word, ή word-addressable. 2.5 Η µορφή των ακεραίων και κινητής υποδιαστολής λέξεων Ένας ακέραιος στην οικόγενεια των επεξεργαστών C6000 είναι µια λέξη των 32-bits. Υποθέστε

οτι η λέξη έχει τη µορφή . Το πιο αριστερό bit, , είναι το πιο

σηµαντικό bit (MSB) και το αντίστοιχο πιο δεξιό, , είναι το λιγότερο σηµαντικό bit (LSB). Οι

ακέραιοι µπορεί να είναι είτε προσηµασµένοι, είτε µη προσηµασµένοι. Ένας µη προσηµασµένος αριθµός έχει την δεκαδική τιµή

),,,,( 013031 ddddd …=

0d31d

∑=

=31

02

n

nndv

και το εύρος του είναι . Οι προσηµασµένοι αναπαρίστανται µε τη µορφή

συµπληρώµατος ως προς 2 µε το MSB να είναι το bit προσήµου. Έτσι ένας προσηµασµένος ακέραιος έχει τη δεκαδική τιµή

]12,0[ 32 −

∑=

+−=30

0

3131 22

n

nndbv

26

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

του οποίου το εύρος είναι . Είναι προφανές ότι όταν ]12,2[ 3131 −− 031 =b ο ακέραιος είναι

θετικός, ενώ είναι αρνητικός όταν 131 =b . Αυτές οι µορφές θεωρούν ότι η υποδιαστολή

βρίσκεται δεξιά από το λιγότερο σηµαντικό bit.

Από την άλλη θεωρώντας L δεκαδικά ψηφία, η λέξη έχει τη µορφή ),.,,( 0131 bbbbb LL …… −=

και έχει τη δεκαδική τιµή

+−= ∑

=

−30

0

3131 222

n

nn

L dbv

Τότε ο ακέραιος έχει τη µορφή . Όταν εκτελούνται αριθµητικές πράξεις ακεραίων που

βρίσκονται σε αυτή τη µορφή, θα πρέπει ο προγραµµατιστής να λάβει υπόψη του τη σωστή θέση της υποδιαστολής. Οι ακέραιοι καταλαµβάνουν ένα καταχωρητή στο αρχείο καταχωρητών.

LQ

Η οικογένεια των επεξεργαστών C6000 υποστηρίζει επίσης ακεραίους µήκους 40-bit (long integers). Οι long integers αποθηκεύονται σε δύο διαδοχικούς καταχωρητές στο αρχείο καταχωρητών. Τα 32 λιγότερα σηµαντικά bits τοποθετούνται σε έναν καταχωτητή µε ζυγή αρίθµηση, ενώ τα 8 πιο σηµαντικά ψηφία τοποθετούνται στα 8 χαµηλότερα bit του καταχωρητή µε την αµέσως υψηλότερη αρίθµηση, η οποία είναι περιττή. Οι επεξεργαστές κινητής υποδιαστολής (όπως ο C6711) µπορούν επίσης να σχηµατίζουν ακεραίους διπλής ακρίβειας µήκους 64 bits οι οποιοί καταλαµβάνουν ένα ζεύγος διαδοχικών καταχωρητών. Ο DSP C6711 υποστηρίζει αριθµούς κινητής υποδιαστολής ΙΕΕΕ µονής και διπλής ακρίβειας. Οι ΙΕΕΕ αριθµοί κινητής υποδιαστολής µπορεί να είναι κανονικοποιηµένοι, µη κανονικοποιηµένοι, NaNs (not a number) και άπειροι αριθµοί. Οι µη κανονικοποιηµένοι αριθµοί είναι µη µηδενικοί αριθµοί οι οποίοι είναι µικρότεροι κατά απόλυτη τιµή, απο το µικρότερο µη µηδενικό, θετικό, κανονικοποιηµένο αριθµό. Οι αριθµοί µονής ακρίβειας έχουν µήκος 32 bits, ενώ οι διπλοί ακρίβειας έχουν µήκος 64 bits. Οι κανονικοποιηµένοι αριθµοί µονής ακρίβειας είναι ακριβείς σε τουλάχιστον 6 δεκαδικά ψηφία, ενώ οι αντίστοιχοι διπλής ακρίβειας σε τουλάχιστον 15 δεκαδικά ψηφία. Η µορφή ενός αριθµού κινητής υποδιαστολής µονής ακρίβειας είναι 31 30 23 22 0

s 067 ,,, eee … 232221 ,,,, ffff …

27

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Ακολούθως επεξηγούνται τα πεδία αυτής της λέξης • Το πεδίο µήκους ενός bit είναι το bit προσήµου. Εάν s 0=s οι αριθµοί είναι θετικοί,

ενώ εάν είναι αρνητικοί. 1=s• Το πεδίο µήκους 8 bit είναι ο πολωµένος εκθέτης που έχει τη δεκαδική τιµή

, έτσι ώστε

067 ,,, eee …

2kk∑

=

=7

0kee 2550 ≤≤ e . Ο πολωµένος εκθέτης ενος κανονικοποιηµένου

αριθµού δε µπορεί να έχει τις τιµές 0 και 255. Η τιµή 0=e είναι δεσµευµένη για αριθµούς που είναι ίσοι µε το 0. Η τιµή 255=e είναι δεσµευµένη για την αναπαράσταση απείρου και NaN.

• Το πεδίο µήκους 23 bit ονοµάζεται mantissa ή δεκαδικό µέρος και

έχει την ισοδύναµη δεκαδική τιµή , που αντιστοιχεί στη δυαδική λέξη

. Η mantissa έχει εύρος [

232221 ,,,, ffff …

23f

∑=

−=23

12

k

kkff

]21,0 23−−21.0 ff … Η αριθµητική τιµή, x , της λέξης µονής ακρίβειας, κινητής υποδιαστολής καθορίζεται από τους ακόλουθους κανόνες:

1. Εάν e και , τότε το 255= 0≠f x είναι ΝaN, ανεξάρτητο από το s

2. Εάν e και , τότε 255= 0=f ( ) ∞−= sx 1

3. Εάν τότε . Αυτοί είναι οι κανονικοποιηµένοι

αριθµοί. Θα πρέπει να σηµειωθεί ότι το

2550 << e )1(2)1( 127 fx es +−= −

f+1 αντιστοιχεί στη δυαδική λέξη 1 .

Για κανονικοποιηµένους αριθµούς, ο εκθέτης επιλέγεται έτσι ώστε να µεταφέρεται το 1 που βρίσκεται στη πρώτη θέση από αριστερά, στη πρώτη θέση αριστερά της υποδιαστολής. Εφόσον τώρα η ύπαρξη του 1 είναι γνωστή, αυτό δε περιλαµβάνεται στο πεδίο επιτρέποντας έτσι την ύπαρξη ενός έξτρα bit ακρίβειας για τη mantissa.

231. ff …

f

4. Εάν και , τότε . Αυτοί είναι οι µη κανονικοποιηµένοι

αριθµοί.

0=e 0≠f fx s 1262)1( −−=

5. Εάν και , τότε . Θα πρέπει να σηµειωθεί ότι ορίζεται τόσο

θετικό όσο και αρνητικό 0.

0=e 0=f 0)1( ×−= sx

Η µορφή ενός αριθµού κινητής υποδιαστολής διπλής ακρίβειας είναι 63 62 52 51 0

s 0910 ,,, eee … 525121 ,,,, ffff …

Τα πεδία είναι αντίστοιχα αυτών την µονής ακρίβειας :

28

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

• Το πεδίο µήκους ενός bit είναι το bit προσήµου. Εάν s 0=s οι αριθµοί είναι θετικοί,

ενώ εάν είναι αρνητικοί. 1=s• Το πεδίο µήκους 11 bit είναι ο πολωµένος εκθέτης που έχει τη δεκαδική

τιµή , έτσι ώστε

0910 ,,, eee …

∑=

=10

02

k

kkee 20470 ≤≤ e . Ο πολωµένος εκθέτης ενος

κανονικοποιηµένου αριθµού δε µπορεί να έχει τις τιµές 0 και 2047. Η τιµή είναι δεσµευµένη για αριθµούς που είναι ίσοι µε το 0. Η τιµή

0=e2047=e είναι δεσµευµένη για

την αναπαράσταση απείρου και NaN.

• Το πεδίο µήκους 52 bit ονοµάζεται mantissa ή δεκαδικό µέρος και

έχει την ισοδύναµη δεκαδική τιµή , που αντιστοιχεί στη δυαδική λέξη

. Η mantissa έχει εύρος [

525121 ,,,, ffff …

52f

∑=

−=52

12

k

kkff

]21,0 52−−21.0 ff … Η αριθµητική τιµή, x , της λέξης µονής ακρίβειας, κινητής υποδιαστολής καθορίζεται από τους ακόλουθους κανόνες:

1. Εάν e και , τότε το 2047= 0≠f x είναι ΝaN, ανεξάρτητο από το s

2. Εάν e και , τότε 2047= 0=f ( ) ∞−= sx 1

3. Εάν τότε . Αυτοί είναι οι κανονικοποιηµένοι

αριθµοί. Θα πρέπει να σηµειωθεί ότι το

20470 << e )1(2)1( 1023 fx es +−= −

f+1 αντιστοιχεί στη δυαδική λέξη 1 .

Για κανονικοποιηµένους αριθµούς, ο εκθέτης επιλέγεται έτσι ώστε να µεταφέρεται το 1 που βρίσκεται στη πρώτη θέση από αριστερά, στη πρώτη θέση αριστερά της υποδιαστολής. Εφόσον τώρα η ύπαρξη του 1 είναι γνωστή, αυτό δε περιλαµβάνεται στο πεδίο επιτρέποντας έτσι την ύπαρξη ενός έξτρα bit ακρίβειας για τη mantissa.

521. ff …

f

4. Εάν και , τότε . Αυτοί είναι οι µη κανονικοποιηµένοι

αριθµοί.

0=e 0≠f fx s 10222)1( −−=

5. Εάν και , τότε . Θα πρέπει να σηµειωθεί ότι ορίζεται τόσο

θετικό όσο και αρνητικό 0.

0=e 0=f 0)1( ×−= sx

Στον C6711 οι αριθµοι κινητικής υποδιαστολής, µονής ακρίβειας αποθηκεύονται σε ένα καταχωρητή, ενώ οι αντίστοιχοι διπλής ακρίβειας αποθηκεύονται σε ένα ζεύγος γειτονικών καταχωρητών. Τα 32 λιγότερα σηµαντικά bits τοποθετούνται σε έναν καταχωτητή µε ζυγή αρίθµηση, ενώ τα 32 πιο σηµαντικά ψηφία τοποθετούνται στον αµέσως υψηλότερο, σε αρίθµηση, καταχωρητή. Γι’ αυτό, ο άρτια αριθµηµένος καταχωρητής περιέχει τα 32 λιγότερα

29

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

σηµαντικά bits της mantissa, ενώ ο περιττά αριθµηµένος καταχωρητής περιέχει τα 20 περισσότερο σηµαντικότερα bits της mantissa, τα 11 ψηφία του πολωµένου εκθέτη και το bit προσήµου.

2.6 Περιγραφή του Enhanced Direct Memory Access (EDMA) Controller Ο EDMA ελεγκτής διαχειρίζεται όλες τις µεταφορές δεδοµένων µεταξύ του L2 cache/memory ελεγκτή και των περιφεριακών συσκευών που υπάρχουν στο ολοκληρωµένο του επεξεργαστή. Αυτές οι µεταφορές δεδοµένων περιλαµβάνουν εξυπηρετήσεις cache, non-cacheable προσβάσεις στη µνήµη, προγραµµατιζόµενες από το χρήστη µεταφορές και προσβάσεις από τον host. Ο EDMA έχει εµπλουτιστεί µε χαρακτηριστικά που τον κάνουν περισσότερο αποδοτικό από τον DMA, όπως ότι διαθέτει 16 κανάλια µε προγραµµατιζόµενη προτεραιότητα και την ικανότητα να συνδέει και να οµαδοποιεί τις µεταφορές δεδοµένων. Ο EDMA επιτρέπει µεταφορά δεδοµένων προς/από οποιοδήποτε διευθυνσιοδοτούµενο χώρο µνήµης συµπεριλαµβανοµένης της L2 SRAM, των περιφερειακών και της εξωτερικής µνήµης. Ο EDMA ελεγκτής αποτελείται από:

• Καταχωρητές γεγονότων και διακοπών επεξεργασίας (Event registers, interrupt processing registers) • Κωδικοποιητή γεγονότων (event encoder) • Parameter RAM (PaRAM) • Υλικό παραγωγής διευθύνσεων (Address generation hardware)

Παρακάτω παρατίθεται το αναλυτικό block διάγραµµα του EDMA ελεγκτή:

30

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Σχήµα 2.3 : Σχηµατικό διάγραµµα του ελεγκτή EDMA Τα EDMA γεγονότα συλλέγονται στον καταχωρητή γεγονότων (event register). Ένα γεγονός είναι ουσιαστικά ένα σήµα συγχρονισµού το οποίο ενεργοποιεί ένα κανάλι EDMA για να αρχίσει τη µεταφορά. Εάν τα γεγονότα συµβούν ταυτόχρονα, τότε, τη σύγκρουση διευθετεί ο κωδικοποιητής γεγονότων (event encoder). Οι παράµετροι αναφοράς που αντιστοιχούν σε κάθε γεγονός αποθηκεύονται στην EDMA parameter RAM και στη συνέχεια περνούν δια µέσου του address generation hardware, ο οποίος διευθυνσιοδοτεί την EMIF και/ή τα περιφερειακά για να πραγµατοποιηθούν οι αναγκαίες διεκπεραιώσεις εγγραφής και ανάγνωσης. Ο EDMA έχει την ικανότητα να πραγµατοποιεί γρήγορες και αποδοτικές µεταφορές µε το να δέχεται µια αίτηση quick DMA (QDMA) από τη CPU. Η QDMA µεταφορά χρησιµοποιείται καλύτερα σε εφαρµογές που απαιτούν γρήγορες µεταφορές δεδοµένων όπως αιτήσεις δεδοµένων σε έναν µικρό loop αλγόριθµο.

2.6.1 Ορολογία για τον EDMA Στη συνέχεια ακολουθούν κάποιοι ορισµοί όρων που θα βοηθήσουν στην περαιτέρω κατανόηση του κειµένου:

31

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Μεταφορά στοιχείου (Element transfer) Η µεταφορά ενός απλού στοιχείου δεδοµένου από την πηγή στον προορισµό. Κάθε στοιχείο, εάν απαιτείται, µπορεί να µεταφερθεί µε βάση το γεγονός συγχρονισµού. Ο όρος “element transfer” χρησιµοποιείται σε συνδυασµό µε την µονοδιάστατη µεταφορά που θα περιγραφεί παρακάτω. Πλαίσιο (Frame) Μία οµάδα από στοιχεία (elements) αποτελεί ένα frame. Τα στοιχεία αυτά µπορούν να είναι είτε σε συνεχόµενες διευθύνσεις είτε όχι. Ένα frame µπορεί να µεταφερθεί µε ή χωρίς τη βοήθεια ενός γεγονότος συγχρονισµού. Ο όρος frame χρησιµοποιείται και αυτός σε συνδυασµό µε την µονοδιάστατη µεταφορά που θα περιγραφεί παρακάτω. Πίνακας (Array) Ένα σύνολο από συνεχόµενα στοιχεία αποτελεί ένα πίνακα. Ο όρος “array” χρησιµοποιείται σε συνδυασµό µε τις δισδιάστατες µεταφορές που και σε αυτές θα αναφερθούν παρακάτω. Block Ένα σύνολο από πίνακες ή πλαίσια αποτελούν ένα block. Για µονοδιάστατες µεταφορές ένα σύνολο από πλαίσια σχηµατίζουν ένα block, ενώ για δισδιάστατες µεταφορές ένα σύνολο από πίνακες σχηµατίζουν ένα block. Μονοδιάστατη µεταφορά (1-D transfer) Ένα σύνολο από πλαίσια, όπως είπαµε, αποτελούν ένα µονοδιάστατο (1-D) block. Ο αριθµός των πλαισίων µέσα στο block (που καθορίζονται από το πεδίο FRMCNT) παίρνει τιµή µεταξύ 1 και 65536. Ο αριθµός των στοιχείων για κάθε πλαίσιο µπορεί να είναι µεταξύ 1 και 65536. Κάθε φορά µεταφέρονται είτε στοιχεία του frame είτε ολόκληρο το frame. ∆ισδιάστατη µεταφορά (2-D transfer) Ένα σύνολο από πίνακες αποτελούν ένα δισδιάστατο (2-D) block. Η πρώτη διάσταση αντιπροσωπεύει τον αριθµό των συνεχόµενων στοιχείων στο πίνακα και η δεύτερη διάσταση εκφράζει τον αριθµό του αντίστοιχου πίνακα. Ο αριθµός των πινάκων σε ένα block (καθορίζεται από το πεδίο FRMCNT) κυµαίνεται µεταξύ 1 και 65536. Κάθε φορά µεταφέρονται είτε κάποιοι πίνακες είτε ολόκληρο το block.

32

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

2.6.2 Καταχωρητές Ελέγχου και Επεξεργασία Γεγονότων Καθένα από τα 16 κανάλια του EDMA έχει ένα συγκεκριµένο γεγονός συχγρονισµού που σχετίζεται µ’ αυτό. Τα γεγονότα αυτά ενεργοποιούν µία µεταφορά δεδοµένων. Παρατίθεται η λίστα µε τους καταχωρητές ελέγχου που επεξεργάζονται τα διάφορα γεγονότα :

Σχήµα 2.4 : Καταχωρητές Ελέγχου EDMA

Εκτός από τον καταχωρητή γεγονότων , ο ελεγκτής EDMA παρέχει τη δυνατότητα στο χρήστη να ενεργοποιεί και να απενεργοποιεί γεγονότα. Οποιαδήποτε από τα 16 bits γεγονότων του 32-bit EER µπορεί να τεθεί στο 1 για να ενεργοποιήσει το ανάλογο γεγονός, όπως φαίνεται παρακάτω :

EER

Όλα τα γεγονότα, ακόµα κι αν είναι απενεργοποιηµένα, εντοπίζονται από τον ER καταχωρητή.

ER

33

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Για να γίνει clear ένα γεγονός από αυτόν, µπορούν να χρησιµοποιηθούν δύο τρόποι. Αν το γεγονός έχει ενεργοποιηθεί στον EER, το αντίστοιχο bit του γεγονότος στον ER θα πρέπει να τεθεί (clear) µόλις η EDMA επικυρώσει µια αίτηση µετάδοσης από αυτό. Εναλλακτικά, αν το γεγονός έχει απενεργοποιηθεί στον EER, η CPU µπορεί να καθαρίσει το γεγονός µέσω του ECR :

ECR

Τοποθετώντας 1 σε οποιοδήποτε από τα bits του, απενεργοποιείται το αντίστοιχο γεγονός ενώ µε 0 δε συµβαίνει τίποτα. Η παραπάνω δυνατότητα επιτρέπει στη CPU να απεµπλακεί σε περίπτωση λάθους ή κωλύµατος. Η CPU µπορεί, επίσης, να θέσει γεγονότα µέσω του ESR, η δοµή του οποίου είναι η ακόλουθη :

ESR

Θέτοντας 1 σε κάποιο από τα 16 bits του, τίθεται στο 1 το αντίστοιχο bit του ER. Πρόκειται για ένα καλό εργαλείο εκσφαλµάτωσης που επιτρέπει στη CPU να επικυρώσει EDMA αιτήσεις στο σύστηµα. Οι µεταφορές αυτές, βέβαια, είναι µη συγχρονισµένες.

2.6.3 Κωδικοποιητής Γεγονότων Αναλαµβάνει τη διευθέτηση της σειράς επεξεργασίας γεγονότων που συµβαίνουν ταυτόχρονα. Ο µηχανισµός αυτός ταξινοµεί τα ταυτόχρονα γεγονότα και δεν ασχολείται µε την προτεραιότητά τους. Η πραγµατική προτεραιότητα µιας µεταφοράς καθορίζεται από τις παραµέτρους EDMA που αποθηκεύονται στη PaRAM του EDMA ελεγκτή.

34

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

2.6.4 Μνήµη RAM παραµέτρων (PaRAM) Ο ελεγκτής EDMA είναι σχεδιασµένος µε βάση µια αρχιτεκτονική RAM. Η PaRAM χρησιµοποιείται για την αποθήκευση των παραµέτρων που ορίζει µια µεταφορά EDMA. Έχει µέγεθος 2ΚΒ και χρησιµοποιείται για τις παραµέτρους και των 16 γεγονότων. Όταν εντοπιστεί ένα γεγονός, οι παράµετροί του διαβάζονται από µία από τις 16 κορυφαίες εγγραφές (top entries) της PaRAM. Έπειτα, στέλνονται στο υλικό παραγωγής διεύθυνσης. Η µνήµη αυτή, όπως φαίνεται στον Πίνακα 2.5 αποτελείται από :

• 16 εγγραφές παραµέτρων µετάδοσης(parameter entries) για τα 16 EDMA γεγονότα. Κάθε είσοδος είναι έξι λέξεων ή 24Β, συνολικά 384Β. Το εύρος διευθύνσεων είναι από 01A0 0000h έως 01A0 017Fh.

• 69 σύνολα παραµέτρων µετάδοσης που χρησιµοποιούνται για τη σύνδεση των γεγονότων. Κάθε σύνολο είναι µεγέθους 24Β, και σε σύνολο 1656Β. Το εύρος διευθύνσεων είναι από 01A0 0180h έως 01A0 07F7h.

• 8Β αχρησιµοποίητης µνήµης που µπορούν να χρησιµοποιηθούν ως scratch pad area. Το εύρος διευθύνσεων είναι από 01A0 07F8h έως 01A0 07FFh.

35

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

36

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Πίνακας 2.1 : Περιεχόµενα PaRAM

2.6.5 EDMA Παράµετροι Μεταφοράς Κάθε εγγραφή παραµέτρου οργανώνεται σε έξι λέξεις των 32-bit συνολικά δηλαδή 192 bits(Σχηµα 2.6). Η πρόσβαση σε αυτές γίνεται µόνο µέσω του περιφερειακού διαύλου των 32-bit, οπως

37

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Σχήµα 2.5 : Πεδία Παραµέτρου της PaRAM

2.6.5.1 Παράµετρος Επιλογών (OPT) Το options parameter (OPT) είναι ένα πεδίο των 32-bit το οποίο καθορίζει πλήρως τον τρόπο µε τον οποίο πρόκειται να γίνει η µεταφορά δεδοµένων. Με βάση τις τιµές του συγκεκριµένου πεδίου προσδιορίζονται όλα εκείνα τα χαρακτηριστικά που απαιτούνται για να ρυθµιστεί ο τρόπος εκτέλεσης και επεξεργασίας των γεγονότων (events). Για παράδειγµα, προσδιορίζει τα επίπεδα προτεραιότητας των EDMA events(PRI), το µέγεθος των στοιχείων (ESIZE), τη διάσταση της πηγής και του προορισµού αντίστοιχα(2DS, 2DD), τον τρόπο συγχρονισµού των frames(FS) και άλλα χαρακτηριστικα που παρουσιάζονται στην µορφή των πεδίων του options parameter που φαινεται στο Σχηµα 2.7.

38

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

39

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

Σχήµα 2.6 : Παράµετρος ΟPT

2.6.5.2 ∆ιεύθυνση Πηγής / Προορισµου (SRC/DST) To πεδίο των 32-bit που καθορίζει τις διευθύνσεις της πηγής και του προορισµού περιέχει την αρχική διεύθυνση για τη πηγή και τον προορισµό αντίστοιχα. Οι διευθύνσεις SRC/DST µπορούν να τροποποιηθούν χρησιµοποιώντας τις τιµές των πεδίων SUM και DUM που περιέχονται στις παραµέτρους επιλογής (options parameter) (δες Σχηµα 2.6).

40

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711

2.6.5.3 Μετρητής Στοιχείων (ELECNT) Πρόκειται για µια 16-bit µη προσηµασµένη τιµή που καθορίζει τον αριθµό των στοιχείων σ’ένα πλαισιο (frame) (για µονοδιάστατες µεταφορές) ή σ’ένα πίνακα (array) (για δισδιάστατες µεταφορές). Αποδεκτή είναι οποιαδήποτε τιµή µεταξύ 1 και 65535. Συνεπώς, ο µέγιστος αριθµός στοιχείων σ’ένα πλαίσιο είναι 65535. Αν ELECNT=0, δεν εκτελούνται µεταφορές.

2.6.5.4 Μετρητής Πλαισίου / Πίνακα (FRMCNT) Πρόκειται, επίσης, για µια 16-bit µη προσηµασµένη τιµή που καθορίζει τον αριθµό των πλαισίων σ’ένα 1-D block ή τον αριθµό των πινάκων σ’ένα 2-D block. O µέγιστος αριθµός των πλαισίων / πινάκων σ’ένα block είναι 65536.

2.6.5.5 Περιεχόµενα ∆είκτη στοιχείου / ∆είκτη πλαισίου (ELEIDX / FRMIDX) Οι 16-bit προσηµασµένες τιµές των πεδίων αυτών χρησιµοποιούνται για την τροποποίηση διευθύνσεων. Πιο συγκεκριµένα χρησιµοποιούνται από τον EDMA για να ανανεώσουν τη διεύθυνση ανάλογα µε τον τύπο της µεταφοράς που έχει επιλεχθεί (1-D ή 2-D), τη τιµή του πεδίου FS καθώς και των SUM/DUM πεδίων. Ο όρος ‘frame index’ αντιστοιχεί σε 1-D µεταφορές, ενώ ο όρος ‘array index’ αντιστοιχεί σε 2-D µεταφορές. Οι SRC/DST διευθύνσεις τροποποιούνται από ένα δείκτη του οποίου η τιµή κυµαίνεται µεταξύ –32768 και 32767. Το element index καθορίζει ένα offset διεύθυνσης για το επόµενο στοιχείο µέσα στο ίδιο frame και χρησιµοποιείται µόνο για 1-D µεταφορές. Αυτό συµβαίνει γιατί οι 2-D µεταφορές δεν επιτρέπουν να υπάρχει χώρος µεταξύ δύο στοιχείων και έτσι ο όρος ‘array’ χρησιµοποιείται για να ορίσει ένα σύνολο από συνεχόµενα στοιχεία. To frame/array index µε τη σειρά του καθορίζει ένα offset για το επόµενο frame/array µέσα στο ίδιο block. 2.6.5.6 Επαναφόρτωση Μετρητή Στοιχείου (ELERLD) Στο πεδίο αυτό οι 16-bit µη προσηµασµένες τιµές χρησιµοποιούνται για να φορτωθεί εκ νέου η τιµή του ELECNT µόλις η µεταφορά και του τελευταίου στοιχείου ολοκληρωθεί. Το element count reload χρησιµοποιείται µόνο για µονοδιάστατες µεταφορές που είναι element synchronized (FS = 0) µιας και ο EDMA πρέπει να κρατήσει πληροφορία για τη διεύθυνση του επόµενου στοιχείου χρησιµοποιώντας την τιµή του πεδίου ΕLECNT. Αυτή η ενέργεια είναι απαραίτητη για multi-frame EDMA µεταφορές, όπου η τιµή του FRMCNT είναι θετική.

41

Κεφάλαιο 2 – Ο επεξεργαστής TMS320C6711