ΠΑΡΑΔΟΣΕΙΣ ΜΑΘΗΜΑΤΟΣ «ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΕΣ 1» ΕΣΩΤΕΡΙΚΗ...

description

Transcript of ΠΑΡΑΔΟΣΕΙΣ ΜΑΘΗΜΑΤΟΣ «ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΕΣ 1» ΕΣΩΤΕΡΙΚΗ...

ΠΑΡΑΔΟΣΕΙΣ ΜΑΘΗΜΑΤΟΣΠΑΡΑΔΟΣΕΙΣ ΜΑΘΗΜΑΤΟΣ

«ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΕΣ 1» «ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΕΣ 1»

ΕΣΩΤΕΡΙΚΗΕΣΩΤΕΡΙΚΗ

ΑΡΧΙΤΕΚΤΟΝΙΚΗ ΑΡΧΙΤΕΚΤΟΝΙΚΗ ΚΑΙ ΛΕΙΤΟΥΡΓΙΕΣΚΑΙ ΛΕΙΤΟΥΡΓΙΕΣ

80858085

ΟΚΤΩΒΡΙΟΣ 2005ΟΚΤΩΒΡΙΟΣ 2005

ΧΟΝΔΡΙΚΟ ΔΙΑΓΡΑΜΜΑ ΧΟΝΔΡΙΚΟ ΔΙΑΓΡΑΜΜΑ 8085 8085 CPU CPU

ΟΙ ΚΑΤΑΧΩΡΗΤΕΣ ΤΟΥ 8085ΟΙ ΚΑΤΑΧΩΡΗΤΕΣ ΤΟΥ 8085

Ο ΑΠΟΚΩΔΙΚΟΠΟΙΗΤΗΣ ΕΝΤΟΛΩΝΟ ΑΠΟΚΩΔΙΚΟΠΟΙΗΤΗΣ ΕΝΤΟΛΩΝ

Η ΑΡΙΘΜΗΤΙΚΗ ΚΑΙ ΛΟΓΙΚΗ ΜΟΝΑΔΑΗ ΑΡΙΘΜΗΤΙΚΗ ΚΑΙ ΛΟΓΙΚΗ ΜΟΝΑΔΑ

ΟΙ «ΣΗΜΑΙΕΣ» ΟΙ «ΣΗΜΑΙΕΣ» FLAGS FLAGS

Η ΜΟΝΑΔΑ ΧΡΟΝΙΣΜΟΥ ΚΑΙ ΕΛΕΓΧΟΥΗ ΜΟΝΑΔΑ ΧΡΟΝΙΣΜΟΥ ΚΑΙ ΕΛΕΓΧΟΥ

TO TO ΥΠΟΣΥΣΤΗΜΑ ΔΙΑΚΟΠΩΝΥΠΟΣΥΣΤΗΜΑ ΔΙΑΚΟΠΩΝ

ΣΕΙΡΙΑΚΗ ΕΙΣΟΔΟΣ / ΕΞΟΔΟΣΣΕΙΡΙΑΚΗ ΕΙΣΟΔΟΣ / ΕΞΟΔΟΣ

ΧΟΝΔΡΙΚΟ ΔΙΑΓΡΑΜΜΑ ΧΟΝΔΡΙΚΟ ΔΙΑΓΡΑΜΜΑ ((BLOCK DIAGRAM)BLOCK DIAGRAM)

80858085 CPUCPU

ΛΕΠΤΟΜΕΡΕΣ ΔΙΑΓΡΑΜΜΑ ΑΡΧΙΤΕΚΤΟΝΙΚΗΣ 8085ΛΕΠΤΟΜΕΡΕΣ ΔΙΑΓΡΑΜΜΑ ΑΡΧΙΤΕΚΤΟΝΙΚΗΣ 8085

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

ΚΑΤΑΧΩΡΗΤΕΣ ΚΑΤΑΧΩΡΗΤΕΣ

((REGISTERS)REGISTERS)

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

ΚΑΤΑΧΩΡΗΤΕΣ (ΚΑΤΑΧΩΡΗΤΕΣ (REGISTERS)REGISTERS) 8085 8085

Ο Ο ΣΥΣΣΩΡΕΥΤΗΣ ΣΥΣΣΩΡΕΥΤΗΣ

( ACCUMULATOR - A )( ACCUMULATOR - A )

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Συσσωρευτής (Accumulator)- Ο βασικότερος καταχωρητής της CPU- Εχει εύρος 8-bit- Αποθηκεύει έναν απο τους τελεστέους (operands) που επεξεργάζεται η ΑΛΜ (ALU)- Λειτουργεί και σαν πηγή (source) και σαν προορισμός (destination)- Εκεί αποθηκεύεται το αποτέλεσμα της πράξης της ΑΛΜ

πχ. MVI A,0FFH / LDA 2020H / STA 2030H / ADD B

ORGORG 20002000HH ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) STARTSTART:: ;δήλωση αρχής εντολών προγράμματος (ψευδοεντολή);δήλωση αρχής εντολών προγράμματος (ψευδοεντολή)LXI HLXI H,2030,2030HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2030) ως δείκτης στην 2030HH MVI AMVI A,0,0FF11HH ;μεταφορά του ;μεταφορά του FF11HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M,,AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL LXI HLXI H,2031,2031HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2031) ως δείκτης στην 2031HHMVI AMVI A,0,0AA22HH ;μεταφορά του ;μεταφορά του AA22HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M, , AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL ADIADI 00 00HH ;μηδενισμός του ;μηδενισμός του flag carry flag carry LDALDA 2030 2030HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030HH MVI BMVI B,84,84HH ;μεταφορά του 84;μεταφορά του 84HH στον καταχωρητή στον καταχωρητή BBADD BADD B ;;A A = = AA + + BBSTASTA 2040 2040HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2040 (αποτελέσματος) στην θέση μνήμης 2040HHLDALDA 2031 2031HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031HHMVI BMVI B,12,12HH ;μεταφορά του 12;μεταφορά του 12HH στον καταχωρητή στον καταχωρητή BBADC BADC B ;;A A = = AA + + BB + + CCSTASTA 2041 2041HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2041 (αποτελέσματος) στην θέση μνήμης 2041HHENDEND ;δήλωση τέλους εντολών προγράμματος (ψευδοεντολή);δήλωση τέλους εντολών προγράμματος (ψευδοεντολή)

Η ΧΡΗΣΗ ΤΟΥ ΚΑΤΑΧΩΡΗΤΗ Α ΣΕ ΠΡΟΓΡΑΜΜΑΗ ΧΡΗΣΗ ΤΟΥ ΚΑΤΑΧΩΡΗΤΗ Α ΣΕ ΠΡΟΓΡΑΜΜΑ

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Προσωρινοί Καταχωρητές (Temporary Registers)- Εχει εύρος 8-bit- Αποθηκεύει έναν απο τους τελεστέους (operands) που επεξεργάζεται η ΑΛΜ (ALU)- Δεν είναι προσπελάσιμος στον προγραμματιστή

πχ. ADD Μ / ADC M / ADI FF

ORGORG 20002000HH ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) STARTSTART:: ;δήλωση αρχής εντολών προγράμματος (ψευδοεντολή);δήλωση αρχής εντολών προγράμματος (ψευδοεντολή)LXI HLXI H,2030,2030HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2030) ως δείκτης στην 2030HH MVI AMVI A,0,0FF11HH ;μεταφορά του ;μεταφορά του FF11HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M,,AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL LXI HLXI H,2031,2031HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2031) ως δείκτης στην 2031HHMVI AMVI A,0,0AA22HH ;μεταφορά του ;μεταφορά του AA22HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M, , AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL ADIADI 00 00HH ;μηδενισμός του ;μηδενισμός του flag carry flag carry LDALDA 2030 2030HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030HH MVI BMVI B,84,84HH ;μεταφορά του 84;μεταφορά του 84HH στον καταχωρητή στον καταχωρητή BBADD BADD B ;;A A = = AA + + BBSTASTA 2040 2040HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2040 (αποτελέσματος) στην θέση μνήμης 2040HHLDALDA 2031 2031HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031HHMVI BMVI B,12,12HH ;μεταφορά του 12;μεταφορά του 12HH στον καταχωρητή στον καταχωρητή BBADC BADC B ;;A A = = AA + + BB + + CCSTASTA 2041 2041HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2041 (αποτελέσματος) στην θέση μνήμης 2041HHENDEND ;δήλωση τέλους εντολών προγράμματος (ψευδοεντολή);δήλωση τέλους εντολών προγράμματος (ψευδοεντολή)

Η ΧΡΗΣΗ ΤΟΥ ΚΑΤΑΧΩΡΗΤΗ Η ΧΡΗΣΗ ΤΟΥ ΚΑΤΑΧΩΡΗΤΗ “TEMP. REG.”“TEMP. REG.”

Ο Ο ΚΑΤΑΧΩΡΗΤΗΣ ΣΗΜΑΙΩΝΚΑΤΑΧΩΡΗΤΗΣ ΣΗΜΑΙΩΝ

(( FLAG REGISTER) FLAG REGISTER)

& &

ΟΙ ΟΙ “ “ΣΗΜΑΙΕΣΣΗΜΑΙΕΣ”” ((FLAGS)FLAGS)

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

D7 D6 D5 D4 D3 D2 D1 D0

S Z AC P CY

Καταχωρητής Σημαιών (Flag Register)- Εχει εύρος 8-bit. Περιέχει πέντε (5) flags του 1- bit- Καταγράφει την κατάσταση της CPU και μπορεί να ελέγχει την κατάσταση

- Carry CY (κρατούμενο) D0- Zero Flag Z (μηδενισμός) D6- Auxiliary Carry Flag AC (βοηθητικό κρατούμενο) D4- Sign Flag S (Πρόσημο) D7- Parity Flag P (Ισοτιμία) D2

Carry CY (κρατούμενο) D0- Τίθεται και μηδενίζεται απο αριθμητικές πράξεις- Τίθεται (CY = 1) όταν η πρόσθεση στην ΑΛΜ παράγει αποτέλεσμα > 8-bit (υπερχείλιση Α)- Μηδενίζεται (CY = 0) όταν η πρόσθεση στην ΑΛΜ δεν προκαλεί υπερχείλιση του Α- Λειτουργεί σαν “Borrow” στην αφαίρεση- Επηρεάζεται απο την Σύγκριση αριθμών (Compare - CMP)- Τίθεται απο την STC / Αντιστρέφεται απο την CMC

Auxiliary Carry AC (Βοηθητικό κρατούμενο) D4- Λειτουργεί όπως το CY αλλα για τα τέσσερα χαμηλά bits (bit-3)- Δείχνει υπερχείλιση στο bit-3 (χαμηλό nibble)- Χρησιμοποιείται στην BCD αριθμητική

Sign S (Πρόσημο) D7- Λειτουργεί σε προσημασμένους αριθμούς (7 bit για τιμή & 1 bit για πρόσημο)- Επιτρέπει χρήση αριθμών απο -128 έως + 127- Οταν S = 1 αρνητικός / S = 0 θετικός πχ. 1111 1111 = - 128, 0111 1111 = + 127

Zero Z (Μηδενισμός) D6- Τίθεται (Ζ = 1) όταν παράγεται μηδενισμός (0000 0000) στον Α ή σε καταχωρητές - μετρητές- Αλλοιώς Ζ = 0

Parity P (Ισοτιμία) D2- Τίθεται (Ρ = 1) όταν ο αριθμός των 1-bits του Α είναι άρτιος- Μηδενίζεται (Ρ = 0) όταν ο αριθμός των 1-bits του Α είναι περιττός

D7 D6 D5 D4 D3 D2 D1 D0

S Z AC P CY

ORGORG 20002000HH ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) STARTSTART:: ;δήλωση αρχής εντολών προγράμματος (ψευδοεντολή);δήλωση αρχής εντολών προγράμματος (ψευδοεντολή)LXI HLXI H,2030,2030HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2030) ως δείκτης στην 2030HH MVI AMVI A,0,0FF11HH ;μεταφορά του ;μεταφορά του FF11HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M,,AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL LXI HLXI H,2031,2031HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2031) ως δείκτης στην 2031HHMVI AMVI A,0,0AA22HH ;μεταφορά του ;μεταφορά του AA22HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M, , AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL

ADIADI 00 00HH ;μηδενισμός του ;μηδενισμός του flag carry flag carry LDALDA 2030 2030HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030HH MVI BMVI B,84,84HH ;μεταφορά του 84;μεταφορά του 84HH στον καταχωρητή στον καταχωρητή BBADD BADD B ;;A A = = AA + + BBSTASTA 2040 2040HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2040 (αποτελέσματος) στην θέση μνήμης 2040HHLDALDA 2031 2031HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031HHMVI BMVI B,12,12HH ;μεταφορά του 12;μεταφορά του 12HH στον καταχωρητή στον καταχωρητή BB

ADC BADC B ;;A A = = AA + + BB + + CCSTASTA 2041 2041HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2041 (αποτελέσματος) στην θέση μνήμης 2041HHENDEND ;δήλωση τέλους εντολών προγράμματος (ψευδοεντολή);δήλωση τέλους εντολών προγράμματος (ψευδοεντολή)

Ο ΜΗΔΕΝΙΣΜΟΣ ΤΟΥ Ο ΜΗΔΕΝΙΣΜΟΣ ΤΟΥ “CY (D0)” “CY (D0)” ΣΤΟΝ ΚΑΤΑΧΩΡΗΤΗ ΣΤΟΝ ΚΑΤΑΧΩΡΗΤΗ “FLAG REG.”“FLAG REG.”

Η ΧΡΗΣΗ ΤΟΥ Η ΧΡΗΣΗ ΤΟΥ “CY (D0)” “CY (D0)” ΣΤΗΝ ΠΡΟΣΘΕΣΗΣΤΗΝ ΠΡΟΣΘΕΣΗ

ΆΛΛΕΣ ΕΝΤΟΛΕΣ ΠΟΥ ΑΦΟΡΟΥΝ ΤΙΣ ΣΗΜΑΙΕΣ ΆΛΛΕΣ ΕΝΤΟΛΕΣ ΠΟΥ ΑΦΟΡΟΥΝ ΤΙΣ ΣΗΜΑΙΕΣ

CMC:CMC: complement carry ( complement carry (αντέστρεψε το κρατούμενο)αντέστρεψε το κρατούμενο)

STC:STC: set carry set carry ( (θεσε το κρατούμενο) θεσε το κρατούμενο) CY = 1CY = 1

JC :JC : jump on carry CY=1 ( jump on carry CY=1 (διακλάδωσε αν το κρατούμενο είναι 1)διακλάδωσε αν το κρατούμενο είναι 1)

JNC:JNC: jump on carry CY=0 ( jump on carry CY=0 (διακλάδωσε αν το κρατούμενο είναι 0)διακλάδωσε αν το κρατούμενο είναι 0)

JZ :JZ : jump on zero Z=1 ( jump on zero Z=1 (διακλάδωσε αν συνέβη μηδενισμός ή ισότητα)διακλάδωσε αν συνέβη μηδενισμός ή ισότητα)

JNZ :JNZ : jump on zero Z=0 ( jump on zero Z=0 (διακλάδωσε αν ΔΕΝ συνέβη μηδενισμός ή ισότητα)διακλάδωσε αν ΔΕΝ συνέβη μηδενισμός ή ισότητα)

…………………………………… ……………………………………..

ΑΛΛΟΙ ΑΛΛΟΙ

ΒΟΗΘΗΤΙΚΟΙ ΚΑΤΑΧΩΡΗΤΕΣΒΟΗΘΗΤΙΚΟΙ ΚΑΤΑΧΩΡΗΤΕΣ

((BB--C C DD--E E HH--L)L)

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Βοηθητικοί Καταχωρητές (Registers)- BC- DE- HL- Address Latch

Καταχωρητής BC- Εχει εύρος 16-bit (BC) ή 2 x 8 - bit (B, C)- Είναι γενικής χρήσης

πχ. MOV A, B / MVI B, F4 / ADD B

Καταχωρητής DE- Εχει εύρος 16-bit (DE) ή 2 x 8 - bit (D, E)- Είναι γενικής χρήσης

πχ. MOV A, D / MVI E, F4 / ADD E

Καταχωρητής HL- Εχει εύρος 16-bit (HL) ή 2 x 8- bit (H, L- Είναι γενικής χρήσης- Χρησιμοποιείται σαν δείκτης δεδομένων και αποθηκεύει διευθυνση

πχ. LXI H,2031H MOV M, A (Μ = 2031)

Ο ΔΕΙΚΤΗΣ ΣΩΡΟΥΟ ΔΕΙΚΤΗΣ ΣΩΡΟΥ

(( STACK POINTER – SP ) STACK POINTER – SP )

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Δείκτης Σωρού (Stack Pointer - SP)

Stack Pointer SP (Δείκτης Στοίβας)- Εχει εύρος 16-bit- Αποθηκεύει Διεύθυνση- Είναι δείκτης της τρέχουσας διεύθυνσης που αντιστοιχεί στην κορυφής της στοίβας- Η στοίβα (Stack) είναι μια δεσμευμένη περιοχή μνήμης RAM- Εκεί αποθηκεύονται προσωρινά δεδομένα (καταχωρητών) όταν συμβαίνει διακοπή ή μετάβαση σε υπορουτίνα- Η Στοίβα έχει δομή LIFO (last in first out)

0000Η

0001Η

0002Η

0003Η

……..

00FFΗ

SP = 00A5H

00A6H

……..

PU

SH

DA

TA INS

TAC

K

PU

LLD

ATA

FRO

MS

TAC

K00A5H

Ο ΑΠΑΡΙΘΜΗΤΗΣ ΠΡΟΓΡΑΜΜΑΤΟΣΟ ΑΠΑΡΙΘΜΗΤΗΣ ΠΡΟΓΡΑΜΜΑΤΟΣ

((PROGRAM COUNTER – PC)PROGRAM COUNTER – PC)

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Απαριθμητής Προγράμματος (Program Counter - PC)

Program Counter PC (Απαριθμητής Προγράμματος)- Εχει εύρος 16-bit- Αποθηκεύει Διεύθυνση- Είναι δείκτης της διεύθυνσης της επόμενης εντολής που πρόκειται να εκτελεστεί- Τροφοδοτεί το Address Bus

(PC = (PC = Διεύθυνση Μνήμης) (Εντολές προγράμματος)Διεύθυνση Μνήμης) (Εντολές προγράμματος)

(2000) MVI A, FFH(2000) MVI A, FFH(2002) STA 2023H(2002) STA 2023H(2005) LDA 2020H(2005) LDA 2020H

…………....………………………………

ORG 2000H ; διεύθυνση πρώτης εντολής (ψευδοεντολή)

START: ;δήλωση αρχής εντολών προγράμματος (ψευδοεντολή)

MVI A,FFH ; μεταφορά του FFH στον καταχωρητή Α

STA 2023H ; αποθήκευση περιεχομένων Α στην ΘΜ 2023Η

LDA 2020H ; φόρτωση περιεχομένων ΘΜ 2020H στον Α

STA 2030H ; αποθήκευση περιεχομένων Α στην ΘΜ 2030Η

END ; δήλωση τέλους εντολών προγράμματος (ψευδοεντολή)

ΚΑΤΑΧΩΡΗΤΗΣ &ΚΑΤΑΧΩΡΗΤΗΣ &ΑΠΟΚΩΔΙΚΟΠΟΙΗΤΗΣ ΑΠΟΚΩΔΙΚΟΠΟΙΗΤΗΣ

ΕΝΤΟΛΩΝΕΝΤΟΛΩΝ

INSTRUCTION INSTRUCTION REGISTER & DECODERREGISTER & DECODER

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Καταχωρητής Εντολής (Instruction Register)- Εχει εύρος 8-bit- Αποθηκεύει τον κωδικό της εντολής προς αποκωδικοποίηση- Συνεργάζεται με τον Αποκωδικοποιητή Εντολών- Δεν είναι προσπελάσιμος στον προγραμματιστή

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Αποκωδικοποιητής Εντολών (Instruction Decoder)- Με βάση το είδος της εντολής καθορίζει τις επόμενες λειτουργίες για την εκτέλεσή της- Καθορίζει τους επόμενους ΚΜ- Ελέγχει το υποσύστημα χρονισμού που παράγει τα σήματα ελέγχου (timing & control)

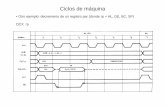

Τ1 Τ2 Τ3 Τ4 Τ1 Τ2 Τ3 Τ1 Τ2 Τ3 Τ1 Τ2 Τ3

CLK

IO/M, S1, S2

A8 - A15

AD0 - AD7

ALE

RD

(0, 1, 1) (0, 1, 0) (0, 1, 0) (0, 0, 1)

20H

Τ1 Τ2

WR

20H 20H

02H 32H 03H 23H 04H 20H

20H

23H “A = C5”

T0

T1

T2

T3

T4

T5

T6

THALT

Twait

Ready

Reset

HALT

OF

OF

HALT

ΛΕΙΤΟΥΡΓΕΙ ΣΤΟΝ ΚΜΛΕΙΤΟΥΡΓΕΙ ΣΤΟΝ ΚΜ (T4) (T4) «ΑΝΑΚΛΗΣΗ ΕΝΤΟΛΗΣ» «ΑΝΑΚΛΗΣΗ ΕΝΤΟΛΗΣ»

ΑΡΙΘΜΗΤΙΚΗ ΑΡΙΘΜΗΤΙΚΗ ΚΑΙ ΚΑΙ

ΛΟΓΙΚΗ ΜΟΝΑΔΑ (ΑΛΜ)ΛΟΓΙΚΗ ΜΟΝΑΔΑ (ΑΛΜ)

ARITHMETIC LOGIC UNIT (ALU)ARITHMETIC LOGIC UNIT (ALU)

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Αριθμητική και Λογική Μονάδα - ΑΛΜ (Arithmetic Logic Unit - ALU)- Εχει εύρος 8-bit- Εκτελεί αριθμητικές (+ -) και λογικές πράξεις (AND, OR, NOT ..)- Χρησιμοποιεί τον Συσσωρευτή και Προσωρινό καταχωρητή ως καταχωρητές εισόδων- Αποθηκεύει το αποτέλεσμα (έξοδο) στον Συσσωρευτή- Οι συνθήκες αποτελέσματος θέτουν ή μηδενίζουν τις σημαίες

ORGORG 20002000HH ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) ;διεύθυνση της πρώτης εντολής (ψευδοεντολή) STARTSTART:: ;δήλωση αρχής εντολών προγράμματος (ψευδοεντολή);δήλωση αρχής εντολών προγράμματος (ψευδοεντολή)LXI HLXI H,2030,2030HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2030) ως δείκτης στην 2030HH MVI AMVI A,0,0FF11HH ;μεταφορά του ;μεταφορά του FF11HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M,,AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL LXI HLXI H,2031,2031HH ;ορισμός του ;ορισμός του MM ( (HLHL) ως δείκτης στην 2031) ως δείκτης στην 2031HHMVI AMVI A,0,0AA22HH ;μεταφορά του ;μεταφορά του AA22HH στον καταχωρητή Α στον καταχωρητή ΑMOV MMOV M, , AA ;μεταφορά του Α στην θέση μνήμης που δείχνει ο ;μεταφορά του Α στην θέση μνήμης που δείχνει ο HH και και LL ADIADI 00 00HH ;μηδενισμός του ;μηδενισμός του flag carry flag carry LDALDA 2030 2030HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2030HH MVI BMVI B,84,84HH ;μεταφορά του 84;μεταφορά του 84HH στον καταχωρητή στον καταχωρητή BBADD BADD B ;;A A = = AA + + BBSTASTA 2040 2040HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2040 (αποτελέσματος) στην θέση μνήμης 2040HHLDALDA 2031 2031HH ;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031;μεταφορά στον Α του περιεχομένου θέσης μνήμης 2031HHMVI BMVI B,12,12HH ;μεταφορά του 12;μεταφορά του 12HH στον καταχωρητή στον καταχωρητή BBADC BADC B ;;A A = = AA + + BB + + CCSTASTA 2041 2041HH ;αποθήκευση του ;αποθήκευση του AA (αποτελέσματος) στην θέση μνήμης 2041 (αποτελέσματος) στην θέση μνήμης 2041HHENDEND ;δήλωση τέλους εντολών προγράμματος (ψευδοεντολή);δήλωση τέλους εντολών προγράμματος (ψευδοεντολή)

ΧΡΗΣΕΙΣ ΤΗΣ «ΑΛΜ» ΣΕ ΕΝΤΟΛΕΣ ΠΡΟΣΘΕΣΗΣΧΡΗΣΕΙΣ ΤΗΣ «ΑΛΜ» ΣΕ ΕΝΤΟΛΕΣ ΠΡΟΣΘΕΣΗΣ

ACI :ACI : A = A + “data” + CYA = A + “data” + CY ADC: ADC: A = A + R + CYA = A + R + CYADD : ADD : A = A + RA = A + R

SBB: SBB: A = A - R - CYA = A - R - CYSBI : SBI : A = A – data - CYA = A – data - CY

ANA: ANA: A = A A = A ANDAND R RANI: ANI: A = A A = A ANDAND “data” “data”

ORA: ORA: A = A A = A OROR R RORI: ORI: A = A A = A OROR “data” “data”

XRA: XRA: A = A A = A XORXOR R RXRI: XRI: A = A A = A ΧΧOROR “data” “data”

ΕΝΤΟΛΕΣ ΥΠΟΣΤΗΡΙΖΟΜΕΝΕΣ ΑΠΌ ΤΗΝ ΑΛΜΕΝΤΟΛΕΣ ΥΠΟΣΤΗΡΙΖΟΜΕΝΕΣ ΑΠΌ ΤΗΝ ΑΛΜ

ΜΟΝΑΔΑ ΜΟΝΑΔΑ ΧΡΟΝΙΣΜΟΥ ΚΑΙ ΧΡΟΝΙΣΜΟΥ ΚΑΙ ΕΛΕΓΧΟΥΕΛΕΓΧΟΥ

TIMING AND CONTROL UNITTIMING AND CONTROL UNIT

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

Μονάδα χρονισμού και ελέγχου (Timing and Control)- Δέχεται εισοδο απο τον Αποκωδικοποιητή Εντολών και τις Σημαίες- Παράγει τα σήματα ελέγχου που εκτελούν τις μικρολειτουργίες (ΚΜ, Τ1, Τ2, κλπ.)

Τ1 Τ2 Τ3 Τ4 Τ1 Τ2 Τ3 Τ1 Τ2 Τ3 Τ1 Τ2 Τ3

CLK

IO/M, S1, S2

A8 - A15

AD0 - AD7

ALE

RD

(0, 1, 1) (0, 1, 0) (0, 1, 0) (0, 0, 1)

20H

Τ1 Τ2

WR

20H 20H

02H 32H 03H 23H 04H 20H

20H

23H “A = C5”

T0

T1

T2

T3

T4

T5

T6

THALT

Twait

Ready

Reset

HALT

OF

OF

HALT

T1 = Μια διεύθυνση μνήμης τοποθετείται στο Address Bus.Παράγεται το ALE για απόπλεξη. Καθορίζεται ο ΚΜ απο IO/M-S0-S1 πχ. Ανάκληση εντολής (OF). Ελέγχεται το HALT.

T2 = Δειγματοληπτούνται οι είσοδοι Ready & Hold. Ο PCαυξάνεται κατα 1 αν ισχύει OF. Ενεργοποιείται ένα απο τασήματα ελέγχου RD, WR, ή INTA.

Twait = Προαιρετική κατάσταση. Δημιουργείται εαν το σήμαReady είναι 0 (αργές μνήμες). Καμμία αλλαγή σε διαύλους.

T3 = Ενα byte εντολής ή δεδομένων μεταφέρεται απο CPU σεΜνήμη ή αντίστροφα. Το όποιο σήμα ελέγχου απενεργοποιείται(τελειώνει).

T4 = Αποκωδικοποιούνται τα περιεχόμενα του καταχωρητήεντολών αποκωδικοποιείται η εντολή.

T5 ή Τ6 = Προαιρετικές καταστάσεις που χρησιμοποιούνται γιατην ολοκλήρωση της εκτέλεσης κάποιων εντολών.

TΗ = Κατάσταση HALT

T0 = Αρχική Κατάσταση μετά απο RESET

T0

T1

T2

T3

T4

T5

T6

THALT

Twait

Ready

Reset

HALT

OF

OF

HALT

ΑΠΟΜΟΝΩΤΕΣ ΔΙΑΥΛΩΝΑΠΟΜΟΝΩΤΕΣ ΔΙΑΥΛΩΝ

( BUFFERS )( BUFFERS )

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

ΥΠΟΣΥΣΤΗΜΑ ΔΙΑΚΟΠΩΝΥΠΟΣΥΣΤΗΜΑ ΔΙΑΚΟΠΩΝ

( INTERRUPTS )( INTERRUPTS )

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND

MEMORY ADDRESSES

TRAP

RST 5.5

RST 6.5

RST 7.5

8085SYSTEM MEMORY

00 Η

08 Η

10 Η

18 Η

20 Η

28 Η

30 Η

38 Η

24 Η

2C Η

34 Η

3C ΗΟ 8085

εκτελεί εντολέςsoftware RST

στη λήψη INTR

RST 0

RST 1

RST 2

RST 3

RST 5

RST 7

RST 4

RST 6

ΣΕΙΡΙΑΚΗ ΕΙΣΟΔΟΣ - ΕΞΟΔΟΣΣΕΙΡΙΑΚΗ ΕΙΣΟΔΟΣ - ΕΞΟΔΟΣ

( SERIAL I / O )( SERIAL I / O )

INSTRUCTIONDECODER

ANDMACHINE

CYCLEENCODING

INTERRUPT CONTROL SERIAL I/O CONTROL

ACCUMULATOR(A REG.) (8 bit)

TEMP. REG.(8 bit)

FLAG REG.(5 bit)

ARITHMETICLOGICUNIT

(ALU)(8 bit)

INSTRUCTIONREGISTER (8 bit)

BREG.

CREG.

DREG.

EREG.

HREG.

LREG.

STACK POINTER

PROGRAM COUNTER

INCREMENTER / DECREMENTERADDRESS LATCH

(8 bit) (8 bit)

(8 bit)

(8 bit)

(8 bit)

(8 bit)

(16 bit)

(16 bit)

(16 bit)

ADDRESS BUFFER (8 bit) DATA / ADDRESS BUFFER (8 bit)TIMING AND CONTROL

INTR

INTA

RST 5.5

RST 6.5

RST 7.5

TRAP

SID SOD

A8 - A15ADDRESS BUS

AD0 - AD7ADDRESS / DATA BUS

X1

X2

CLK OUT

READY

RD WR ALE S0 S1 IO/M

HOLD

HLDA

RESET IN

RESET OUT

REGISTERARRAY

RESET

POWERSUPPLY

+5V

GND